### MULTIPROJEKT CHIP- GRUPPE

BADEN - WÜRTTEMBERG

WORKSHOP FEBRUAR 1993

REUTLINGEN

HERAUSGEBER: FACHHOCHSCHULE ULM

© 1993 Fachhochschule Ulm

Das Werk und seine Teile sind urheberrechtlich geschützt. Jede Verwertung in anderen als den gesetzlich zugelassenen Fällen bedarf deshalb der vorherigen schriftlichen Einwilligung des Herausgebers.

### Inhaltsverzeichnis

- 1. Entwicklung elektronischer Systeme und Schaltkreise mit VHDL

- M. Koch, D. Tavangarian FernUniversität Hagen

- 2. Entwicklung eines Radschlupfprozessors mit der Beschreibungssprache VHDL

- T. Büchner, R. Granzer IMS-Stuttgart

- G. Kampe FH-Esslingen

- 3. Entwurf und Realisierung einer ASIC-basierenden optoelektronischen Busschnittstelle

- Höptner, A. Larsch FH-Karlsruhe

- 4. Baustein zur Datenverschlüsselung

- Führer, P. Jonski FH-Ulm

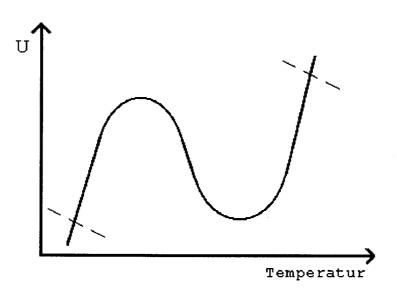

- 5. Entwicklung eines integrierten Temperatur-Spannungsumsetzers mit einstellbarer nichtlinearer Kennlinie in Bipolar-Technik

- G. Albert, S. Christ FH-Mannheim

- 6. Erfahrungen mit der Board-Station von Mentor-Graphics

- E. Mackensen FH-Offenburg

### Entwicklung elektronischer Systeme und Schaltkreise mit VHDL

Djamshid Tavangarian, Michael Koch

FernUniversität Hagen, Technische Informatik II Postfach 940, 5800 Hagen 1 Tel. 02331 987 4412, Fax. 02331 64 373 E-mail: michael.koch@fernuni-hagen.de

### 1 Einleitung

Bei der Entwicklung digitaler hoch- (VLSI) und höchstintegrierter Schaltkreise (ULSI) haben sich die strukturierten und systematischen Entwurfsmethoden und -verfahren weitgehend durchgesetzt. Dabei wird die im Rahmen einer Schaltkreisentwicklung formulierte Aufgabenstellung mit hoher Komplexität in kleinere Einheiten zerlegt, um einerseits eine hierarchische Sicht über die Gesamtschaltung zu ermöglichen und andererseits die Komponenten überschaubar und einfach zu gestalten. Diese Vorgehensweise wird als Top-Down-Entwurf bezeichnet.

Ein wesentliches Hilfsmittel für den Entwurf sind Hardware-Beschreibungssprachen (HDLs). HDLs sind formale Sprachen, die zur strukturierten Beschreibung der Architektur von Hardware-Systemen verwendet werden. Unter der Architektur wird die Angabe der Ein- und Ausgangsanschlüsse, die Topologie eines Schaltkreises, also die Konnektivitätsbeschreibung der Schaltkreiskomponenten, und die Verhaltensbeschreibung eines Hardware-Systems verstanden.

Die HDLs werden beim Entwurf von Schaltkreisen als Eingabesprache von Simulatoren und Synthese-Programmen eingesetzt. Die strukturierte und präzise Beschreibung eines Hardware-Systems mit einer HDL unterstützt die Dokumentation des Systems und bildet eine Basis für eine effiziente Kommunikation zwischen Schaltungsdesignern.

Eine neue Entwicklung auf diesem Gebiet stellt die Hardware-Beschreibungssprache VHDL dar, die im Auftrag der US-Regierung im Rahmen des Projektes VHSIC (Very High Speed Integrated Circuits) entwickelt wurde [VHD87].

Ursprünglich sollte VHDL als eine gemeinsame Plattform zur Verständigung zwischen den Entwicklern innerhalb großer Entwurfsprojekte dienen. Inzwischen sind aber sowohl von der Industrie als auch von wissenschaftlichen Institutionen so viele Erweiterungen in VHDL eingeflossen, daß sie über fast alle für einen Schaltkreisentwurf notwendigen Merkmale verfügt.

Die erste Version der VHDL wurde 1985 unter der Bezeichnung VHDL 7.2 freigegeben. Eine spätere Version wurde 1987 mit einem völlig neuen Satz von Werkzeugen ergänzt. Im gleichen Jahr wurde die Sprache durch das "Institute of Electrical and Electronics Engineers" in den USA als IEEE-1076 standardisiert.

Der Einsatz von VHDL wird mit vielfältigen Vorteilen beim Entwurf integrierter Schaltkreise verknüpft. Sie unterstützt sowohl eine hierarchische als auch eine bibliotheksbasierte Entwicklung eines Schaltkreissystems. Eine technologieunabhängige Beschreibung eines Schaltkreises ist möglich. Damit können die zu realisierenden Schaltkreise in eine Systembeschreibung eingebettet

und mit den peripheren Schaltungsteilen simuliert und analysiert werden. VHDL stellt Sprachelemente zur Verfügung, die sowohl eine Verhaltens- als auch eine Strukturbeschreibung von Schaltkreisen erlauben. Diese Beschreibungen können in unterschiedlichen Abstraktionsebenen erfolgen. Die in VHDL verwendete Syntax und Semantik kann konsequent über alle Abstraktionsebenen hinweg verwendet werden. Durch die Standardisierung der VHDL können unter Einsatz konsistenter Bibliotheken die in dieser Sprache beschriebenen Systeme zwischen unterschiedlichen Werkzeugen transferiert, ausgetauscht und weiterverarbeitet werden.

Die heute verfügbaren VHDL-Simulatoren unterstützen vorwiegend die Entwicklung von Schaltkreisen auf Gatterebene. Die Basiselemente eines Schaltkreises auf dieser Ebene sind logische Gatter und Verbindungselemente (Leitungen).

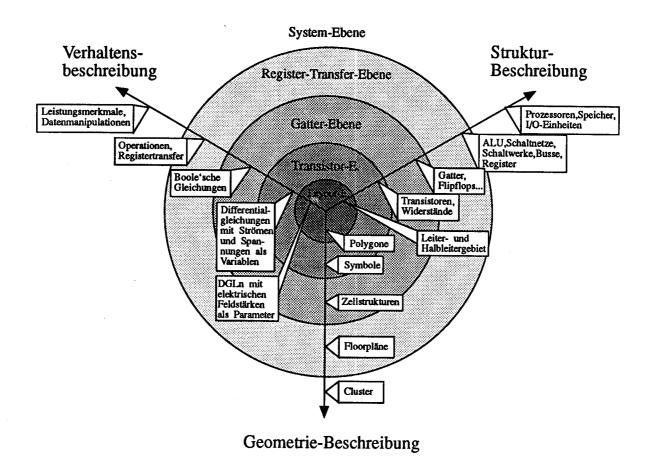

### 2 Abstraktionsebenen

Bei der Beschreibung komplexer Schaltungen können hierarchisch gegliederte Abstraktionen der Schaltungskomponenten vorgenommen werden, die unterschiedliche Sichten einer Schaltung ermöglichen. Die unterschiedlichen Sichten einer Schaltung führen zur Bearbeitung von Schaltungen in unterschiedlichen Ebenen, den sogenannten Abstraktionsebenen. Diese unterschieden sich in ihren beobachtbaren Objekten (z.B. Ströme, Spannungen, digitale Signale u.ä.) sowie den auf der Ebene verwendeten Modellierungs- und Berechnungsmethoden.

Unterschiedliche Beschreibungsarten können zur formalen Definition einer Schaltung in den Abstraktionsebenen zugrundegelegt werden. Dabei kann eine Schaltung durch eine funktionale, eine strukturelle oder eine physikalische Beschreibung dokumentiert werden.

Die funktionale Beschreibung gibt an, wie Operationen oder Transformationen auf Eingangswerte (Eingangsinformationen) angewendet, wie sie intern in Zwischenwerte überführt und wie sie anschließend auf Ausgangswerte (Ausgangsinformationen) abgebildet werden.

Die strukturelle Beschreibung stellt die Zusammensetzung größerer Strukturen aus kleineren Strukturen und Modulen in einer Schaltung dar. Die einzelnen Elemente können in Abhängigkeit der abstrakten Sicht durch spezielle Verbindungsstrukturen (Ein-/Ausgabetore, Kommunikationskanäle etc.) oder auch direkt durch Leitungen, Busse u.ä. verbunden sein.

Bei der physikalischen Beschreibung können geometrische Aspekte (z.B. die Lage von Schaltungselementen im Layout) oder zeitliche Aspekte (z.B. Datenflüsse) zusammengefaßt und zur Beschreibung zugrundegelegt werden.

In den Abstraktionsebenen werden die Komponenten und die zu verarbeitenden Informationen mit unterschiedlichen Dichten bzw. Abstraktionen erfaßt. Die wichtigsten Abstraktionsebenen digitaler Systeme sind:

- System-Ebene

- Registertransfer-Ebene

- Gatter-Ebene

- Transistor-Ebene

- Layout-Ebene

Die verschiedenen Ebenen sind in ihrer Reihenfolge durch einen immer größeren Detailreichtum und eine geringer werdende Übersichtlichkeit gekennzeichnet.

Für jede Ebene existieren aufgrund unterschiedlicher Aspekte unterschiedliche Beschreibungsarten einer Schaltung. Die unterschiedlichen Beschreibungsarten in unterschiedlichen Abstraktionsebenen lassen sich aus der Abbildung 2-1 in Anlehnung an das Gajsky-Kuhn-Diagramm (oder auch Y-Diagramm genannt) ableiten [RAM89].

Abbildung: 2-1: Das Y-Diagramm

### 3 Simulation auf Gatter-Ebene

Mit der fortschreitenden Entwicklung der Technologie und der Verbreitung großintegrierter Schaltungen werden von Designern und Anwendern integrierter Schaltkreise wirklichkeitsgetreue und zuverlässige Simulatoren zur Analyse und Verifizierung von Schaltungen verlangt, da die Prototypherstellung einer Schaltung mit hohen Kosten verbunden ist. Die korrekte Analyse einer Schaltung mit adäquaten Simulationszeiten stellt daher hohe Anforderungen an einen Simulator. Durch die Vielfältigkeit der Eigenschaften der Elemente bzw. der Technologie- und Prozeßparameter werden von einem Simulator genaue Definitions- und Behandlungsmöglichkeiten für Modelle mit den entsprechenden Zeitparametern und physikalischen Größen gefordert. Um möglichst genaue Simulationsergebnisse zu erzielen, muß der Simulator weiterhin über ausgereifte Berechnungsmethoden und Verfahren in Verbindung mit erweiterten Zustandsräumen für digitale Signale verfügen, die die erhöhte Anzahl logischer Signalzustände berücksichtigt.

Der Einsatzbereich der Logiksimulatoren als Entwicklungs- und Entwurfswerkzeuge erstreckt sich auf die Architektur- bzw. Logikentwicklung einer Schaltung (CAE: Computer Aided Engineering), den Layoutentwurf (CAD: Computer Aided Design) und den Schaltungstest (CAT: Computer Aided Test).

Ein Logiksimulator bildet auf Gatter-Ebene die reale Schaltung durch den Einsatz mathematischer und/oder funktioneller Modelle für die Gatter der Schaltung im Rechner ab. Mit Hilfe dieser Modelle werden bei der Berechnung der Schaltung die Ausgangsinformationen der Schaltung (Ausgangssignale) für bestimmte vom Entwickler definierte Eingangsinformationen (Eingangssignale, Stimulies) ermittelt. Die Genauigkeit der Simulationsergebnisse hängt weitgehend von der Genauigkeit der gewählten Modelle sowohl für die Elemente als auch für die Signale entlang der Verbindungen zwischen den Elementen ab. Durch die Erfassung unterschiedlicher Parameter (z.B. Verzögerungszeiten, Anstiegs- und Abfallzeiten, Lastfaktoren u.ä.) wird die Genauigkeit der Modelle stark beeinflußt.

Mit der Simulation einer Schaltung können etwaige Entwurfsfehler entdeckt und beseitigt werden, was zu einem fehlerfreien Entwurf einer Schaltung aus der logischen (architektonischen) Sicht führt. Außerdem können die Entwürfe hinsichtlich unterschiedlicher Schaltungsparameter (z.B. Leistungsbedarf, Signallaufzeiten entlang der Pfade, Empfindlichkeiten u.ä.) optimiert werden.

Der Einsatz von Simulatoren bei der Schaltungsentwicklung ermöglicht eine beträchtliche Zeitersparnis in der Entwurfsphase einer Schaltung. Der aufwendige Aufbau und Test eines Musters wird überflüssig.

Auch die Verifikation einer Schaltung kann durch eine wiederholte Simulation der Schaltung durchgeführt werden.

Bei der Verifiktion wird die Frage gestellt, inwieweit eine entwickelte Schaltung die bei der Aufgabenstellung formulierten Randbedingungen erfüllt. Die Grundlage für die Beantwortung dieser Frage bildet im allgemeinen ein Pflichtenheft. Aus der praktischen Erfahrung kann festgestellt werden, daß hierbei neben Entwurfsfehlern auch Fehler im Pflichtenheft erkannt werden.

Eine digitale Schaltung auf Gatter-Ebene wird als eine Einheit mit Eingängen und Ausgängen betrachtet, die Signale empfängt, sie manipuliert und die Resultate an die Ausgänge weiterleitet. Die Manipulation der Informationen wird in Abhängigkeit der in der Schaltung realisierten Funktion durch entsprechende Komponenten durchgeführt.

### 4 Modellierung von Gattern

Zur Modellierung eines Gatters sind zu erfassen:

- a) Die logische Funktion, die das ideale Verhalten eines Gatters dokumentiert. Hierfür werden Boole'sche Gleichungen eingesetzt.

- b) Die physikalischen Eigenschaften aufgrund der verwendeten Technologie, die das reale Verhalten des Gatters in einer Schaltung bestimmen.

Der Informationsfluß entlang eines Gatters erfolgt mit Zeitverzögerungen, die einerseits durch Wanderungsgeschwindigkeit der Ladungsträger in den Transistoren und anderseits durch Ladung und Entladung von Transistor- und Leitungskapazitäten bestimmt werden. Die Nichtlinearitäten der Ströme und Spannungen der Transistoren und Kapazitäten bewirken, daß unterschiedliche Verzögerungszeiten beim 0-1- bzw. 1-0-Übergang am Ausgang eines Gatters entstehen.

In Abhängigkeit der Dauer der Einschaltzeit ton und Ausschaltzeit toff unterscheidet man zwischen

- einer linearen Verzögerungszeit, wenn ton gleich toff ist, und

- einer nichtlinearen Verzögerungszeit, wenn ton ungleich toff ist.

Diese Zeitabschnitte werden bei der Modellierung eines Gatters als eine Basis zur Berechnung von Gatterverzögerungszeiten zugrunde gelegt. Falls keine Verzögerungszeiten bei der Simulation eines Netzwerkes berücksichtigt werden, entsteht eine verzögerungsfreie Modellierung der Gatter. Sie erlaubt eine zeitoptimale Simulation und Verifikation eines Schaltnetzes hinsichtlich seines logischen Verhaltens. Für Schaltwerke ist die Verzögerungszeit jedoch ein essentielles Attribut, das für eine korrekte Arbeitsweise der Schaltung verantwortlich ist. Hier werden die Signalverzögerungen zur Speicherung von Schaltwerkzuständen eingesetzt.

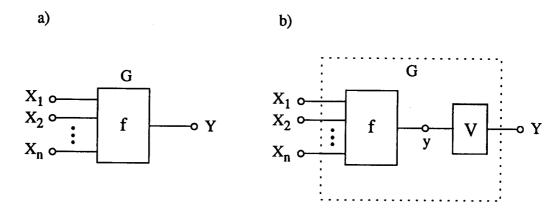

Eine einfache Modellierung des Zeitverhaltens eines Gatters G (Abb. 4-1a), das durch eine Boole'sche Funktion

$$Y(t) = f(X_1(t), X_2(t), ..., X_n(t))$$

(4-1)

charakterisiert ist, verwendet ein zweistufiges Modell (Abb. 4-1b), das als "Unit-Delay-Modell" eines Gatters bezeichnet wird und eine lineare Zeitverzögerung

$$\tau = t_{on} = t_{off}$$

oder  $\tau = (t_{on} + t_{off})/2$

zugrunde legt. In der Gleichung 4-1 sind  $X_1$  bis  $X_n$  die Eingangssignale und Y das Ausgangssignal des Gatters.

- Abbildung 4-1:

- a) Ein allgemeines Gatter G

- b) Unit-Delay-Modell des Gatters G

In der ersten Stufe dieses Modells wird die Boole'sche Funktion des Gatters mit

$$y = f(X_1, X_2, ..., X_n)$$

(4-2)

erfaßt. Gleichung 4-2 beschreibt das logische Verhalten des Gatters und ermöglicht die Berechnung des logischen Zustandes der eingeführten Zwischenvariable y in Abhängigkeit der Eingangsvariablen  $X_1$  bis  $X_n$ .

In einer zweiten Stufe (Stufe V) wird das Zeitverhalten des Gatters als eine lineare Zeitverzögerung  $\tau$ , also sowohl für den 0-1- als auch für den 1-0-Übergang, berücksichtigt. Das neu eingeführtes Element wird als Verzögerungsglied V (Unit-Delay-Element) bezeichnet. Für das Verzögerungsglied gilt:

$$Y(t) = y(t-\tau) \tag{4-3}$$

Durch Einsetzen der Gleichung 4-2 in die Gleichung 4-3 kann die Modellgleichung für das Gatter ermittelt werden:

$$Y(t) = f\{(X_1(t-\tau), X_2(t-\tau), ..., X_n(t-\tau)\}$$

(4-4)

Diese Gleichung beschreibt sowohl das logische als auch das zeitliche Verhalten eines Gatters. In diesem Modell bewirkt jedes Eingangssignal die gleiche Zeitverzögerungszeit  $\tau$ , die durch das Verzögerungsglied V am Ausgang des Gatters repräsentiert wird. Damit wird angenommen, daß alle Signalpfade zwischen den Eingangssignalen und dem Ausgangssignal gleich sind. Diese Modellierungsart wird auch als "ausgangsseitige Delay-Modellierung" bezeichnet.

Eine formale Beschreibung des Gatterverhaltens in dieser Modellierungsart kann wie folgt angegeben werden:

IF "eine Änderung an einem der Eingänge vorliegt" THEN

$$Y \leftarrow (f(X_1, X_2, X_3 ... X_n))$$

AFTER  $\tau$  ns ENDIF

In dieser Formulierung wird der Variable Y der durch die Funktion f errechnete Wert mit einer Verzögerung von  $\tau$  ns zugewiesen.

Prinzipiell kann aber im Unterschied zu dem oben angegebenen Modell jeweils jedem Eingang ein Verzögerungsglied zugeordnet werden. In diesem Fall spricht man von einem "eingangsseitigen Modellierungsverfahren".

### 5 Signalzustände und -modelle

Signale sind Informationsträger. Sie stellen zeitlich veränderliche Größen dar, die die auf sie abgebildeten Informationen tragen. In elektronischen Systemen sind Ströme und Spannungen die Informationsträger. Sie sind physikalische Größen, die zeitlich entweder einen kontinuierlichen Verlauf oder einen diskontinuierlichen Verlauf in diskreten Stufen besitzen können. Auch der Informationsparameter, der in den meisten Fällen die Amplitude eines Trägers darstellt, kann einen kontinuierlichen oder einen diskreten Verlauf aufweisen.

Zur Differenzierung von Signalzuständen und zur Behandlung von Signalen in einem Simulator, der für die Simulation von Schaltkreisen unter Berücksichtigung physikalischer Eigenschaften in unterschiedlichen Technologien eingesetzt werden soll, wird eine Modellierung der Signalzustände durch die Zuordnung von Signalgewichten oder Signalstärken vorgenommen.

Bei der Modellierung der Signalstärke werden im allgemeinen mehrere Stufen zugrundegelegt. Die am häufigsten verwendeten Stärken sind im folgenden angegeben:

### F (forcing):

Die Stärke bezeichnet den Signalzustand eines Knotens mit höchstem Gewicht. Hier liegt ein Knoten vor, der seinen Zustand durch eine Verbindung mit verschwindend kleinem Widerstand zu anderen Knoten überträgt. Derartige Knoten in einem Netzwerk sind insbesondere die Betriebsspannungs- und Masse-Knoten. Bei dieser Stärke wird die Verbindung als annähernder Kurzschluß zwischen zwei Knoten betrachtet.

### W (weak resistive)

Diese Stärke gilt für einen Knoten, der eine Verbindung mit einem niedrigen Widerstandswert zu einem anderen Knoten aufweist. Damit wird der Knoten relativ stark beeinflußt, falls er von  $V_{DD}$ - oder  $V_{SS}$ -Knoten getrieben wird.

### R (resistive):

Bezeichnet den Signalzustand eines Knotens, der durch einen mittelohmigen Widerstand an einen anderen (aktiven) Knoten im Netzwerk angeschlossen ist.

### Z (high impedance):

Dieser Zustand entspricht dem typischen Schwebezustand bei Tri-State-Ausgängen eines Gatters. Eine Beeinflussung des Gatter-Ausgangsknotens durch den  $V_{DD}$ - oder durch den  $V_{SS}$ -Knoten liegt in einer vernachlässigbar schwachen Form vor.

### D (disconnect):

Dieser Zustand stellt die Unterbrechung zwischen zwei Knoten dar, d. h. die Knoten können sich gegenseitig nicht beeinflussen.

Zusätzlich wird ein Zustand U (Undefiniert, Unknown) eingeführt, wenn keine Aussage über die tatsächliche Stärke eines Knotens gemacht werden kann.

Jede der oben beschriebenen Stärken (bis auf D) kann den logischen Zuständen 0, 1 oder X zugeordnet werden, so daß das Schema in Abb. 5-1 zustande kommt.

In der Tabelle sind die Grundzustände der Signale in der obersten Zeile angegeben. Die restlichen Zeilen stellen die möglichen Kombinationen der Grundzustände dar. Insgesamt erhält man aus der Tabelle 46 logische Werte zur Darstellung von Signalen (Summe der Zeilen und Spalten, d. h. Summe aller Grundzustände und ihrer Kombinationen).

Durch die Einführung von Stärken ist man nun in der Lage, wenn mehrere treibende Knoten auf einen gemeinsamen Knoten wirken, den effektiven Zustand des Knotens zu bestimmen.

Zustandskombinationen

### Grundzustände

|      |       |    |     | Gruii      | uzusta | шае      |     |     |     |  |

|------|-------|----|-----|------------|--------|----------|-----|-----|-----|--|

| Wert | F0    | R0 | W0  | <b>Z</b> 0 | D      | Z1       | W1  | R1  | F1  |  |

| U    |       |    |     |            |        |          |     |     |     |  |

| ZDX  |       | ZI | ΟX  |            |        |          |     |     |     |  |

| DZX  |       |    |     |            | D      | ZX       |     |     |     |  |

| ZX   |       |    |     |            | ZX     |          |     |     |     |  |

| WZ0  |       |    | W   | /Z0        |        |          |     |     |     |  |

| WZ1  |       |    |     |            | WZ1    |          |     |     |     |  |

| WDX  | WDX   |    |     |            |        | <u> </u> |     |     |     |  |

| DWX  |       |    | DW  |            |        | DWX      |     |     |     |  |

| WZX  |       |    | WZX |            |        |          |     |     |     |  |

| ZWX  |       |    | ZWX |            |        | VX       |     |     |     |  |

| WX   |       |    |     | WX         |        |          |     |     |     |  |

| RW0  |       | RV | VO  | <u> </u>   |        |          |     |     |     |  |

| RW1  |       |    |     |            |        | RW1      |     |     |     |  |

| RZ0  | RZ0   |    |     |            |        |          |     |     |     |  |

| RZ1  |       |    |     |            |        |          | RZ1 |     |     |  |

| RDX  | RDX   |    |     |            |        |          |     |     |     |  |

| DRX  | DRX   |    |     |            |        |          |     |     |     |  |

| RZX  | RZX   |    |     |            |        |          |     |     |     |  |

| ZRX  | ZRX   |    |     |            |        |          |     |     |     |  |

| RWX  | RWX   |    |     |            |        |          |     |     |     |  |

| WRX  | WRX   |    |     |            |        |          |     |     |     |  |

| RX   | RX    |    |     |            |        |          |     |     |     |  |

| FR0  | FR0   |    |     |            |        |          |     |     |     |  |

| FR1  |       |    |     |            |        |          |     |     | FR1 |  |

| FW0  | FW0   |    |     |            |        |          |     |     |     |  |

| FW1  |       |    |     |            |        |          |     | FW1 |     |  |

| FZ0  |       |    |     |            |        |          |     |     |     |  |

| FZ1  |       |    |     |            |        |          | FZ1 |     |     |  |

| FDX  | FDX   |    |     |            |        |          |     |     |     |  |

| DFX  |       |    |     |            |        | DFX      |     |     |     |  |

| FZX  | FZX   |    |     |            |        |          |     |     |     |  |

| ZFX  | ZF    |    |     |            |        | X        |     |     |     |  |

| FWX  | FWX   |    |     |            |        |          |     |     |     |  |

| WFX  | · WFX |    |     |            |        |          |     |     |     |  |

| FRX  | FRX   |    |     |            |        |          |     |     |     |  |

|      | RFX   |    |     |            |        |          |     |     |     |  |

| RFX  |       |    |     |            |        | Λ        |     |     |     |  |

Abbildung 5-1: Gewichtete Standardlogikwerte, Grundwerte (1. Zeile) und ihre Kombinationen (restliche Zeilen).

### 6 Simulationsverfahren

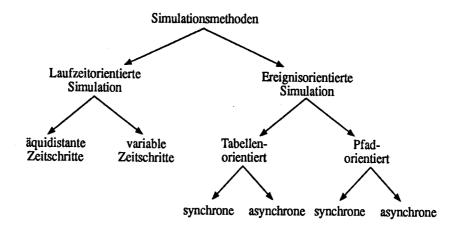

Die Verfahren für die Simulation digitaler Schaltungen können in zwei Kategorien, nämlich laufzeitorientierte und aktivitätsorientierte bzw. ereignisorientierte Verfahren, aufgeteilt werden (Abb. 6-1).

Abbildung 6-1: Strukturierung von Simulationsverfahren.

### a) Laufzeitorientierte Simulation

Bei der laufzeitorientierten Methode wird ein Netzwerk vollständig zu den Zeitpunkten eines Zeitrasters berechnet. Zur Bestimmung der Zeitpunkte werden die Gatterlaufzeiten zugrunde gelegt. Die Gatter können unterschiedliche Verzögerungszeiten als lineare und nichtlineare Verzögerungen oder Laufzeitbereiche aufweisen.

Die aufeinanderfolgenden Berechnungszeitpunkte eines Netzwerkes können äquidistante oder variable Abstände aufweisen.

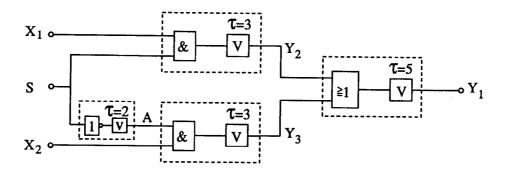

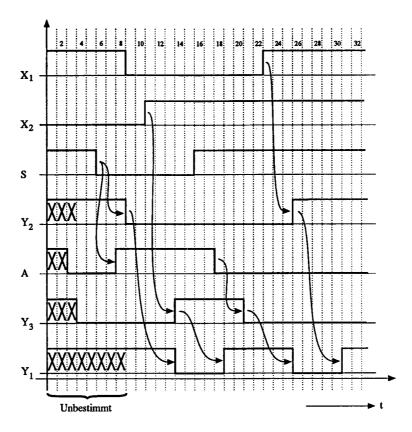

Abb. 6-2 zeigt den Ablauf einer Simulation für eine Schaltung nach diesem Verfahren. In der Abbildung sind neben der Struktur der Schaltung, die Gattermodelle mit ausgangsbezogenen Verzögerungsgliedern enthält, die Modellgleichungen in Abhängigkeit der Signalverzögerungszeiten dargestellt. Eine Simulation wird zum Zeitpunkt t=0 gestartet und in (normierten) Schritten von 1 mit Hilfe der Gleichungen durchgeführt. Das Ergebnis ist als Impulsdiagramm angegeben. Die Eingangssignale X<sub>1</sub>, X<sub>2</sub> und S werden für die Simulation definiert. Sie werden als gegeben vorausgesetzt. Eine Signaländerung am Ausgang der Schaltung entsteht, wenn sich die Eingangssignale ändern.

$$Y_{2}(t) = X_{1}(t-3) S(t-3)$$

$$A(t) = \overline{S}(t-2)$$

$$Y_{3}(t) = A(t-3) X_{2}(t-3) = \overline{S}(t-5) X_{2}(t-3)$$

$$Y_{1}(t) = Y_{2}(t-5) \lor Y_{3}(t-5) = X_{1}(t-8) S(t-8) \lor \overline{S}(t-10) X_{2}(t-8)$$

Abbildung 6-2: Beispiel einer laufzeitorientierten Simulation

### b) Ereignisorientierte Simulation

Bei einer aktivitäts- oder ereignisorientierten Simulation werden die auftretenden Aktivitäten (Ereignisse) erfaßt und deren Fortpflanzung in den betreffenden Pfaden der Schaltung berücksichtigt. Das Verfahren benötigt eine geringere Simulationszeit als die laufzeitorientierte Simulation, da nur die aktiven Phasen der Signale, d.h. nur wenn Änderungen bei den Signalzuständen vorliegen, betrachtet werden und eine Berechnung der Schaltung vorgenommen wird. Ein Ereignis entsteht also durch eine Signaländerung bei den Eingangssignalen oder an den inneren Knoten eines Netzwerkes.

Prinzipiell unterscheidet man zwischen zwei Verfahren ereignisorientierter Simulationsmethoden (vergl. Abb. 5-1):

- Tabellenorientierte Ereignissimulation

("Next Event List Simulation", "Time Mapping Event Scheduling")

- Pfadorientierte Ereignissimulation ("Selective Trace Simulation")

Bei der tabellenorientierten Ereignissimulation wird zur Erfassung der chronologisch auftretenden Ereignisse eine Ereignisliste eingesetzt. Sukzessive werden die Positionen der Tabelle erfaßt und mit Hilfe der zugrunde gelegten Datenstruktur festgestellt, auf welche Elemente sie eine Änderung ausüben. Zusammen mit anderen Eingangszuständen sowie mit der Funktion eines Elementes werden die Ausgangssignale berechnet. Liegt eine Änderung des Ausgangssignals vor, wird die Ereignis-Tabelle aktualisiert, um derartige Änderungen nach der Bearbeitung aller Elemente als neue Ereignisse zu bearbeiten.

Bei der pfadorientierten Ereignissimulation wird nur eine selektive Fortpflanzung der Ereignisse entlang der Pfade berücksichtigt. Bei der Simulation werden also nur die Gatter bearbeitet, die durch ein Ereignis (eine Signaländerung) an den Eingängen aktiviert werden. Alle anderen Gatter werden nicht berücksichtigt.

### 7 Hardware-Beschreibung in VHDL

Die Basis zur Beschreibung digitaler Komponenten und Systeme in VHDL bilden das funktionale und das zeitliche Verhalten sowie der strukturelle Aufbau eines Systems. Daraus ergeben sich bei der Modellierung digitaler Systeme in VHDL drei sich gegenseitig ergänzende Modelle:

- das Verhaltensmodell (behavioral model),

- das Zeitmodell (timing model) und

- das Strukturmodell (structural model).

### a) Das Verhaltensmodell

Eine funktionale Beziehung, die aus einer Folge von Operationen besteht, repräsentiert das Verhalten des Netzwerkes, das durch die Beobachtbarkeit von Auswirkungen an den Ausgängen infolge der Erregungen an den Eingängen (Stimuli) des Netzwerkes charakterisiert wird. Somit bildet die funktionale Beziehung eines Netzwerkes die Grundlage zur Modellierung des logischen Verhaltens des Systems.

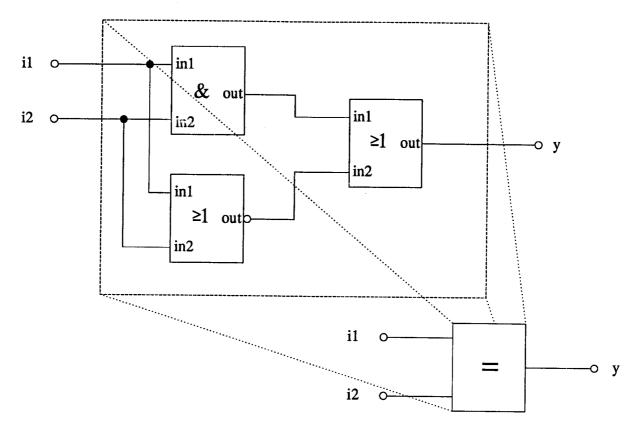

Als Beispiel wird ein digitales System, das aus einem Äquivalenz-Gatter besteht, betrachtet. Das Verhalten des Gatters kann mit Hilfe der Gatterfunktion, die die Ausgangsvariable y in Abhängigkeit der Eingangsvariablen i1 und i2 angibt, beschrieben werden.

Die Struktur der Schaltung ist jedoch erst nach der Auflösung der Gleichung durch NICHT-, UNDund ODER-Gatter darstellbar.

Die formale Verhaltensbeschreibung eines Gatters oder einer Einheit eines Systems in VHDL wird mit Hilfe einer Programmstruktur, die als  $Proze\beta$  bezeichnet wird, vorgenommen.

Ein Prozeß umfaßt Datenstrukturen, Instruktionen, Prozeduren etc., ähnlich wie in prozeduralen Programmiersprachen Pascal oder C. So wird das gesamte System durch eine Ansammlung von unabhängigen und konkurrierenden Prozessen beschrieben, die parallel ausgeführt werden. Die zeitliche Folge der parallel ablaufenden Prozesse in einem System dokumentiert das Verhalten des Gesamtsystems. Zur Kommunikation und zur Synchronisation zwischen den Prozessen werden Signale eingesetzt. Da die Signale sich entlang von Signalpfaden in einem digitalen System

fortpflanzen können, werden sie auch zur Aktivierung und zur Steuerung von Prozessen eingesetzt. Ein Prozeß generiert ein Signal, das sich entlang eines Pfades auswirkt. Ein oder mehrere Prozesse entlang des Signalpfades, die das Signal empfangen, werden zur Bearbeitung des Signals aktiviert.

Die Kommunikation über Pfade in einem System ist an einen festen Datentyp gebunden. Z.B. kann über einen Pfad vom Typ *Integer*, kein Signal vom Typ *Bit* übertragen werden.

Die Prozesse werden solange ausgeführt, bis sie in einen Warte-Zustand versetzt werden. Aus diesem Warte-Zustand heraus kann der Prozeß wieder aktiviert werden, wenn eine bestimmte Bedingung erfüllt ist. Solche Bedingungen könnten benutzt werden, um den Abstand von Prozessen und so das Verhalten einer Schaltung zu modellieren. Z.B. werden Prozesse benötigt, die nur dann reagieren, wenn sich ein Zustand im System ändert. Diese Zustandsänderung wird durch die Änderung eines Signalwertes repräsentiert, da die Signale die Zustände des Systems repräsentieren. In VHDL heißt das, daß ein Prozeß sensitiv im bezug auf den Wert eines Datenpfades ist. Derartige Datenpfade heißen sensibilisierte Kanäle (sensitivity channels). Wenn sich der Wert auf einem dieser Kanäle ändert, wird der zugehörige Prozeß reaktiviert. Um diese Signal-Bedingungen innerhalb eines Prozesses zu implementieren, wird die wait-Anweisung benutzt. Wird bei der Ausführung eines Prozesses eine wait-Anweisung gefunden, wird die Bedingung, die zur Aktivierung benötigt wird, gespeichert und der Prozeß in den Warte-Zustand versetzt.

Der zu dem Beispiel des Äquivalenzgatters mit zwei Eingängen gehörende Prozeß hat zwei sensitive Eingangskanäle, nämlich die Eingänge i1 und i2. Daher wird der Prozeß, der die Äquivalenzfunktion für den Ausgangswert y berechnet, bei jeder Änderung eines dieser Eingangswerte neu gestartet.

### b) Das Zeitmodell in VHDL

Um das reale Verhalten eines Systems abbilden bzw. modellieren zu können, werden in VHDL die Zeit und speziell die Verzögerungszeiten von Komponenten als Parameter in die Modelle aufgenommen.

Das Zeitverhalten der Komponenten im System ist im allgemeinen durch Verzögerungszeiten gegeben, die in ihrer Gesamtheit das zeitliche Verhalten des Systems widerspiegeln. Neben Gatterverzögerungszeiten und Verzögerungszeiten für sonstige Komponenten in einem Netzwerk können in VHDL auch die Aktionen mit Verzögerungszeiten behaftet sein. Beispielsweise können entlang eines Signalpfades mit mehreren Prozessen Verzögerungszeiten für die Aktivierung von Prozessen und für die Ausführung der im Prozeß vorhandenen Aktionen eingesetzt werden. Derartige Verzögerungen werden als Aktionsverzögerung bezeichnet. Die Anzahl von Aktionen entlang eines Signalpfades ist beliebig.

Eine Aktionsquelle (z.B. Ausgang eines Gatters), die einen Signalpfad beeinflußt, wird als Signaltreiber (signal driver) bezeichnet.

Zu einem Signal kann nur ein Treiber gehören. Ein Treiber kann jedoch mehrere Signalquellen umfassen. Der Treiber wird durch eine geordnete Menge von Zeit/Werte-Paaren, die jeweils den Wert des Signals zu den zugehörigen Zeiten angeben, definiert. Folglich stellt ein Signal eine physikalische Größe dar, die während der Aktivierung und Ausführung von Prozessen ständig aktualisiert wird.

Die Bearbeitung eines Modells in VHDL erfolgt in zwei Phasen, die als Simulationszyklus bezeichnet werden. In der ersten Phase werden die Ursachen (Stimuli) erfaßt, die jeweils eine Signal-Änderung erzeugen. In der zweiten Phase werden die daraus folgenden Auswirkungen im Modell bestimmt.

Während der ersten Phase des Simulationszyklus werden die Werte den Signalen zugeordnet. Dieser Schritt ist abgeschlossen, wenn alle Signale die zur augenblicklichen Simulationszeit gehörenden Werte angenommen haben. In der zweiten Phase werden alle die Prozesse, die über sensitive Kanäle neue Werte erhalten haben, aktiviert und ausgeführt, bis sie in den Wartezustand versetzt werden, d.h. bis sie auf eine wait-Anweisung stoßen oder vollständig ausgeführt worden sind. Die Phase ist beendet, wenn alle Prozesse jeweils im Wartezustand (suspend) sind. Um den Zyklus zu beenden, wird die Simulationszeit auf den nächsten Zeitpunkt gesetzt, zu dem wiederum eine Aktion stattfindet. Dann beginnt der nächste Simulationszyklus.

Die Simulation ist beendet, wenn ein bestimmter (vorgegebener) Zeitpunkt erreicht ist, oder wenn keine Signaländerungen mehr vorliegen, die einen Prozeß neu starten könnten.

Betrachtet man den oben beschriebenen Ablauf, so ist zu erkennen, daß immer eine gewisse Zeit von der Generierung eines Wertes durch einen Prozeß bis hin zum Eintragen in das zugehörige Signal vergeht. Wenn keine explizite Verzögerung bei der Zuweisung eines Wertes an ein Signal angegeben ist, wird mindestens ein sogenanntes delta-delay eingesetzt. Das delta-delay bewirkt keine Erhöhung der Simulationszeit, es sorgt aber dafür, daß ein Simulationszyklus zum Eintragen der neuen Werte durchlaufen wird (update).

Immer wenn sich der neue Wert eines Signals vom vorherigen unterscheidet, bezeichnet man auch dies als ein Ereignis. Ein sensitiver Kanal reagiert also auf die Ereignisse des zugehörigen Signals, so daß mit VHDL das ereignisorientierte Simulationsverfahren einfach zu realisieren ist.

### c) Das Strukturmodell

Die in einem digitalen System vorhandenen Ein- und Ausgänge werden in der Schnittstelle der Schaltung (entity oder entity declaration) definiert.

Die Verbindungen zwischen den einzelnen Einheiten des Systems übernehmen die Kommunikation und den Datenaustausch zwischen den Einheiten. Die Schnittstellen, die zu Verbindungen mit anderen Einheiten führen, werden als *ports* bezeichnet. Die Port-Beschreibungen (*port declaration*) enthalten die Definitionen der am Datenaustausch beteiligten Signale.

Als Beispiel eines Strukturmodells kann das Äquivalenzgatter aus drei Teilsystemen aufgebaut werden. Jedes Teilsystem stellt eine vollständige Einheit dar (AND, OR, NOR). In Abb. 7-3 sind Elemente der Schaltung, die jeweils als getrennte *entities* definiert werden, angegeben.

In jedem Element existiert eine Port-Beschreibung, die die Namen der intern verwendeten Ein- und Ausgänge definiert. Durch den Aufruf dieser Teilsysteme aus der nächst höheren Ebene (Äquivalenz), werden die aktuellen Werte über die Signale an die internen Signale übergeben bzw. die berechneten Werte von den internen Signalen auf die "Verbindungssignale" weitergeleitet. Auf diese Weise kann ein Element, daß sich in einer Bibliothek befindet mehrfach benutzt werden (Instanziierung).

Abbildung 7-3: Strukturmodell des Äquivalenzgatters

### 8 Struktur eines VHDL-Programms

Ein VHDL-Entwurf - eine VHDL-Entwurfseinheit (unit) - setzt sich aus der Bausteindeklaration (entity declaration) und mindestens einem Architekturrumpf (architectural body) zusammen. Eine VHDL-Entwurfseinheit ist ein abgeschlossener Block von Anweisungen. Sie kann einzeln auf Korrektheit der Syntax überprüft werden. Ist die Syntax korrekt, kann die Einheit als Bibliothekselement für weitere Entwürfe verwendet werden.

### Bausteindeklaration (entity declaration)

Die Bausteindeklaration ist formal folgendermaßen aufgebaut:

```

entity Bausteinname is

port (Schnittstellenliste);

generic (Parameterliste);

Deklarationen;

begin

Anweisungen;

end Bausteinname;

```

Schnittstellenlisten definieren die Verbindungen eines Bausteins zur Außenwelt. Sie werden durch das reservierte Wort port eingeleitet. Die einzelnen Schnittstellenelemente werden

jeweils durch ein Semikolon voneinander getrennt. Jedes Schnittstellenelement kann mehrere Schnittstellenobjekte enthalten, die durch Kommata getrennt werden. Die Schnittstellenliste darf nur Objekte der Objektart signal enthalten. Eine Schnittstellenliste definiert folgende Objekteigenschaften:

- a) den Datentyp der Schnittstellenobiekte

- b) die Richtung des Datenflusses über die Schnittstelle

Für die Festlegung der Richtung des Datenflusses stellt VHDL vier Modi zur Verfügung (in, out, inout und buffer). Durch die Angabe der Richtung kann bei der Simulation überprüft werden, ob die Schaltungsstruktur des Entwurfs korrekt ist. Die Bedeutung der Modi ist in Tab. 8-1 dargestellt.

| Modus  | Art der Leitung                                              |  |  |  |  |

|--------|--------------------------------------------------------------|--|--|--|--|

| in     | Eingangsleitung;<br>nur lesender Zugriff (default)           |  |  |  |  |

| out    | Ausgangsleitung;<br>nur schreibender Zugriff                 |  |  |  |  |

| inout  | bidirektionale Leitung;<br>lesender und schreibender Zugriff |  |  |  |  |

| buffer | Ausgangsleitung;<br>lesender und schreibender Zugriff        |  |  |  |  |

Tabelle 8-1: Modi zur Steuerung des Datenflusses

Der Modus buffer sollte verwendet werden, wenn das Signal eigentlich ein Ausgangssignal ist, jedoch auch für interne Berechnungen benötigt wird.

Die allgemeine Form eines Schnittstellenelements ist folgende:

```

Objektart Bezeichnerliste :

Richtung Datentyp := Standardwert

```

Die minimale Definition eines Schnittstellenelements besteht aus der Bezeichnerliste und der Angabe des Datentyps. Die Objektart ist bei der Schnittstellenliste festgelegt und muß daher nicht angegeben werden.

```

port (Eingang1, Eingang2: in Bit;

Wert: in Integer; Ausgang: out Bit);

```

<u>Parameterlisten</u> erlauben die Übergabe von modellabhängigen Parametern an einen Baustein. Z.B. ist es möglich, universelle Modelle zu erstellen und diesen bausteinabhängige Parameter, wie die Verzögerungszeit, über diese Parameterlisten anzugeben. Eine Parameterliste ist eine spezielle Schnittstellenliste, die durch das Schlüsselwort generic eingeleitet wird. Für diese Liste ist nur die Objektart constant und die Datenflußrichtung in zugelassen.

- <u>Deklarationen</u> innerhalb der Bausteindeklaration können eingesetzt werden, um dieselben Objekte tür verschiedene Architekturrümpfe benutzen zu können. Die Deklaration in jedem einzelnen Architekturrumpf kann so entfallen.

- <u>Anweisungen</u> innerhalb der Bausteindeklaration können dazu benutzt werden, einige Aktionen (wie die Überprüfung von Eingangsbedingungen) für alle Architekturrümpfe gemeinsam durchzuführen. Dies vereinfacht wiederum die Architekturrümpfe.

Im folgenden ist die Bausteindeklaration für ein RS-Flip-Flop angegeben:

```

entity RS_FF is

port (R, S: in Bit; Q, QN: buffer Bit);

generic (Ver);

begin

assert not (S = '1' and R = '1')

report "Fehler: S und R sind auf '1'"

severity Error;

end RS_FF;

```

### Architekturrumpf (architectural body)

Ein Architekturrumpf beschreibt die Struktur und das Verhalten des Bausteins. Zu jeder Bausteindeklaration muß mindestens ein Architekturrumpf existieren. Dies ist der grundlegende Aufbau:

```

architecture Rumpfname of Bausteinname is

Deklarationen;

begin

Anweisungen;

end Rumpfname;

```

Der Deklarationsteil enthält die Typ-, Signal- und Konstantendeklarationen. Außerdem werden hier Komponenten deklariert, die schon in VHDL beschrieben worden sind und die im Anweisungsteil instanziiert werden.

Der Anweisungsteil enthält die Struktur- und/oder die Verhaltensbeschreibung des Bausteins. Die Verhaltensbeschreibung besteht aus Prozessen oder parallel zu verarbeitenden Anweisungen (concurrent statements). Die Strukturbeschreibung umfaßt die Komponenteninstanziierungen.

Neben Bausteindeklarationen und Architekturrümpfen gibt es Elemente, die die Übersichtlichkeit einer VHDL-Beschreibung verbessern können:

- Unterprogramme (subprograms),

- Pakete (packages) und

- Bibliotheken (libraries).

Insbesondere die Bibliotheken ermöglichen es, getestete VHDL-Entwurfseinheiten ohne erneute Analyse und damit ohne zusätzlichen Zeitaufwand in anderen VHDL-Bausteinen einzusetzen.

### 9 Zusammenfassung

In diesem Beitrag wird eine Einführung in VHDL gegeben. Es werden die prinzipiellen Modellierungsverfahren digitaler Komponenten und Signale und der Aufbau eines VHDL-Programms dargestellt, sowie die in VHDL verwendeten Modelle, Daten und Objekte. Die Struktur- und Verhaltensbeschreibung digitaler Schaltkreise in VHDL wird erläutert.

Mit zunehmender Steigerung der Komplexität elektronischer Systeme hat die standardisierte Hardware-Beschreibungssprache VHDL ((very high speed integrated circuits) Hardware Description Language) als ein höchst geeignetes Dokumentations- und Entwicklungswerkzeug für den strukturierten Entwurf komplexer Schaltkreise an Bedeutung gewonnen. Die VHDL erlaubt es, ein elektronisches System sowohl aus einer abstrakten Sicht als auch auf Gatter-Ebene zu synthetisieren, sein Verhalten durch Simulations- und Verifikationswerkzeuge zu überprüfen und zur Herstellung vorzubereiten. Bereits entwickelte und getestete Komponenten können wiederholt zur Vereinfachung und Beschleunigung eines Entwurfs herangezogen werden.

Mit ihrem Einsatz wird insbesondere "Time-To-Market" drastisch reduziert, die Verständigung zwischen den Beteiligten in einem Projekt in hohem Maße gesteigert und der strukturierte Entwicklungsablauf gefördert.

Im vergangenen Jahr wurde vom "VHDL Standardization Committee" eine überarbeitete Version der Sprache vorgestellt. Der neue Entwurf umfaßt mehrere sinnvolle Ergänzungen (z.B. Fanout abhängiges Timing, Einsatz globaler Variablen, Varianten-Records, etc.). Damit wird die Verbreitung der Sprache VHDL weiterhin unterstützt.

### 10 Literaturverzeichnis

[ASH90] Ashenden, P. J.:

"The VHDL Cookbook", Adelaide, 1990

[BEu87] Bechtold, M.; Reus, Th.; Tavangarian, D.:

"Simulation hybrider Schaltungen", 4. Symposium Simulationstechnik, Zürich, Sept. 1987

[COE89] Coelho, D.R.:

"The VHDL Handbook", Kluwer Academic Publishers, Boston, 1989

[HOR85] Horneber, E.-H.:

"Simulation elektrischer Schaltungen auf dem Rechner", Springer, Berlin, 1985

[HuS81] Hachtel, G. D.; Sangiovanni-Vincentelli, A. L.:

"A Survey of Third-Generation Simulation Techniques", Proc. of the IEEE, Vol. 69, No. 10, S. 1264-1280, Oct. 1981

[LIu89] Lipsett, R.; Schaefer, C.; Ussery, C.:

"VHDL: Hardware Description and Design", Kluwer Academic Publishers, Dordrecht, 1989

[RAM89] Rammig, F. J.:

"Systematischer Entwurf digitaler Systeme", Verlag B. G. Teubner, Stuttgart, 1989

[RuD83] Ruehli, A. E.; Ditlow, G. S.:

"Circuit analysis, logic simulation and design verification for VLSI", Proc. IEEE, 71, pp. 34-48, January 1983

[SCH87] Schwarz, A. F.:

"Computer Aided Design of Microelectronic Circuits and Systems", Academic Press, London, 1987

[SPI85] Spiro, H.:

"Simulation integrierter Schaltungen", Oldenbourg Verlag, 1985

[TAu91] Koch, M.; Macke, H.; Tavangarian, D.:

"Struktur eines VHDL-basierten Simulators für die Lehre", ASIM91 7.Symposium Simulationstechnik, Hagen 1991, S.406-410

[TuK92] Koch, M.; Tavangarian, D.:

"Practical Design Experience Using VHDL", Proceedings of the 3.EUROCHIP Workshop on VLSI Design Training, Grenoble 1992, S.124-129

[VHD87] IEEE Standard VHDL Language Reference Manual -Std 1076- 1987, IEEE, New York, 1988.

### Entwicklung eines Radschlupfprozessors mit der Beschreibungssprache VHDL

Dipl.Ing. T.Büchner, Roland Granzer Institut für Mikroelektronik Stuttgart Prof.Dr.Ing G.Kampe Fachhochschule für Technik Esslingen

Hier wird über eine Diplomarbeit berichtet, bei der ein Radschlupfprozessor mit der Hardwarebeschreibungssprache VHDL in einem anwenderspezifischen IC implementiert werden soll. Nach einem Überblick über die Synthese mit VHDL wird am Beispiel einer Teileinheit des Prozessors die Umsetzung in Hardware beschrieben.

### 1. Einleitung

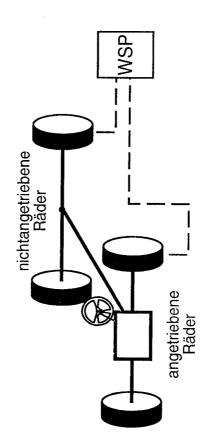

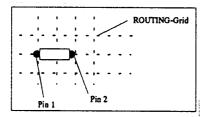

Die Fahrsicherheit eines Automobils hängt in hohem Maße vom Kraftschluß zwischen Reifen und Fahrbahn ab. Eine bestimmende Größe dabei ist der Radschlupf, mit dessen Hilfe Aussagen über den aktuellen Zustand der Bodenhaftung gemacht werden können. Bild Nr.3 zeigt die Eingangsgrößen des Radschlupfprozessors. Die Signale der ABS-Sensoren eines angetriebenen und eines nicht angetriebenen Rades werden zur Schlupfberechnung benötigt. Die ABS-Sensoren bestehen aus einer gelochten Metallplatte und einer Spule, in der während der Fahrt zur Geschwindigkeit proportionale Signale erzeugt werden (siehe Bild 3 unten). Der so ermittelte Schlupfwert wird dann über eine interne serielle Schnittstelle an einen zentralen Kfz-Controller übermittelt, der dann die Auswertung bzw. Darstellung für den Fahrer vornimmt.

### 2. Einführung in VHDL

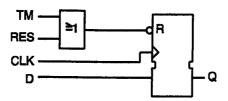

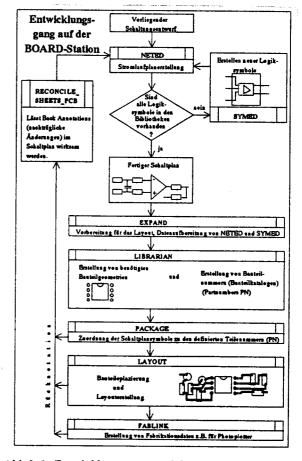

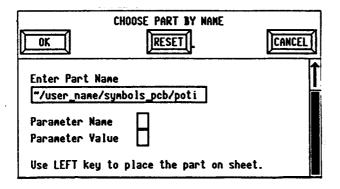

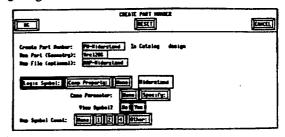

In Bild 4 werden die Gründe genannt, warum mit dieser Diplomarbeit vorhandene Prototypen des Radschlupfprozessors in VHDL neu beschrieben werden sollten. Mit die wichtigsten Gründe sind dabei, daß mit VHDL ein großer Teil der Schaltkreisentwicklung durchführbar ist und die Sprache durch die Softwarehersteller unterstützt wird. Auf Bild 5 ist am Beispiel eines einfachen Flipflops der Unterschied zwischen den beiden wichtigsten Beschreibungsarten von VHDL dargestellt. Die Verhaltensbeschreibung geschieht ähnlich wie in C oder Pascal auf einer sehr hohen Ebene, während die Strukturbeschreibung einer Netzliste oder

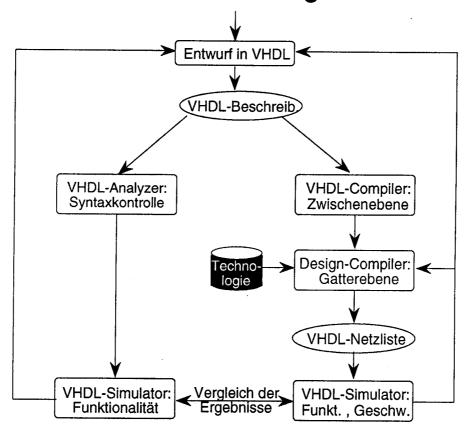

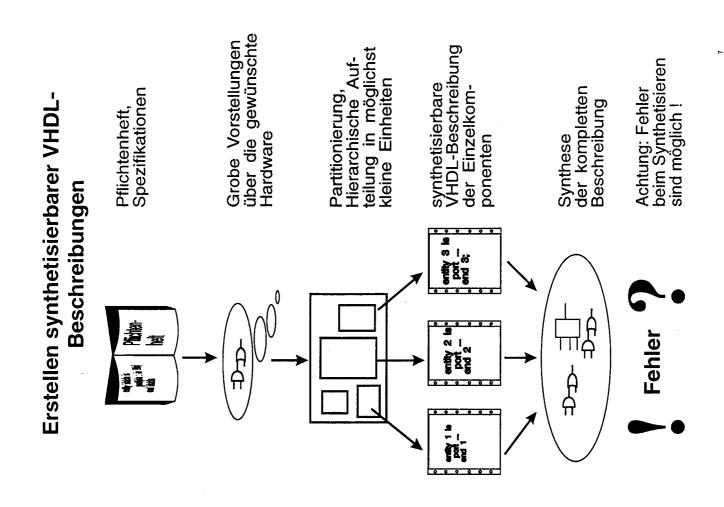

einem Schaltplan entspricht. Bild 6 zeigt den Entwicklungszyklus mit einer Synthese der VHDL-Beschreibung. Die eigentliche Umsetzung (Synthese) von Verhaltensbeschreibung in Netzliste werden durch den VHDL-Compiler bzw. den technologieabhängigen Design-Compiler vorgenommen. Allerdings ist nicht der komplette Umfang der VHDL-Sprache synthetisierbar, sondern nur ein gewisser, nicht allzu komplexer, Ausschnitt davon (z.B. keine Rekursion). Die Vorgehensweise bei der Erstellung einer synthetisierbaren VHDL-Beschreibung ist auf Bild 7 zu sehen. Besonders wichtig bei diesem Top-down Entwurf ist, schon bei der Verhaltensbeschreibung möglichst genaue Vorstellungen über die gewünschte Hardware mit einfließen zu lassen. D.h. man sollte wissen, wo man Zähler, Register, Schaltwerke usw. einsetzen will und diese Einheiten dann auf Verhaltensebene beschreiben. Dadurch ist dann später eine gute Verifizierbarkeit und Änderbarkeit der synthetisierten Schaltung gewährleistet.

### 3. Der Aufbau des Radschlupfprozessors

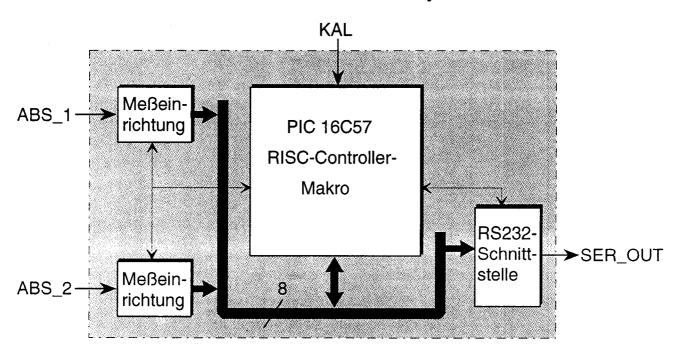

Auf Bild 8 sind die Einzelkomponenten des Radschlupfprozessors zu sehen. Das RISC-Controller-Makro wurde durch die Diplomarbeit von Volker Wahl in VHDL beschrieben. Die Entwicklung der Meßeinrichtungen und der RS232-Schnittstelle sowie die Verbindung der Komponenten waren Ziel dieser Arbeit. Die einzelnen Einheiten sind durch einen 8-Bit Datenbus und entsprechenden Steuerleitungen mit dem internen RISC-Controller verbunden. Die Steuerung der Abläufe sowie die eigentliche Berechnung des Schlupfwertes sind die Aufgaben dieses RISC-Controllers. Die von den Meßeinrichtungen gelieferten Meßwerte sowie der zu übertragende Schlupfwert haben eine Breite von 16 Bit. Da für einen internen 16 Bit Bus jedoch nicht genügend Ports am Controller-Makro vorhanden sind, wurde hier der Weg über einen 8-Bit Bus mit zwei Buszyklen gewählt.

### 4. Realisierung der RS232-Schnittstelle

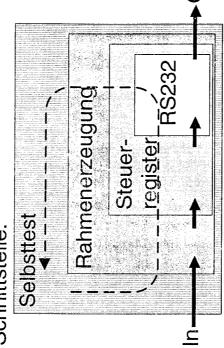

Die Aufgaben der Schnittstelle und ihre hierarchische Aufteilung in funktionale Ebenen sind in Bild 9 dargestellt. Ein wichtiges Ziel dabei war, die Schnittstelle mit einem integrierten Selbsttest und veränderbaren Übertragungsparametern auszustatten. Außerdem ist auf Bild 9 (mitte) der Datenfluß innerhalb der Schnittstelle zu erkennen. Im Normalbetrieb werden die Daten in jeder Ebene verändert und dann weitergereicht. Während des Selbsttests werden in der Testebene spezielle Daten erzeugt und durch die weiteren geschickt. Die Auswertung der Testdaten erfolgt dann wieder in der Testebene. Auf dem unteren Teil des Bildes sind außerdem zwei der Probleme die bei der Umsetzung in VHDL autraten genannt. Die Probleme

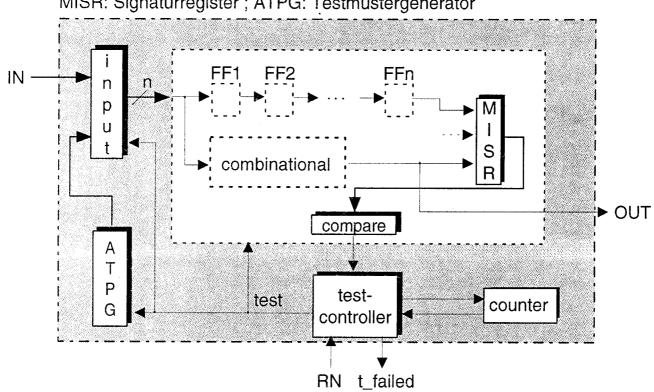

waren hauptsächlich im Bereich der Testbarkeit bzw. dem Selbsttest zu finden. Da in der Verhaltensbeschreibung noch keine genauen Aussagen über eine Realisierung durch den Synthetisierer gemacht werden können, sind Testergebnisse auf Verhaltensebene zum Teil nicht ermittelbar. Bild 10 zeigt die Schnittstelle in ihrem endgültigem Aufbau. Die Einheiten im grau unterlegten Teil des Bildes werden aussschließlich für die Testbarkeit benötigt. Durch eine Mehrfachausnutzung einzelner Register (z.B. dem Signaturregister) für den Selbsttest und für den normalen Betrieb konnte der Testaufwand hier auf etwa 30% gesenkt werden. Dieser Wert ist jedoch trotzdem noch relativ hoch.

### 5. Zusammenfassung

Bild 11 faßt die Ergebnisse dieser Arbeit in Bezug auf VHDL bzw. den WSP noch einmal zusammen. Besonders wichtig ist, daß die Schaltungen nach der Synthese bezüglich des Zeitverhaltens genau überprüft werden, da hier keine Fehlerfreiheit garantiert wird. Die kommende Aufgabe liegt nun im Test und in der Verifikation eines fertigen Musters des RISC-Controllers.

### Diplomarbeit

# Entwicklung eines Radschlupfprozessors mit der Beschreibungssprache VHDL

Roland Granzer

Institut für Mikroelektronik Stuttgart

Fachhochschule für Technik Esslingen

Betreuer am IMS:

Betreuer an der FHTE:

Dipl.-Ing. T.Büchner

Prof.Dr.Ing. G.Kampe

### Übersicht

- 1. Der Radschlupfprozessor

- 2. Einführung zu VHDL

- 3. Der Aufbau des Prozessors

- 4. Die Realisierung einer seriellen Schnittstelle

- 5. Zusammenfassung und Ausblick

# Aufgaben des Radschlupfprozessors WSP

Vermeidung von Extremsituationen bei Kraftfahrzeugen:

- präzise Messung des Radschlupfs

- Messung in festen Zeitintervallen

- Datentransfer zu zentralem Kfz-Controller

## Der WSP am Fahrzeug:

### Der ABS-Sensor:

# Gründe für eine Entwicklung im VHDL

- Standisierung durch den IEEE

- → genormter Sprachumfang

- → Unterstützung durch Softwarehersteller

- → Portabilität zwischen unterschiedlichen

- Systemen

- Umfangreiche Möglichkeiten mit VHDL

- → Verhaltensbeschreibungen

- → Netzlisten (Strukturbeschreibungen)

- → Testumgebung (Stimuli, Auswertung) alles in einer Sprache

- Schaltungsspezifikationen in VHDL

- → VHDL-Spezifikation ist simulierbar

### Beschreibungsarten in VHDL

Beispiel: D-FF mit asynchr. Reset

### 1. Die Verhaltensbeschreibung

```

FF1:

process(CLK,RES,TM)

begin

if (RES='0' and TM='0')

then Q <= '0';

elsif (CLK'event and CLK='1')

then Q <= D;

end if;

end process;</pre>

```

### 2. Die Strukturbeschreibung (Netzliste)

5

### Schaltkreisentwicklung mit VHDL

6

### Der Aufbau des Wheel-Slip-Processor

# Realisierung der RS232-Schnittstelle

Übertragung des 16-Bit Schlupfwertes in 4 Rahmen Ziel:

- Erzeugung der Rahmenbits

- Einstellbare Parameter

Parität, Stop-, Datenbits, Handshake, Baudrate)

Selbsttest

Schnittstelle:

Testbarkeit muß von Anfang an berücksichtigt werden Probleme:

In VHDL vor der Synthese kein Zugriff auf Register von Schaltwerken (FSM's)

### Realisierung der RS232-Schnittstelle

MISR: Signaturregister; ATPG: Testmustergenerator

# **Zusammenfassung und Ausblick**

### Zu VHDL:

- Schaltungsentwicklung in VHDL mit anschl. Synthese vereinfacht die Umsetzung in Netzlisten

- Syntheseergebnisse müssen genau überprüft werden

- Änderungen sind in VHDL schneller durchführbar

- Testbarkeit von Anfang an berücksichtigen

- Beispiel für eine selbsttestende Schaltung in VHDL.

### Zum WSP:

- Ein einziger Chip für Messung, Berechnung und Ausgabe des Schlupfwertes

- Vielseitig einsetzbar durch progr. Mikrocontroller

- Alle Einheiten des Chips als VHDL-Beschreibung vorhanden → weiterverwendbar

- kommende Aufgabe: Test + Verifikation des Controllers an einem fertigen Muster

=

### Entwurf und Realisierung einer ASICbasierenden opto-elektronischen Busschnittstelle

Dipl.-Ing. Heinz Berl Prof. Dr.-Ing. N. Höptner Prof. Dr. G. Krieg Dipl.-Ing. A. Larsch

IIT der Fachhochschule Karlsruhe

Dieses Projekt wurde im Zeitraum 1.1.91 bis 31.3.93 bearbeitet. Es wurde mit Personalmitteln für 3 Mannjahre aus dem Schwerpunkt-programm gefördert. Weiterhin wurde die ASIC-Herstellung im Rahmen des Budgets der MPC-Gruppe durchgeführt.

### <u>Projektziele:</u>

- für den Anwender einfache Busschnittstelle mit möglichst hoher Datenrate

- Verwendbarkeit von Lichtwellenleitern und Kupferleitern

- adressierbare Busteilnehmer (mindestens 256)

- faires Buszuteilungs-Konzept: Echtzeitfähigkeit

- flexible Austauschbarkeit von Kosten gegen Übertragungsrate ohne Änderung der Kernhardware

- integrierte Kernhardware

- Vergleich der Leistungsfähigkeit ASIC LCA

### Systemkonzept

Zur Anwendung gelangt das DQDB - Zugriffsverfahren (DQDB - Distributed Queue Dual Bus).

Bussystem - Übersicht:

## Bus-Zugriffsverfahren

Wenn eine Station senden will, so setzt sie im Datenstrom der entgegengesetzten Übertragungsrichtung ein freies Requestfeld und signalisiert somit allen vor ihr liegenden Stationen ihren Sendewunsch.

Anhand des Zählerstandes in der eigenen Station ist sie über die Anzahl der Sendewünsche aller nach ihr liegenden Stationen informiert.

Bevor sie nun einen freien Datenrahmen belegt, läßt sie zuvor so viele freie Datenrahmen passieren. wie zum Zeitpunkt des Zugriffwunsches im Zähler gespeichert waren.

Damit ist gewährleistet, daß ohne Arbiter eine gleichmäßige Verteilung der Bandbreite an alle senden wollende Stationen erfolgen kann.

Das folgende Bild zeigt die Struktur einer dafür realisierten Busschnittstelle, wie sie in einem ASIC nun implementiert werden muß.

Der Datenrahmen hat folgenden Aufbau:

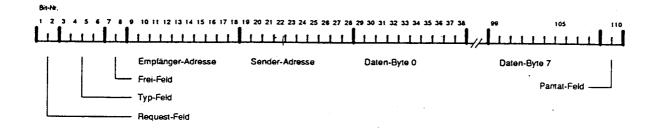

Damit ergibt sich ein Nutzdatenraten-Anteil von 64 bit / 110 bit - 58%. (Beipiel: Bei 50 Mbit/s ----> 29 Mbit/s)

# Weiteres Vorgehen:

Zur Zeit wird eine Demonstrationssystem realisert, daß

- die Adressierbarkeit und

- die effektive Datenrate

unter Beweis stellen soll. Natürlich wird damit ebenfalls die volle System-Funktionsfähigkeit nachgewiesen.

Gleichzeitig geben wir damit potentiellen Anwendern eine Vorstellung von der Komplexität einer anwenderspezifischen Schaltung.

Dieses Demonstrationssystem soll von einem PC zu mehreren anderen PCs adressierbar auswählbare Bilder übertragen.

## System-Merkmale:

- 50 MBit/s Brutto- 29 MBit/s Netto-Übertragungsrate

- freie Adressierbarkeit

- 2 256 Stationen

- gleiche Bandbreitenverteilung auf alle Stationen (DQDB-Verfahren)

- echtzeitfähig

- parallele Schnittstelle, 8 64 Bit breit konfigurierbar

- automatische Initialisierung und Einsynchronisation aller Stationen nach dem Einschalten

- automatische Fehlererkennung und Auftrennung des Bussystems an der Fehlerstelle

- automatische Neuinitialisierung nach Beseitigung des Fehlers

- 8/10-Codierung für ausbalancierten, seriellen Datenstrom

- Service und Diagnoseschnittstelle

- optionale elektrische serielle Übertragung

## **DQDB** Funktionsprinzip

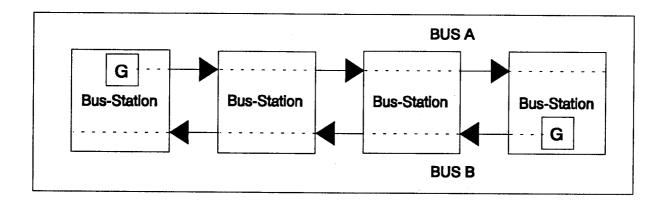

Das Funktionsprinzip des opto-elektronischen Bussystems wurde aus dem DQDB-Zugriffsverfahren abgeleitet. Dieses Verfahren befindet sich zur Zeit in der Normung und ist für den Einsatz in MAN's (Metropolitan Area Networks) gedacht. DQDB steht für "Distributed Queue Dual Bus" (Verteilte Warteschlange, Doppel-Bus). Es handelt sich dabei um ein deterministisches Zugriffsverfahren, wie es beispielsweise für Echtzeitsysteme benötigt wird.

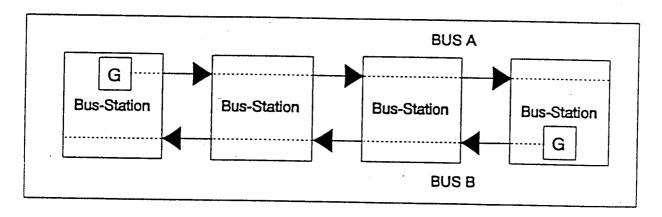

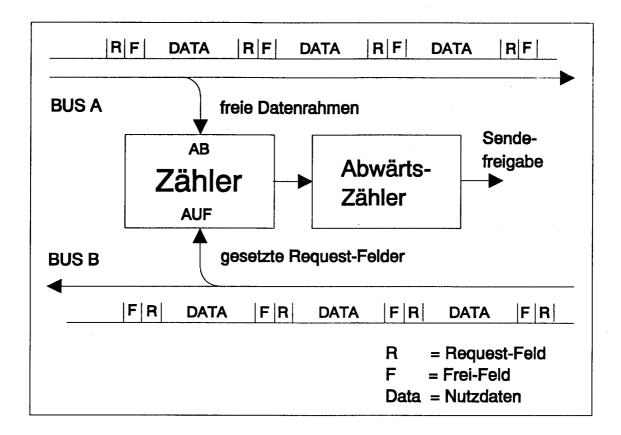

In Bild 1 ist der prinzipielle Aufbau eines solchen Systems dargestellt. Bei diesem Verfahren werden zwei entgegengesetzt gerichtete Übertragungsstrecken, hier als BUS A und BUS B bezeichnet, verwendet. Die Busstationen, die sich am Anfang der Übertragungsstrecken befinden, erzeugen über einen hier mit G bezeichneten Generator einen Datenstrom, der aus kontinuierlich aufeinanderfolgenden Datenrahmen besteht (siehe Bild 3).

Bild 1: Bustopologie

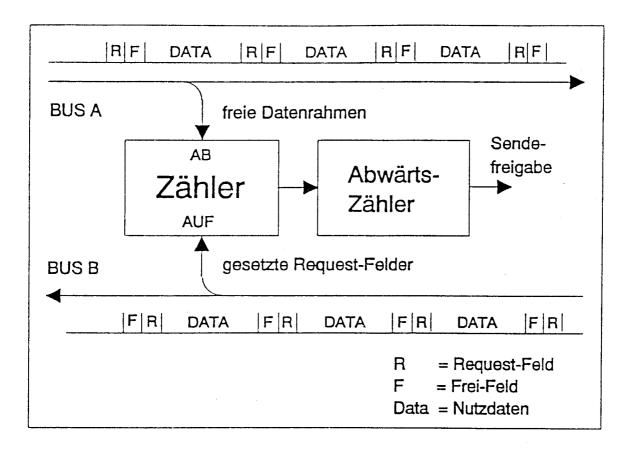

Jeder Datenrahmen enthält neben den eigentlichen Nutzdaten Steuerinformationen, über die der Zugriff geregelt wird. So gibt es ein Feld über das signalisiert wird, ob der Datenrahmen frei ist oder ob er gültige Daten enthält. Weiterhin enthält jeder Rahmen ein sogenanntes Request-Feld, durch das eine Datenübertragung initialisiert werden kann.

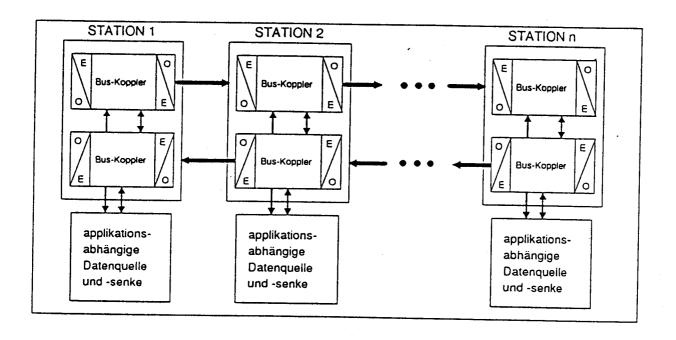

Jeder Teilnehmer am Bus (Busstation) ist mit beiden Übertragungsrichtungen verbunden und hört diese Datenströme ständig ab. In jeder dieser Busstationen existiert nun für jede Übertragungsrichtung jeweils ein Zähler, der durch passierende freie Datenrahmen dekrementiert und durch gesetzte Request-Felder im Datenstrom der Gegenrichtung inkrementiert wird (siehe Bild2).

Bild 2 : Die Zähler der verteilten Warteschlange

Wenn eine Station senden will, so setzt sie im Datenstrom der entgegengesetzten Übertragungsrichtung ein freies Request-Feld und signalisiert somit allen vor ihr liegenden Stationen ihren Sendewunsch. Anhand des Zählerstandes in der eigenen Station ist sie über die Anzahl an Sendewünsche der nach ihr folgenden Stationen informiert.

Bevor sie einen freien Datenrahmen belegt, läßt sie deshalb soviele freie Datenrahmen passieren, wie zum Zeitpunkt des Requestsetzens durch den Zähler angezeigt wurden. Hierzu ist ein Abwärtszähler vorhanden, der mit dem Inhalt des Zählers zum Zeitpunkt des Setzens des Request-Feldes geladen wird und dann durch jeden passierenden freien Datenrahmen dekrementiert wird. Auf diese Art und Weise ist gewährleistet, daß die zur Verfügung stehende Bandbreite gleichmäßig auf alle sendewilligen Stationen verteilt wird.

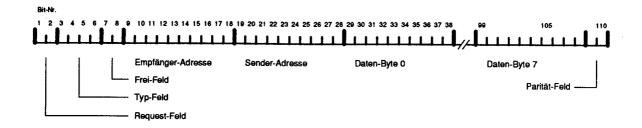

Das für das opto-elektronische Bussystem festgelegte Format des Datenrahmens ist in Bild 3 dargestellt. Ein Datenrahmen besteht aus 110 Bit und beinhaltet neben Kontrollinformationen die Empfänger- und Sender-Adresse sowie 8 Datenbytes. Hieraus ergibt sich eine Nutzdatenrate von 58 %. Neben den bereits erwähnten Frei- und Request-Feldern ist in den Kontrollinformationen ein Paritäts-Feld enthalten, mit dem es möglich ist, Ein-Bit Fehler zu erkennen.

Bild 3: Format des Datenrahmens

Ein weiteres sogenanntes Typ-Feld bietet außerdem die Möglichkeit, einzelne Datenrahmen von dem beschriebenen Zugriffsverfahren auszunehmen und für Sonderaufgaben zu verwenden. Das Typ-Feld kann 6 verschiedene Zustände annehmen, so daß bis zu 5 solcher besonderen Buszuteilungsmöglichkeiten realisiert werden können.

Eine mögliche Sonderaufgabe ist es zum Beispiel, daß eine Station einen speziell gekennzeichneten Datenrahmen (Typ + eigene Stationsadresse) immer belegen darf. Je nachdem wie oft solche Rahmen von der Kopfstation generiert werden, kann einer oder mehreren Stationen daduch eine feste Übertragungsbandbreite zugeordnet werden. Die verbleibende Bandbreite verteilt sich dann wieder gleichmäßig auf die verbleibenden Stationen.

Von der als Kopfstation arbeitenden Station werden zusätzlich zu den Datenrahmen zyklisch Synchronisationszeichen ausgesendet, anhand derer die folgenden Stationen Übertragungsfehler erkennen können und sich dann neu auf den Datenstrom synchronisieren.

Im Fall einer Unterbrechung in der Übertragungsstrecke übernimmt die Station hinter der Unterbrechungsstelle die Funktion der Kopfstation. Der Bus zerfällt dadurch in zwei Teil-Busse, die jedoch für sich jeweils voll funktionsfähig sind.

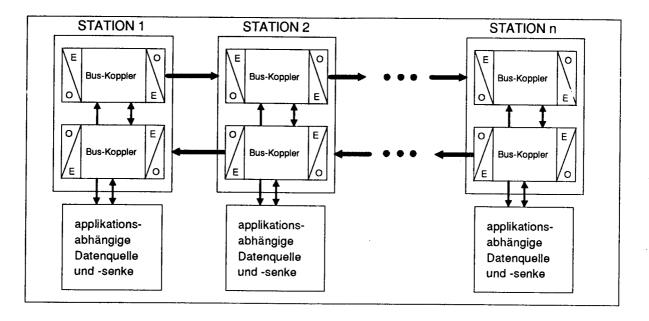

Das Bussystem besitzt eine Schnittstelle zur anwenderspezifischen Datensenke- oder Quelle, die sich in ihrer Busbreite flexibel konfigurieren läßt. Es sind Busbreiten von 8, 16, 32 und 64 Bit einstellbar. Bild 4 gibt eine Bussystem-Übersicht an.

Bild 4: Systemübersicht

Wie vorher erwähnt, kann der Datenübertragungsrahmen eine Empfänger- und eine Sender-Adresse enthalten. Werden diese mit je 8 Bit codiert, so lassen sich bis zu 256 Busteilnehmer adressieren.

Das Übertragungsmedium muß nicht notwendigerweise ein Lichtwellenleiter sein. Bei Einsatz des selben Verfahrens und auch der gleichen Bausteine lassen sich kürzere Übertragungsstrecken bzw. solche mit geringerer Datenrate auch kostengünstiger mit Kupferkabel realisieren.

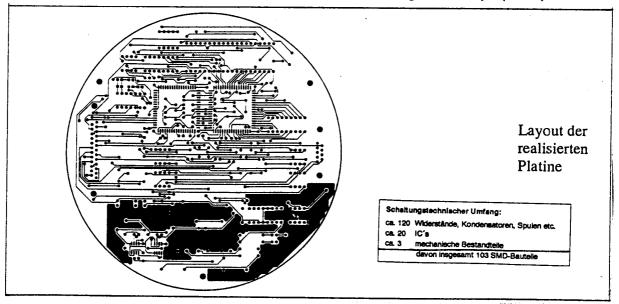

## **Kurzbeschreibung Optobus-Leiterplatte**

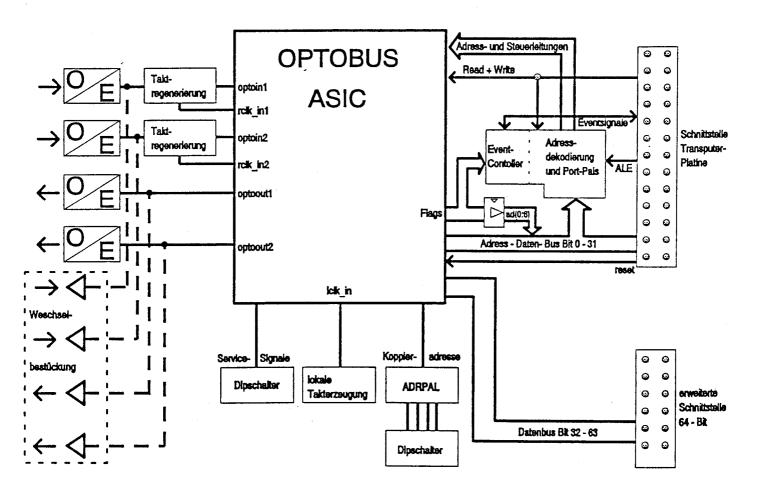

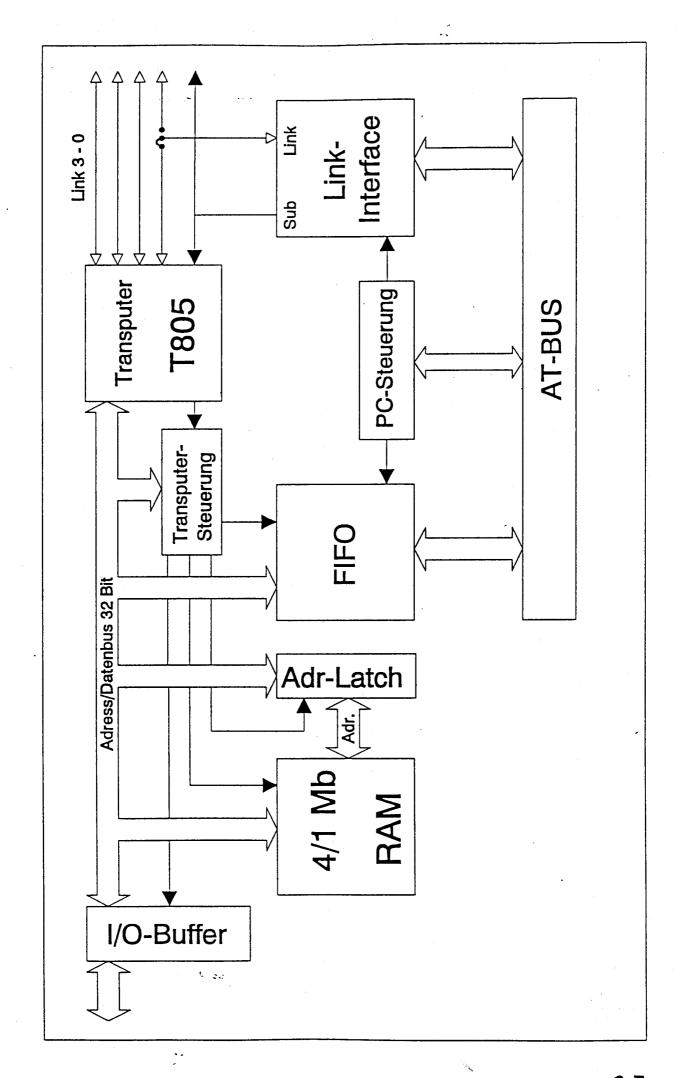

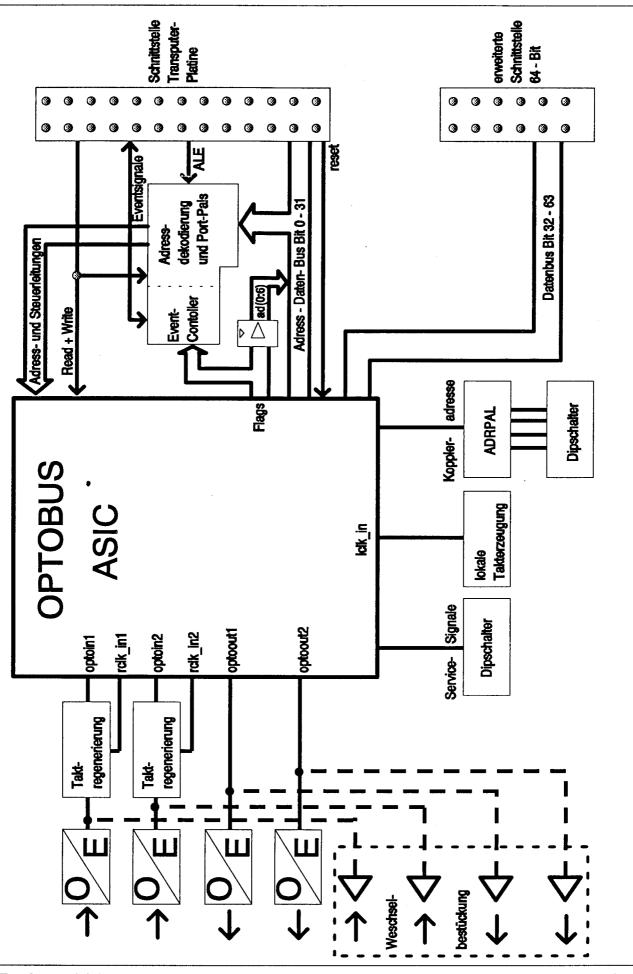

Auf der seriellen Seite haben wir bei optischem Medium vier Wandler, für jede Richtung einen Empfänger und einen Sender. Als Wechselbestückung kann man stattdessen Bustreiber einsetzen, und über Koaxleitung übertragen. Die eingehenden Daten werden über einen Taktregenerator geführt, der daraus den Systemtakt zurückgewinnt, und die Daten wieder auffrischt. Über Schalter einstellbar sind Servicesignale, die den Buskoppler in einen bestimmten Modus zwingen, und zur Diagnose dienen. Für den Betrieb als Generator, wird der Systemtakt von einem Quarzoszillator erzeugt. Über einen weiteren Schalter wird die 8Bit Adresse jedes Kopplers eingestellt, die während der Initialisierung seriell eingetaktet wird. Als Steuerndes System, auf dem auch unser Demo laufen wird, haben wir ein B008 Kompatibles Transputerboard, mit PC-Schnittstelle entwickelt. Die Optobus-Platine besitzt eine Schnittstelle zu diesem Transputerboard. Vom A/D-Bus dieses 32Bit-Systems dekodieren wir alle Steuersignale aus, und können den Optobus ansprechen, als wäre er ein Speicherbereich des Transputers. Außerdem können vom Optobus aus Events am Transputer ausgelöst werden, und vom Transputer aus kann man die Flags, die den Zustand des Asic anzeigen, auslesen.

## **Kurzbeschreibung Optobus-Asic**

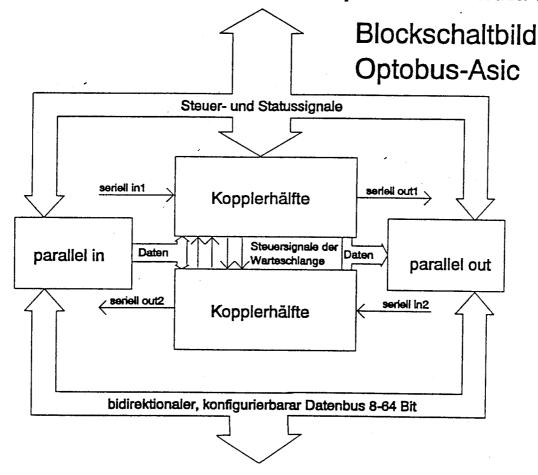

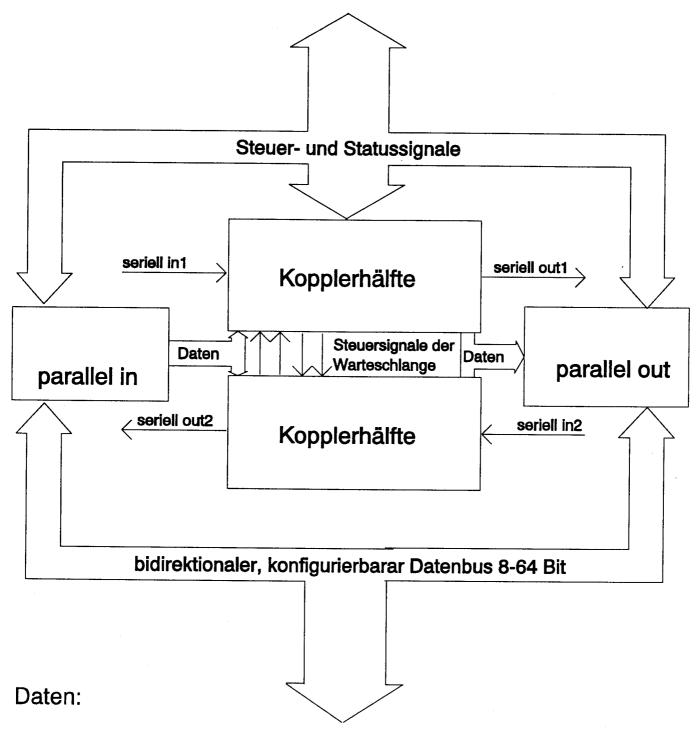

Das Blockschaltbild zeigt die Aufteilung der Funktionen im Optobus-Asic.

Wir haben eine parallele Schnittstelle für von außen eingehende Daten, und eine für nach außen gehende Daten. Diese Schnittstellen greifen beide auf den bidirektionalen Bus zu, der durch von außen angelegte read/write-Signale in der Richtung umgeschaltet wird. Außerdem haben wir eine Reihe von Signalen, die von außen die Funktionen des Asic steuern, sowie Statussignale, die z.B. den Kopplermodus oder Datenempfang anzeigen. Für jede Richtung ist eine Kopplerhälfte vorhanden, die unabhängig und asynchron zur gegenüberliegenden läuft. Die Steuerung der Warteschlange wird über Signale im Handshake-Verfahren geregelt.

Aufgrund der Busbreite von 64Bit mußten wir ein 144 Pingrid-Array-Gehäuse wählen, das wir auch bis auf den letzten Pin ausgereizt haben. Der GF2G1-Master der von uns verwendet wurde stellt ca. 13500 Gatterfunktionen zur Vefügung, wovon wir 9600 Gatterfunktionen verwendeten. Das entspricht 53000 aktiven Transistoren, und einer Ausnutzung von 76%. Damit liegen wir noch 4% unter den Vom IMS vorgeschlagenen 80%, und hätten also noch Platz gehabt die eine oder andere Idee zu verwirklichen, was aus Zeitgründen aber leider unmöglich war.

Dr.Ing. N.Höptner

Dipl.Ing. A.Larsch

# **Blockschaltbild Optobus-Asic**

144 PGA-Gehäuse9600 Gatterfunktionen53000 aktive Transistoren76% Ausnutzung

# Produktion eines ASIC beim Institut für Mikroelektronik Stuttgart

IIT

-Erzeugung einer EDIF-Netzliste, eines Pin-Files, eines Supersynchronous-Tracefiles und eines At-Speed-Tracefiles nach den Richtlinien des IMS

- IMS -Übersetzung der EDIF-Netzliste in das Format des IMS

- -Erstellung der statistischen Daten (Ausnutzung etc.)

- -Prüfung der Netzliste

- -Übersetzung der Tracefiles und deren Prüfung

- -Extraktion von Stimulifiles aus den Tracefiles

- -(Fehlersimulation)

- -> Simulation der Schaltung beim IMS -> Erzeugung eines Tracefiles -> Vergleich mit unserem Tracefile

Freigabe der Netzliste

- -Platzieren und Routen der Schaltung

- -Extraktion einer Netzliste mit realen Kapazitäten

- -Vergleich dieser, mit unserer Netzliste (Logiktest)

- -Design-Rule-Check

- -Postroutesimulation und erneuter Vergleich mit unseren Tracefiles

Layout-Freigabe und Produktion

- -Wafertest: Stromaufnahme, Anlegen der Stimuli

- -> Vergleich mit unseren Simulationsergebnissen

- -Gut-Schlecht-Auswahl aller Chips

- -Verpackung der guten Chips

- -Test der IC bei Betriebsfrequenz

Auslieferung der ASIC

# Baustein zur Datenverschlüsselung

Bearbeiter

: Peter Jonski

**Fachbereich**

: Industrieelektronik

**Betreuer**

Prof. A. Führer

Fachhochschule:

Ulm

## TABLE OF CONTENTS

| Section 1                                                                                                                                                                                                                                                                    |                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Vorwort                                                                                                                                                                                                                                                                      | 1-1                                    |

| 1.1 Thema der Diplomarbeit                                                                                                                                                                                                                                                   | 1-1                                    |

| Section 2                                                                                                                                                                                                                                                                    |                                        |

| Einfuehrung zum verwendeten Chiffrieralgorithmus                                                                                                                                                                                                                             | 1-1                                    |

| 2.1 Historie 2.2 Schnelle Blockchiffrierverfahren 2.2.1 Ablauf einer Verschluesselung 2.2.2 Einsatz eines Schluessels 2.2.3 Erhoehung der Datensicherheit durch Weisses Rauschen 2.2.4 Die Chiffrierfunktionen 2.2.5 Vorgehen bei der Entschluesselung 2.3 Anwendungsgebiete | 2-1<br>2-1<br>2-2<br>2-2<br>2-3<br>2-5 |

| Section 3                                                                                                                                                                                                                                                                    |                                        |

| Umsetzung des Algorithmus in einen Integrierten Schaltkreis                                                                                                                                                                                                                  | 3-1                                    |

| 3.1 Aufteilung in funktionale Gruppen 3.2 Aufbau und Wirkungsweise der Funktionseinheiten 3.2.1 Das Businterface 3.2.2 Die Register 3.2.3 Die Chiffriereinheit                                                                                                               | 3-2<br>3-2<br>3-2                      |

| Section 4                                                                                                                                                                                                                                                                    |                                        |

| Realisierung der Schaltung                                                                                                                                                                                                                                                   | 4-1                                    |

| 4.1 Technologie 4.2 Das CADENCE Entwicklungssystem 4.3 Testmoeglichkeiten des Bausteins 4.4 Simulation 4.4.1 Erstellen von Simulationsdateien mit SKILL 4.4.2 Ablauf der Simulation 4.5 Zusammenfassung                                                                      | 4-1<br>4-2<br>4-2<br>4-2               |

| Fa | achhoch | ischule | Ulm      |              |            |

|----|---------|---------|----------|--------------|------------|

| P. | Jonski  | : Baus  | tein zur | Datenverschl | luesselung |

2/18/93

## **LIST OF FIGURES**

| 1. | Vergleich Bit-stream-Ciphering und Block-Ciphering           | 1-1 |

|----|--------------------------------------------------------------|-----|

| 2. | Prinzipieller Ablauf einer Chiffrierung mit K=1              | 2-1 |

| 3. | Aufbau einer Runde mit Schluessel und Schluesselmanipulation | 2-3 |

| 4. | Abbildung und Transposition                                  | 2-4 |

| 5. | Reihenfolge der Chiffrierfunktionen                          | 2-6 |

| 6. | Blockdarstellung des DEP                                     | 3-1 |

| 7. | Aufbau der Chiffriereinheit                                  | 3-3 |

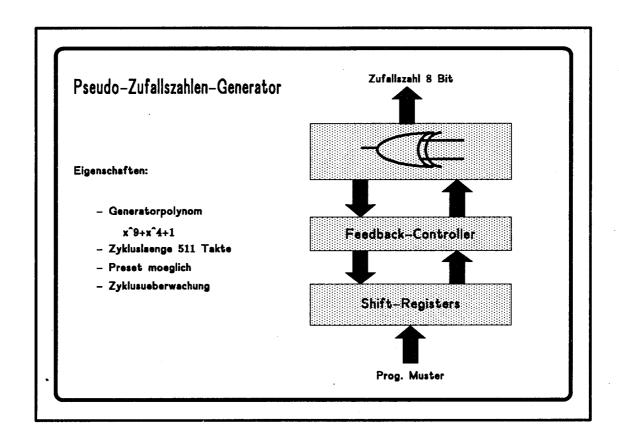

| 8. | Pseudo-Zufallszahlen-Generator                               | 3-4 |

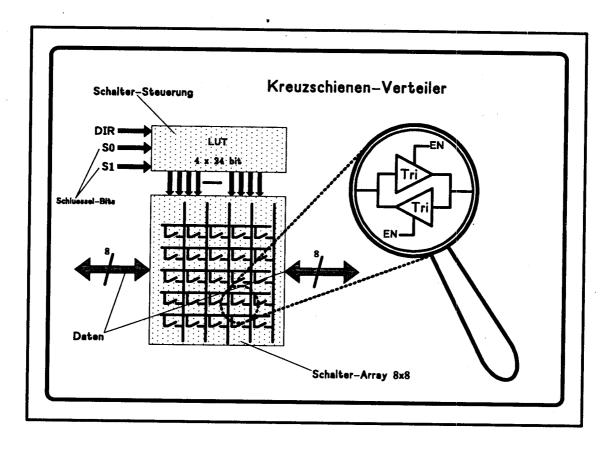

| 9. | Kreuzschienen-Verteiler 8x8 Leitungen                        | 3-5 |

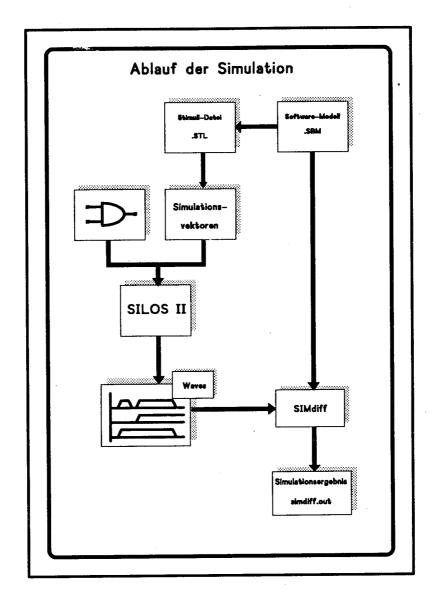

| 10 | Ablauf der Simulation                                        | 4-3 |

## 1. Vorwort

## 1.1 Thema der Diplomarbeit

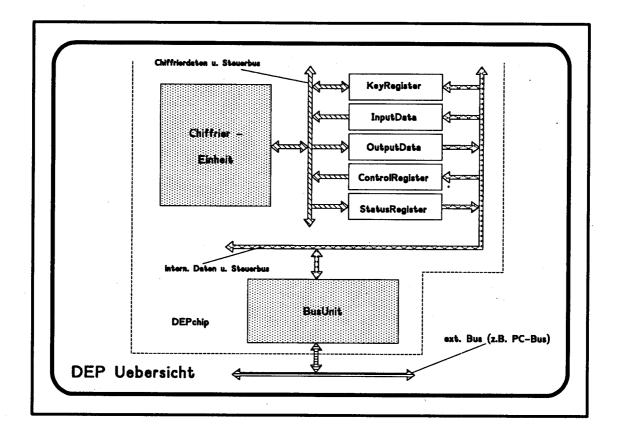

Das Thema der Diplomarbeit war der Entwurf eines integrierten Bausteins zur Datenverschlüsselung nach einem kryptografischen Verfahren.

Dieser Chip wurde als Peripheriebaustein konzipiert und arbeitet in einem IBM PC AT oder Kompatiblen mit der Mikroprozessorfamilie 80x86 zusammen. Der Data Encryption Processor (DEP) kann Daten sowohl ver- als auch entschlüsseln. Er ist in der Lage seine Daten entweder mit dem Hostprozessor auszutauschen, kann jedoch auch mit dem Plattform DMA-Controller zusammenarbeiten. Der Prozessor verarbeitet seine Daten im Binärformat und unterscheidet keine anderen Formate. Die Wortbreite des Prozessors beträgt 8 Bit.

## 2. Einfuehrung zum verwendeten Chiffrieralgorithmus

### 2.1 Historie

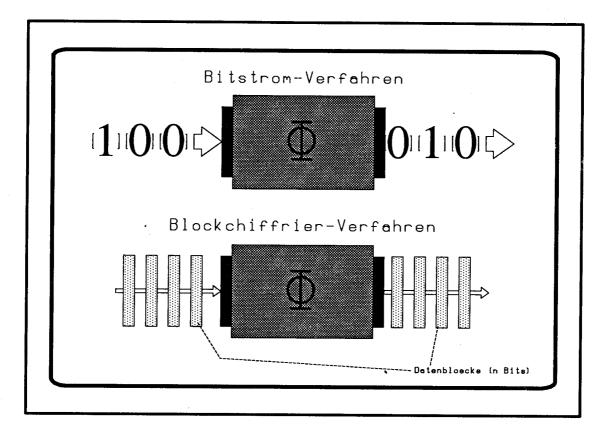

Bei dem verwendeten Chiffrieralgorithmus handelt es sich um ein sogennantes Blockchiffrierverfahren.

Im Gegensatz zu Bit-stream-Verfahren, bei denen ein kontinuierlicher Bitstrom kodiert wird, werden bei diesem Verfahren immer mehrere Bits parallel chiffriert. Das Verfahren gehört zu den klassischen Chiffriermethoden.

Abb. 1 Vergleich Bit-stream-Ciphering und Block-Ciphering

Vor zwei Jahren wurde der Algorithmus von der kryptografischen Abteilung der Universität Ulm unter der Leitung von Prof. Dr. Trautner in seinem Geschwindigkeitsverhalten entscheidend verbessert. Die Abteilung entwickelte ein allgemeines Designkonzept unter dem Namen 'Schnelles Blockchiffrierverfahren oder RNK-Design', das sich durch eine hohe Flexibilität bei der Umsetzung in Hardware auszeichnet. Dieses Verfahren ist bereits zum Patent angemeldet.

Durch die Wahl der Parameter R, N und K kann der Entwickler entscheiden, ob ein Design zeitoptimales oder hardwareoptimales Verhalten zeigen soll.

Für den von mir entworfenen Chip wurde die hardwareoptimale Lösung ausgewählt.

### 2.2 Schnelle Blockchiffrierverfahren

## 2.2.1 Ablauf einer Verschluesselung

Prinzipiell ist der Ablauf einer Verschlüsselung beim zeitoptimalen und beim hardwareoptimalen Design gleich.

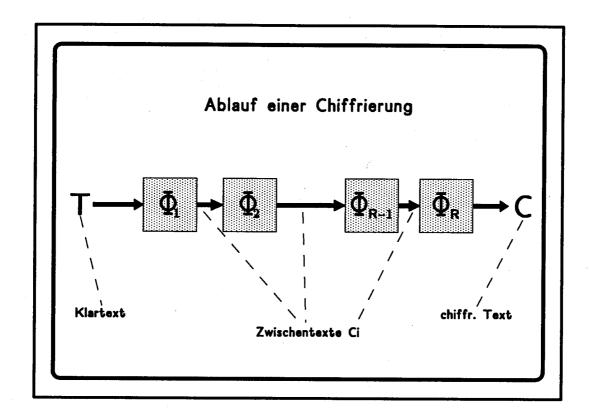

Bei der Chiffrierung durchläuft der Klartext T mehrere Runden R. In jeder Runde wird eine eindeutige Funktion  $\phi$  aus N-Funktionsblöcken insgesamt K-mal auf den Text angewendet. Daraus folgt die gesamte Funktion nach R Runden:

$$\Phi = \phi^{\mathsf{K}}_{1} * \phi^{\mathsf{K}}_{2} * \phi^{\mathsf{K}}_{3} * \dots * \phi^{\mathsf{K}}_{\mathsf{R}}$$

wie das folgende Bild verdeutlicht:

Abb. 2 Prinzipieller Ablauf einer Chiffrierung mit K=1

Jede Funktion of führt eine äußerst einfache Operation mit den Daten durch.

Trotzdem ergibt ihre Verkettung eine sehr komplizierte Funktion. In der ersten Runde erzeugt eine Funktion aus dem Klartext T einen Zwischentext  $C_1$ .

$$C_1 = T^* \phi^K_1$$

In jeder weiteren Runde wird aus dem Zwischentext  $C_i$  der Zwischentext  $C_{i+1}$  und in der letzten Runde schließlich der chiffrierte Text C erzeugt.

$$C = C_{R-1} * \phi^{K}_{R}$$

Die Zwischentexte C<sub>i</sub> sind von außen nicht beobachtbar.

Jede Verschlüsselungsfunktion besteht aus einer Anzahl verschiedenartiger <u>Tauschfunktionen</u>. Im vorliegenden Fall wird sie aus einer <u>Abbildung</u> und einer <u>Transposition</u> gebildet:

$$\phi_i = d_i * t_i d_i = Abbildung, t_i = Transposition$$

Um einen kleinen Harwareaufwand zu erzielen, sollte R und N möglichst klein gewählt werden. Die Anzahl der Wiederholungen K muß dann allerdings genügend groß sein, um eine ausreichende Permutation der Daten zu gewährleisten. Aus diesen Gründen entschieden wir uns für die Werte R=1, N=2 und K=16.

### 2.2.2 Einsatz eines Schluessels

Die Auswahl der Permutationsfunktionen in einer Runde geschieht mit Hilfe eines Schlüssels, der von dem Benutzer vor der Ver- bzw. Entschlüsselung angegeben wird. Anstelle eines statischen Sclüssel verwendet das RNK-Design einen zeitabhängigen Schlüssel. Nach jeder Wiederholung in einer Runde wird dieser Schlüssel, wie der Text, mittels einer Funktion modifiziert.

Die Permutation des Schlüssels geschieht mit Hilfe einer Tauschfunktion. Ob der verschlüsselte Text oder der Klartext jeweils zur Auswahl einer Permutation benutzt werden soll, bleibt dem Designer überlassen. In diesem Design wurde zur Modifizierung des Schlüssels der erzeugte Zwischentext verwendet.

Durch die Verknüpfung von Text und Schlüssel erreicht man, daß sowohl Text als auch Schlüssel voneinander abhängig sind.

Die erforderliche Länge des Schlüssels ist von der Anzahl der Wiederholungen pro Runde und von der Anzahl der verschiedenen Tauschfunktionen abhängig. Im vorliegenden Fall stehen zwei unterschiedliche Funktionen zur Auswahl. Eine Abbildung und eine Transposition. Bei beiden Funktionsarten ist die Auswahl zwischen vier verschiedenen Abbildungen und Transpositionen möglich. Deshalb benötigt man zur Auswahl der Tauschoperationen insgesamt 4 Bit. Da in unserem Entwurf jede Runde 16 mal durchlaufen wird, ergibt sich die Schlüssellänge zu 16\*4 Bit = 64 Bit.

## 2.2.3 Erhoehung der Datensicherheit durch Weisses Rauschen

Da die Schlüsselinformation mit dem chiffrierten Text kodiert wird und nicht explizit zur Verfügung steht, muß ein Unbefugter den Startschlüssel herausfinden um den Klartext sichtbar zu machen. Eine Möglichkeit den Schlüssel herauszubekommen wäre, das System wiederholt mit der Eingabe von unterschiedlichen Schlüsseln zu

starten, und die Anfangsblöcke des verschlüsselten Textes zu entschlüsseln. Dieser Versuch könnte solange wiederholt werden, bis der richtige Schlüssel gefunden worden ist.

Um diese Angriffsmöglichkeit zu vereiteln verfährt man wie folgt:

Beim Start verschlüsselt der DEP erst eine Reihe von Zufallszahlen, die er intern erzeugt. Erst danach verschlüsselt er Daten, die vom Benutzer geliefert werden. Die verschlüsselten Zufallszahlen werden vom Prozessor nicht verworfen, sondern vor den verschlüsselten Daten abgelegt, da sie später zur Entschlüsselung benötigt werden.

Bei der Datenentschlüsselung dechiffriert der Prozessor zuerst die, vor der eigentlichen Information abgelegten, chiffrierten Zufallszahlen und verwirft sie danach. Anschließend dechiffriert er die verschlüsselten Nutzdaten.

Mit dieser Methode wird das erste Datum eines Benutzers immer mit einem bereits durch Zufallszahlen permutiertem Schlüssel chiffriert. Da die Zufallsmuster dem Benutzer nie als Klartext sichtbar werden, kann der Schlüssel nicht durch Angriffe mit unterschiedlichen Texten rekonstruiert werden.

Mit dieser Methode wird ein Angriffsversuch noch weiter erschwert.

#### 2.2.4 Die Chiffrierfunktionen

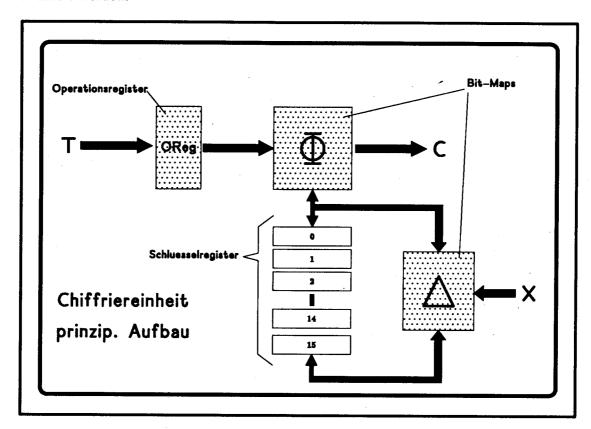

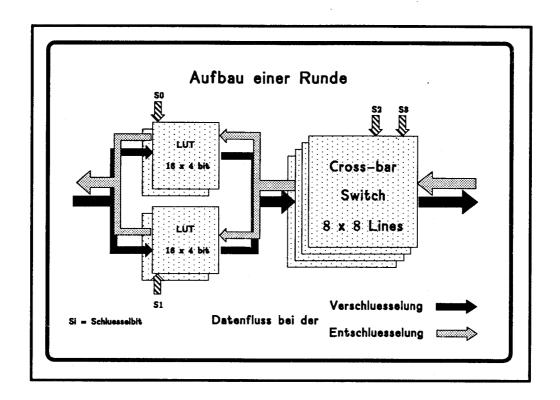

Im folgenden Kapitel soll der Aufbau einer Runde anhand von Bild 3 genauer erläutert werden.

Abb. 3 Aufbau einer Runde mit Schluessel und Schluesselmanipulation

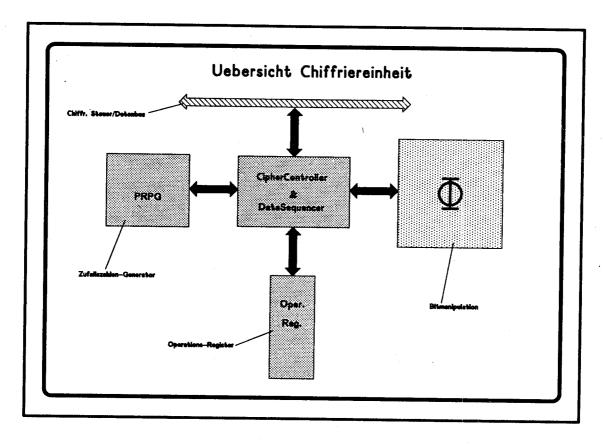

Jede Runde besteht aus einem Operationsregister und einer Baugruppe, in der das Datum manipuliert wird. Diese Einheit enthält die Chiffrierfunktion.

Zu Beginn jeder Runde wird das Datum in das Operationregister geladen. Mit jedem

Rechenschritt durchläuft der Inhalt des Operationsregisters die Manipulationseinheit (Abb. 4), in der die Tauschfunktionen ablaufen. Das Ergebniss von jedem Rechenschritt wird anschließend zurück in das Operationsregister geschrieben. Dabei entscheidet der momentane Schlüssel darüber welche Kombination der verschiedenen

2/18/93

Tauschfunktionen ausgewählt wird. Dieser Vorgang wird nun K mal wiederholt. Mit jeder Wiederholung rotiert der Schlüssel um ein Schlüsselsegment weiter und das vorherige Segment wird ebenfalls durch eine Funktion modifiziert. Für den Aufbau dieser Funktion kann im Prinzip der gleiche, wie für die Datenmanipulation gewählt werden. Sie kann aber auch einfacher oder komplizierter sein. Der Ablauf der Schlüsselchiffrierung entspricht dem Ablauf der Datenmanipulation. Die Auswahl der Tauschfunktion für den Schlüssel geschieht in diesem Fall durch Datenbits.

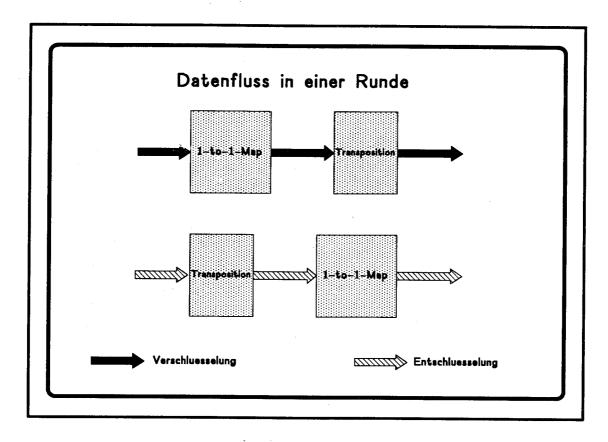

Abb. 4 Abbildung und Transposition

Die Tauschfunktion besteht aus einer Abbildung und einer Transposition. Innerhalb einer Verschlüsselungsrunde durchlaufen die Daten zuerst die Abbildung, und dann die Transposition. Dabei wählt ein Teil des Schlüssels je eine Abbildung und eine Transposition aus einer Anzahl von Abbildungen und Transpositionen aus.

Da es sich bei der Abbildung und Transposition um sehr einfache Funktionen handelt, werden sie auch Elementaroperationen genannt. Ihre Aufgabe ist die Manipulation eines Datenwortes. Alle Datenworte sind Elemente des Zahlenraumes  $Z_2E$ . Dabei ist E die Wortbreite in Bits. Man fordert nun, daß eine Elementaroperation jedes Datum wieder in den Raum  $Z_2E$  abbildet. In diesem Fall entspricht E=8, da die Wortbreite des Prozessors 8 Bit beträgt.

## Die e-Bit-Abbildung:

Der Datenblock wird in E/e e-Bit-Blöcke aufgeteilt. Mit jedem dieser Blöcke werden m Abbildung durchgeführt (m=2). Dies geschieht mit Hilfe von

Permutationstabellen. Von der Abbildung wird gefordert, daß sie eindeutig ist, d.h. jeder Eingangskombination darf nur eine Ausgangskombination zugewiesen werden. Außerdem muß sie bijektiv sein.

Damit die Permutationstabellen nicht zu groß werden, ist im vorliegenden Fall e=4 gewählt worden. So erhält man Tabellen mit 2<sup>4</sup>=16 Werten zu 4 Bit. Für jeden e-Bit-Block wird durch ein Schlüsselbit ausgewählt, welche Abbildung weiter verwendet wird. Somit sind für die e-Bit-Abbildung im vorliegenden Fall 2 Schlüsselbit erforderlich.

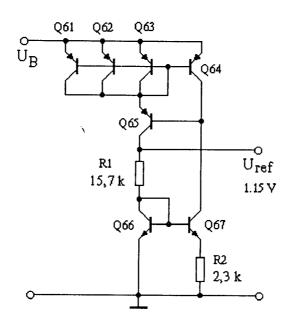

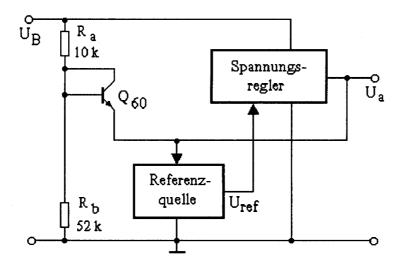

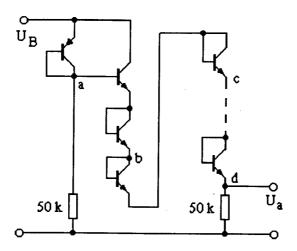

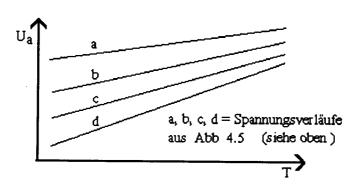

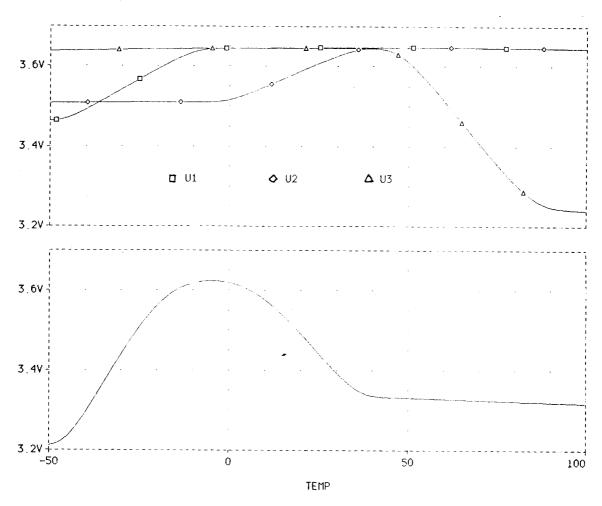

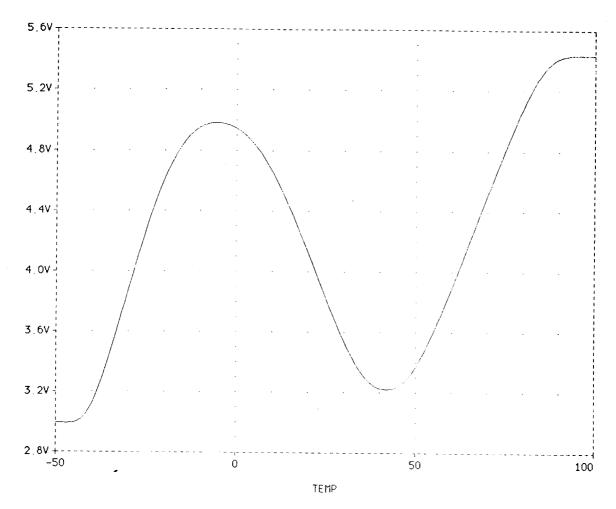

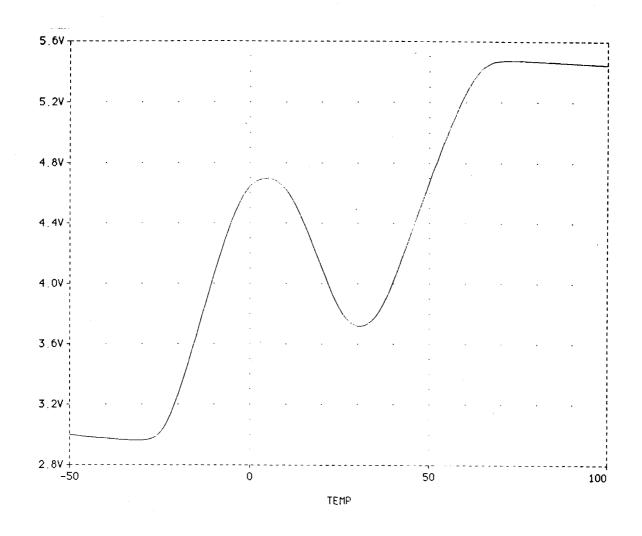

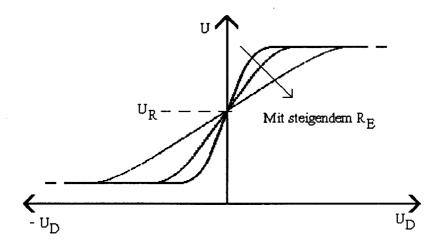

## Die E-Bit-Transposition: