Herausgeber: Hochschule Mannheim Ausgabe: 56/57 ISSN 1868-9221

Workshop: Ravensburg-Weingarten Juli 2016 Workshop: Albstadt-Sigmaringen Februar 2017

Band 56 Workshop: Ravensburg-Weingarten Juli 2016

### 1 Entwicklung eines intelligenten autonomen Fahrzeugs Dustin Braun, Robin Braun, Christian Epe, Bernhard M. Rieß Hochschule Düsseldorf

- 13 Delay-Line Analog-Digital-Wandler mit geringer Latenzzeit für digital geregelte Schaltwandler Samuel Quenzer-Hohmuth, Cedric Jiago, Steffen Ritzmann, Thoralf Rosahl, Bernhard Wicht Hochschule Reutlingen

- 19 Entwicklung eines Feldbusmoduls "CAN" für eine neue Industriesteuerungsgeneration "IndraControl XM"

Mirko Auth

Hochschule Offenburg

- 25 Modulares Test- und Emulationssystem für digitale ASIC-Bausteine

Jan-Morten Reiners, Andreas Stiller, Peter Schulz Fachhochschule Dortmund

Band 57 Workshop: Albstadt-Sigmaringen Februar 2017

31 Graphbasierte Verifi kation mikroelektronischer Schaltungen

Lutz Bense, Marco Trunzer und Joachim Gerlach Hochschule Albstadt-Sigmaringen

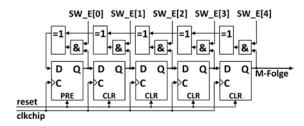

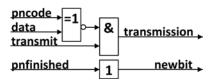

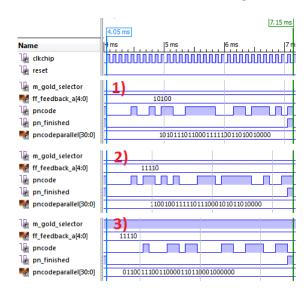

39 Entwurf und FPGA Implementierung eines DSSS-Übertragungssystems für den Einsatz in der Lehre

Dominik Schwarz, Christian Geist, Anestis Terzis Hochschule Ulm

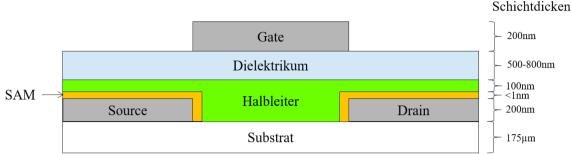

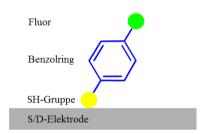

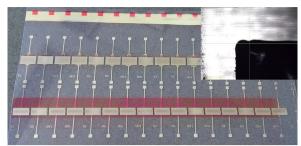

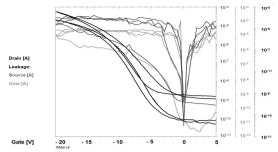

47 Entwicklung eines Prozesses für komplett Inkjet-gedruckte organische Schaltungen

Alexander Scholz, Thomas Rohland, Bernd Vettermann, Jürgen Giehl Hochschule Mannheim

# Inhaltsverzeichnis

| Entwicklung eines intelligenten autonomen Fahrzeugs                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Delay-Line Analog-Digital-Wandler mit geringer Latenzzeit für digital geregelte Schaltwandler</b> 13 S. Quenzer-Hohmuth, C. Jiago, S. Ritzmann, T. Rosahl, B. Wicht, Hochschule Reutlingen |

| Entwicklung eines Feldbusmoduls "CAN" für eine neue                                                                                                                                           |

| Modulares Test- und Emulationssystem für digitale ASIC-Bausteine                                                                                                                              |

MPC-WORKSHOP Februar 2017

# Inhaltsverzeichnis

| Lutz Bense, Marco Trunzer und Joachim Gerlach, Hochschule Albstadt-Sigmaringen                                                                      |              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Entwurf und FPGA Implementierung eines DSSS-Übertragungssystems für den Einsatz in Dominik Schwarz, Christian Geist, Anestis Terzis, Hochschule Ulm | der Lehre 39 |

| Entwicklungeines Prozesses für komplett Inkjet-gedruckte organische Schaltungen                                                                     |              |

# Tagungsband zum Workshop der Multiprojekt-Chip-Gruppe Baden-Württemberg Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie. Die Inhalte der einzelnen Beiträge dieses Tagungsbandes liegen in der Verantwortung der jeweiligen Autoren.

Herausgeber: Jürgen Giehl, Hochschule Mannheim, Paul-Wittsack-Straße 10, D-68163 Mannheim

Mitherausgeber (Peer Reviewer):

Marc Ihle, Hochschule Karlsruhe, Moltkestraße 30, D-68163 Karlsruhe

Frank Kesel, Hochschule Pforzheim, Tiefenbronner Straße 65, D-75175 Pforzheim

Jasmin Aghassi-Hagmann, Hochschule Offenburg, Badstraße 24, D-77652 Offenburg

Elke Mackensen, Hochschule Offenburg, Badstraße 24, D-77652 Offenburg

Lothar Schmidt, Hochschule Ulm, Prittwitzstraße 10, D-89075 Ulm

Alle Rechte vorbehalten

Diesen Workshopband und alle bisherigen Bände finden Sie im Internet unter: http://www.mpc-gruppe.de/de/workshopbaende.html

# Entwicklung eines intelligenten autonomen Fahrzeugs

Dustin Braun, Robin Braun, Christian Epe, Bernhard M. Rieß

Zusammenfassung — Autonomes Fahren wird in Zukunft eine immer größere Rolle spielen. In dem vorgestellten Beitrag wird ein autonom fahrendes Modellauto gezeigt, bestehend aus Chassis, zwei elektrischen Antriebsmotoren, Lenkung mit elektrischem Servomotor, Akku, Kamera und Mikrocontroller sowie der zugehörigen, auf dem Mikrocontroller befindlichen Steuer- und Regelungssoftware.

Die zentralen Komponenten der Steuerungssoftware bestehen aus:

- Filterung und Korrektur der Kameradaten

- Kurvenfrüherkennung durch Einsatz einer zweiten Kamera

- Nichtlineare Lenkungsregelung

- Geschwindigkeitsregelung mittels Geschwindigkeitsmessung durch an den Hinterrädern angebrachter Hall-Sensoren und Regelkreis

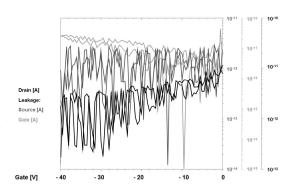

- Zielerkennung mittels Kamera

Damit gelingt es dem Fahrzeug eine beliebige aber aus vordefinierten Grundelementen bestehende Strecke selbständig zu befahren. Das heißt durch Anwendung einer kleinen mikroelektronischen Schaltung – einer Mikrocontrollers – ist es mit einfachsten Mittel möglich ein autonomes Fahrzeug zu entwickeln und zu programmieren. Beliebige Streckenführungen können so mit möglichst hoher Geschwindigkeit durchfahren werden, ohne die vorgegeben Strecke zu verlassen.

Abbildung 1: Streckenführung beim NXP-CUP EMEA Final 2016.

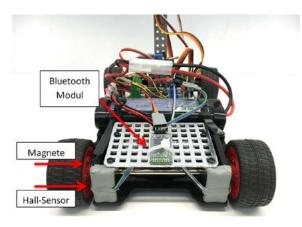

Abbildung 2: Autonomes Fahrzeug der Hochschule Düsseldorf.

### I. EINLEITUNG

Ziel dieser Projektarbeit war die Entwicklung eines autonomen Fahrzeugs im Maßstab 1:18, das in der Lage ist eine unbekannte Strecke eigenständig zu fahren. Grundlage bilden die Vorgaben und Regeln des internationalen NXP-Cup [1] bei denen jährlich Universitäten und Hochschulen mit eigens entwickelten Fahrzeugkonzepten gegeneinander im Wettbewerb antreten. Eine typische Strecke ist in Abb. 1 dargestellt.

### II. HARDWARE

Aufbauend auf einem vorgegebenen Basismodell können am Fahrzeug Eigenentwicklungen angebaut werden. Dabei muss ein optischer Sensor (Kamera) zur Navigation genutzt werden. Darüber hinaus sind bis zu 15 weitere Sensoren erlaubt, wie z.B. die Verwendung eines Geschwindigkeits-, Beschleunigungsoder Infrarotsensors. Die Verarbeitung der Kameradaten geschieht auf einem 32-Bit-Mikrocontroller, welcher nach der Aufbereitung und Auswertung der Kameradaten Entscheidungen über den nötigen Lenkungseinschlag und die Geschwindigkeit der beiden jeweils separat ansteuerbaren Hinterräder trifft. Das Projektkonzept verwendet die von der Firma NXP zur

1

Abbildung 3: Fahrzeugkonzept Detail-Hinterachse.

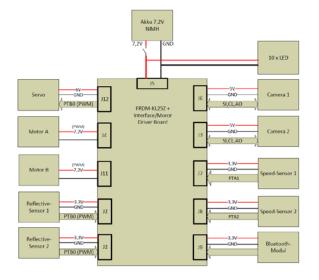

Abbildung 4: Schematische Übersicht der Kommunikationsstruktur.

Verfügung gestellten Grundkomponenten: Chassis des Fahrzeugs, Kamera, NXP FRDM-KL25Z Board, Interface/Motor Driver Board, Steuerungsservo, Motoren. Abbildung 4 zeigt das Blockschaltbild der Kommunikation zwischen dem FRDM-KL25Z Mikrocontroller und den verwendeten Sensoren und Aktoren.

Zur Geschwindigkeitsmessung dienen zwei Hallsensoren. So kann der implementierte Regelalgo-rithmus je nach Streckenführung Geschwindigkeit der beiden Antriebsmotoren auswerten und gezielt anpassen. Die Aufhängung der Kamera sowie die Befestigung der Elektronik erfolgt mit leichten Alu-minium-Blechen. Spannungsversorgung wurde mit einem RC-Akku, 7,2 V, 1500 mAh, realisiert. Mit Hilfe eines Bluetooth-Moduls kann zu Entwicklungs-zwecken drahtloser Kamera-, ein Austausch vom Lenkungs- und Geschwindigkeitsdaten mit dem PC, auf dem die Software entwickelt wird, erfolgen. Auch die implementierten Betriebsmodi Config, Auto, Soft-Brake, Hard-Brake und Manual können damit gesetzt werden.

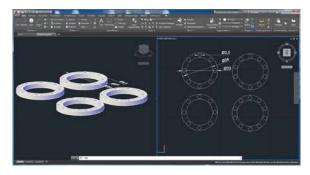

Abbildung 5: Design der Magnetringe in AutoCAD [2].

Abbildung 6: Design der Magnetringe in AutoCAD [2].

### A. Geschwindigkeitsmessung

Die Messung der Fahrzeuggeschwindigkeit erfolgt über die Messung von Magnetfeldern mittels zweier Hallsensoren (Typ SS413A) an den an der Hinterachse angebrachten Antriebsrädern, wie in Abbildung 3 dargestellt. Dazu wurden mit Hilfe des CAD-Werkzeugs AutoCAD [2], wie in Abbildung 5 dargestellt, Kunststoffringe entwickelt, in denen die Magnete an den Hinterrädern des Fahrzeugs befestigt werden können. Diese wurden mit Hilfe eines 3D-Druckers gefertigt, die anschließend mit 10 Neodym-Magneten wechselnder Polarität bestückt wurden. Abbildung 6 zeigt von links nach rechts die gefertigten Kunststoffringe in Relation zum Fahrzeug, die mit den Magneten bestückten Ringe sowie die am Hinterrad angebrachten Ringe.

### B. Kamera

NXP-Cup Strecke beim besteht vorgegebenen Fahrbahnelementen mit schwarzen Fahrbahnbegrenzungen am linken und rechten Fahrbahrand auf weißem Grund. Um die Streckenführung frühzeitig zu erkennen, wird die dazu verwendete Kamera, wie in Abbildung 2 zu sehen, einem Mast angebracht. Streckenerkennung geschieht über eine Line-Scan-Kamera (1x128 Pixel) mit manuell einstellbarem Fokus und einer maximalen Clock-Rate von 8 Abbildung 7 zeigt links die Rück- und rechts die Vorderseite der verwendeten Kamera.

Nach Anlegen der Spannungsversorgung und eines entsprechenden Clock-Signals gibt die Kamera am analogen Output nacheinander Spannungen für jeden Pixel aus, deren Wert der erfassten Helligkeit entspricht. Die Ausgabe eines kompletten Bildes kann je nach Clock zwischen 267 µs und 68 ms dauern. Die

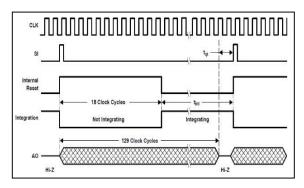

Abbildung 7: Line-Scan-Kamera (Vor- und Rückseite, Quelle: [3], mit TAOS TSL1401R-LF,  $128\times1$  LINEAR SENSOR ARRAY.

Abbildung 8: Timing-Verhalten des TSL1401R-LF, 128  $\times$  1 LINEAR SENSOR ARRAY.

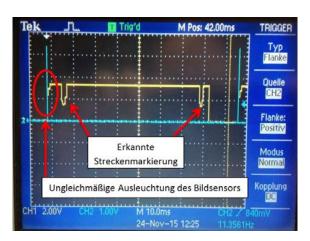

Einstellung des Kamerafokus erfolgt mittels Oszilloskop. Dabei zeigen sich Probleme bei schlechter Ausleuchtung der Strecke sowie einer ungleichmäßigen Belichtung des Bildsensors aufgrund der Linse, erkennbar links beim Zeilenbeginn in Abbildung 9. Das gelb dargestellte Signal zeigt die von der Kamera empfangene Helligkeit. Am rechten und linken Rand fällt sofort eine deutlich reduzierte Helligkeit auf, die durch die schwarze Fahrbahnbegrenzung im Kontrast zur weißen Fahrbahn hervorgerufen wird. Zusätzlich ist rot markiert am linken Rand das Problem mit der ungenügenden Streckenausleuchtung erkennbar. Der Effekt verschlimmert sich zu beiden Seiten bei schwächer werdender Ausleuchtung oder zu hoch gewählter Clock-Frequenz. Letzteres begründet sich mit der vom Bildsensor benötigten Integrationszeit.

Jeder der 128 Pixel besteht aus einer Verschaltung einer Photodiode, einem Operationsverstärker und einem Kondensator. Die Photodiode lädt den Kondensator mit einer Geschwindigkeit proportional zur Lichtintensität auf. Die Dauer des Ladevorgangs (Integrationszeit) ist die Zeit zwischen den positiven Flanken des in Abbildung 8 dargestellten SI Signals. Die Kondensatorspannung (AO) hängt daher sowohl von der Integrationszeit als auch von der Lichtintensität ab. Mit steigender Clock-Rate steht jedem Pixel weniger Zeit zur Verfügung seine Spannung aufzubauen. Insgesamt sinkt damit der Signalpegel der Kamera, wobei die äußeren Pixel am anfälligsten für diese "Störung" sind. Wird hingegen die Clock-Rate zu niedrig gewählt, läuft man Gefahr die Strecke unterabzutasten, wodurch die Streckenerkennung je nach

Abbildung 9: Spannung am Ausgang A0 eines Kamerabildes.

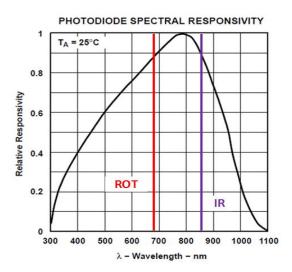

Abbildung 10: Spektrale Empfindlichkeit der Kamera.

Geschwindigkeit des Fahrzeugs "verschmieren" kann. Zur Lösung dieses Problems ist eine gute Balance zwischen niedrig zu haltender Clock-Rate und ausreichender Streckenauflösung zu finden. Alternativ kön-nen die Kameradaten per Software aufgearbeitet wer-den, wie in Kapitel II.B erläutert.ms

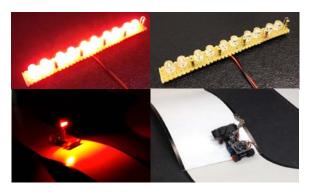

### C. Ausleuchtung der Strecke

Wie in Kapitel II.B beschrieben, können schwierige Lichtverhältnisse auf der Strecke zu verschlechterten Kameradaten führen. Zudem ist es denkbar, dass das Fahrzeug einen Tunnel passieren muss. Zu diesem Zweck wurde eine Beleuchtung am Fahrzeug passend zur Empfindlichkeit des Bildsensors angebracht. Abbildung 10 zeigt die spektrale Empfindlichkeit der verwendeten Photodioden. Die stärkste Empfindlichkeit der Photodioden liegt im Infrarotbereich (IR). Aus Kostengründen wurden rote LEDs verwendet, da ihre abgestrahlte Lichtwellenlänge von 680 nm in einem ähnlich empfindlichen Spektralbereich wie die maximale Empfindlichkeit der Photodioden des

Abbildung 11: Beleuchtung mit Hilfe roter LEDs.

Bildsensors liegt ("ROT" in Abb. 10). Abbildung 11 zeigt oben das entworfene Beleuchtungselement, bestehend aus 10 roten LEDs im ein- (links) und ausgeschalteten (rechts) Zustand sowie unten auf dem Fahrzeug im Einsatz.

### D. Mehrkamera-Konzept

Die von NXP vorgegeben maximalen Ausmaße des Fahrzeugs betragen 305x400x250 mm (HxLxB). Hieraus ergibt sich eine maximale Kamerahöhe und ein damit entstehender Blickwinkel auf die Strecke. Der Bildsensor soll die gesamte Streckenbreite (60 cm) und zusätzlich einen Sicherheitsbereich von ca. 5 cm zu beiden Seiten erfassen. Hieraus ergibt sich mit der verwendeten Linse (Öffnungswinkel: ca. 60°) eine Mindestsichtweite von ca. 50 cm vor das Auto. Die eingestellte Sichtweite beeinflusst in hohem Maß das Kurvenfahrverhalten. Je weiter nach vorn die Kamera schaut, desto enger werden die Kurven gefahren. Dem entgegen steht die Bewältigung des Hügels, da eine weiter nach vorne schauende Kamera bei Steigungen schneller die Sicht auf die Strecke verliert. Zudem ist

Abbildung 12: Zwei-Kamera-Konzept.

bei höheren Geschwindigkeiten vor Kurven ein Abbremsen nötig, damit das Fahrzeug nicht von der Strecke driftet. Das erfordert jedoch eine besonders weite Sicht nach vorne. Aus diesem Grund wurde wie in Abbildung 12 dargestellt auf ein Zwei-Kamera-System gesetzt. Kamera 1 (Cam 1) wurde auf optimale Kurven- und Hügelfahrt ausgerichtet. Kamera 2 (Cam 2) dient der Kurvenfrüherkennung.

### III. SOFTWARE

Im Folgenden werden grundlegende Konzepte der entwickelten Software vorgestellt.

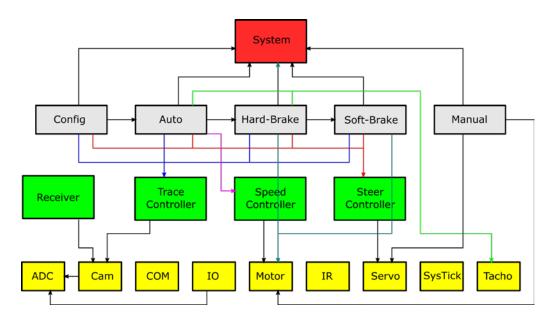

### A. Grundkonzept der entwickelten Software

Zur Ansteuerung der Hardware wurden effiziente Treiber, in Abbildung 13 gelb dargestellt, geschrieben, welche einfach zu verwendende Funktionen nach außen bereitstellen. Die Treiber konfigurieren die entsprechenden Register des Controllers. Die in Abbildung 13 in grün dargestellten Controller regeln anhand der erfassten Kamera- und Geschwindigkeitsdaten die Auslenkung der Vorderräder sowie die Geschwindigkeit der Motoren an der Hinterachse. Eine genaue Beschreibung der Regler erfolgt in Abschnitt III.C. Das Verhalten des Gesamtsystems wird durch

Abbildung 13: Übersicht Softwarekonzept.

Abbildung 14: Aufbereitung der Kameradaten.

Abbildung 15: Erkennung der Fahrbahngrenzen.

die in Abbildung 13 in grau dargestellten und in Ab-schnitt III.D näher beschriebenen Betriebsmodi be-stimmt. Das System (rot dargestellt) lässt sich mit Hilfe der Betriebsmodi beispielsweise von einem Entwicklungs-Modus (Manual-Modus) in einen Con-fig-Modus und einen Race-Modus (Auto-/Hard-Brake-/Soft-Brake-Modus) umschalten.

### B. Verarbeitung der Kameradaten

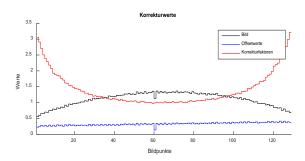

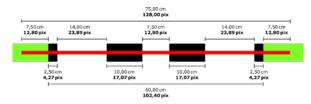

Die Streckenerkennung (schwarze Fahrbahnbegrenzungen auf weißem Grund) geschieht, wie in Kapitel II.B dargestellt, über eine Line-Scan-Kamera (1x 128 Pixel), deren Daten einer Aufbereitung bedürfen. Wie in Abbildung 14 zu erkennen ist, erfahren die äußeren Pixel des Bildsensors (schwarze Kurve) aufgrund der Kameralinse eine geringere Belichtung. Zudem tritt bei absoluter Dunkelheit ein Offset-Fehler auf, der in Abbildung 14 in blau zu sehen ist. Um sowohl die geringere Belichtung an den Fahrbahnrändern sowie auch die Offsetwerte zu kompensieren, wurden für jedes Kamerapixel Korrekturfaktoren – in Abbildung 14 rot dargestellt - berechnet. Zur Aufbereitung der Kameradaten, d.h. zur Kompensation des Offsets und der geringeren Randbelichtung, wird der Offset von den tatsächlichen Pixelwerten der Kamera subtrahiert und das Ergebnis mit dem jeweiligen Korrekturfaktor multipliziert:

pixelvalue[index] =

(pixelvalue[index] - offset[index])\* factor[index]

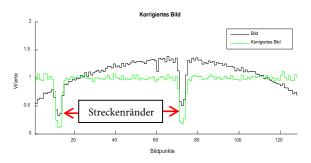

Abbildung 16: - Konzept: Lenkung.

Das Ergebnis der Bildkorrektur ist in Abbildung 15 dargestellt. Die schwarze Kurve zeigt die original Kameradaten, die grüne Kurve das Ergebnis nach der Bildverarbeitung. Die schwarzen Streckenbegrenzungen am linken und rechten Fahrbahnrand sind nun als ausgeprägte Minima sehr gut zu erkennen und zu detektieren und zur Weiterverarbeitung für die Fahrzeugsteuerung hervorragend verwendbar.

### C. Regler

In diesem Kapitel wird die Lenkungsregelung vorgestellt. Diese besteht aus der Berechnung der Ansteuerungswerte für den Servomotor, der die gelenkten Räder an der Vorderachse einschlagen kann, dem Steer Controller Kapitel III.C.1 und einem Modul zur frühzeitigen Erkennung von Kurven und dem Ziel, dem Trace Controller Kapitel III.C.2.

### 1) Steer Controller

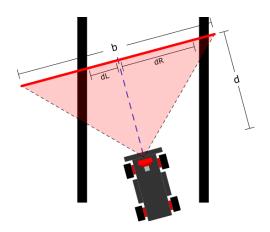

Die zurückzulegende Strecke ist dem Auto nicht bekannt. Es können jeder Zeit Hindernisse, wie Kurven, Schikanen, Kreuzungen, Hügel sowie ein Rüttelabschnitt auftreten. Darauf muss der Steueralgorithmus reagieren können. Aus den empfangenen und korrigierten Kameradaten wird, wie in Abbildung 16 dargestellt, permanent der Abstand der Fahrzeuglängsachse zum linken Fahrbahnrand dL und zum rechten Fahrbahnrand dR berechnet. Das Software-Modul Steer Controller berechnet daraus den Lenkungseinschlag und sorgt dafür, dass dL und dR ständig angeglichen werden.

Bei der Wahl des Lenkalgorithmus muss darauf geachtet werden, dass die Lenkung nicht schwingt. Schwingungen entstehen typischerweise durch I-Anteile des Reglers, Verzögerungen und zu extremen Lenkbewegungen. Die Lenkung muss jedoch stark genug sein, um einen Hügel auch direkt nach einer Kurve gerade hochfahren zu können. Kreuzungen dürfen nicht dazu führen, dass das Auto abbiegt.

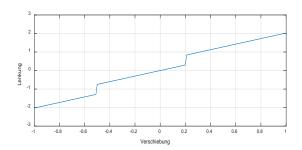

Abbildung 17: – Lineare Lenkung: Es wird entsprechend dem Mittelwert des Abstandes von Mitte bis linken bzw. rechten Kante eingelenkt.

Abbildung 18: Lineare Lenkung mit Sprung: Entspricht der linearen Lenkung, jedoch macht diese, wenn eine Fahrbahnbegrenzung nicht erkannt wurde, einen Sprung in die jeweilige Richtung der nicht erkannten Fahrbahnkante. Dies führt dazu, dass auf Kurven schneller reagiert wird, aber leider auch auf Kreuzungen. Diese Lenkung wird im jetzigen Fahrzeug verwendet, da sie das beste Ergebnis liefert.

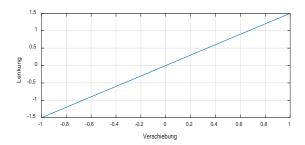

Schlangenlinien sollten am besten gerade durchfahren werden. Während der Testphase wurden verschiedene Lenkalgorithmen getestet, welche in den Abbildungen 17 bis 20 beschrieben werden. Für den Einsatz im vorgestellten Fahrzeug hat sich die in Abbildung 18 dargestellte lineare Lenkung mit Sprüngen in den Experimenten als am geeignetsten herausgestellt.

### 2) Trace Controller

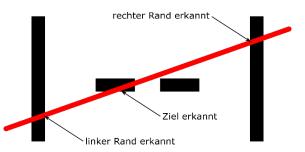

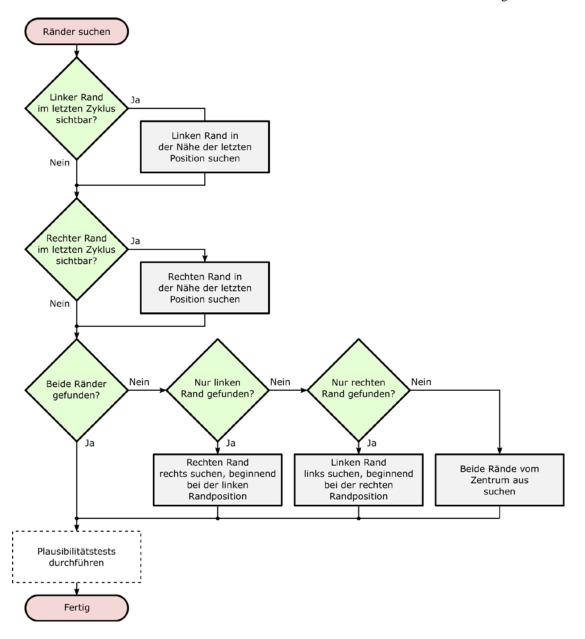

Das Modul Trace Controller übernimmt die Randerkennung sowie die Randverfolgung der abzufahrenden Strecke. Außerdem können mit diesem Modul Kurven und das Ziel frühzeitig erkannt werden.

### a) Randverfolgung

Es wurde eine Streckenrandverfolgung wie in Abbildung 22 dargestellt implementiert, die es gestattet, bei verlorener Sicht auf die Fahrbahn oder beim Verlassen der Fahrbahn (z.B. durch Drift in Kurven) wieder auf die Strecke zurück zu finden. Mit Hilfe der Randverfolgung ist es möglich Kurven wesentlich schneller zu fahren.

Abbildung 19: Quadratische Lenkung: Bei der quadratischen Lenkung werden kleine Verschiebungen nur wenig ausgeglichen und größere Verschiebungen sehr stark. Dies hat den Vorteil, dass Kurven mit einer geringen Verzögerung stark genommen werden, die Schlangenlinien jedoch praktisch gerade durchfahren werden.

Abbildung 20: Interpolation: Hierbei wird eine Funktion durch mehrere Verschiebungen aufgestellt. Abhängig von den Verschiebungen wird dann zwischen zwei Punkten interpoliert, d.h. es wird eine vorgegebene Funktion angenähert.

Abbildung 21: Konzept: Kurvenfrüherkennung.

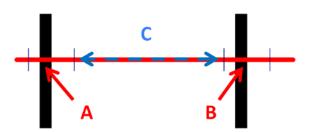

### b) Kurvenfrüherkennung

Damit das Auto auf geraden Strecken möglichst schnell fahren kann, muss eine Kurve bereits möglichst früh vor dem Einlenken erkannt werden, so dass genügend Zeit zum Abbremsen und Einlenken bleibt. Dafür wurde, wie in Kapitel II.D erwähnt, eine zweite Fernkamera (Cam 2, Abb. 12) angebracht, welche etwas weiter als die erste Kamera (Cam 1, Abb. 12) schaut. Zur frühzeitigen Erkennung von Kurven werden, wie in Abbildung 22 gezeigt, zwei Intervalle A und B innerhalb eines Kamerabildes sowie ein Abstand C dieser Intervalle definiert. Kamera 2 prüft, ob innerhalb der Intervalle A und B jeweils ein Rand und im Bereich C "nichts" erkannt wird. In diesem Fall handelt es sich mit hoher Wahrscheinlichkeit um einen geraden Streckenabschnitt, so dass die vor dem Fahrzeug liegende Strecke mit hoher Geschwindigkeit

Abbildung 23: Zielmarkierung beim NXP-Cup; Schwarz dargestellt ist die Zielmarkierung, der rote Strich entspricht der Kamerabildbreite, grün markiert ist der Bereich neben der Strecke.

gefahren werden kann. Die Regelung der Geschwindigkeit wird in Abschnitt III.C.3 beschrieben. Die Kurvenfrüherkennung erlaubt somit eine Geschwindigkeitssteigerung auf gerader Strecke und vermeidet das Hinausdriften aus Kurven dank der Möglichkeit des frühzeitigen Bremsens.

Abbildung 24: Sichere Zielkennung auch bei schräger Durchfahrt.

### c) Zielerkennung

Laut NXP-Cup-Regeln muss das Fahrzeug nach Durchfahren einer Zielmarkierung innerhalb einer

Abbildung 22: - Konzept: Streckenrandverfolgung.

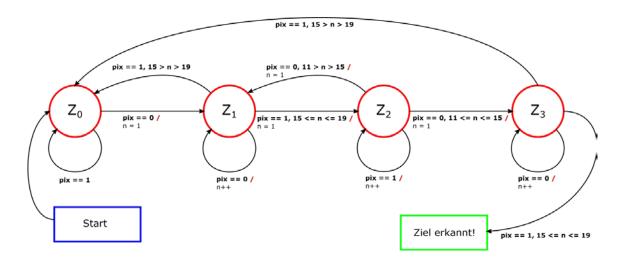

Abbildung 25: Zustandsautomat der einfachen Zielerkennung.

Bremszone von zwei Metern Länge zum Stillstand kommen. Die Zielmarkierung besteht, wie in Abbildung 23 dargestellt, aus einem zweigeteilten und quer zur Fahrbahn liegenden schwarzen Streifen mit bekannten Abmessungen. Die Erkennung läuft in diesem Fall durch einfaches Überprüfen des Kamerabildes mit Hilfe eines einfachen Zustandsautomaten dessen Zustandsübergangsdiagramm in Abbildung 25 gezeigt ist.

Ein als weiß erkanntes Pixel wird im Zustandsübergangsdiagramm mit einer logischen 0 (pix==0) dargestellt, ein schwarzes Pixel mit 1 (pix==1). Der Zustandsautomat überprüft nun jedes Pixel eines Kamerabildes hinsichtlich des zu erwartenden Zielmusters.

Der Startzustand des Automaten ist  $Z_0$ . Dies entspricht dem linken schwarzen Fahrbahnrand. Solange weitere schwarze Pixel des linken Rands erkannt werden, bleibt der Automat im Zustand  $Z_0$ . Nun überprüft der Automat die Pixelfolge, die die Kamera liefert, von links nach rechts. Sobald eines oder mehrere weiße Pixel erkannt werden, befinden wir uns links von der Zielmarkierung und der Automat geht in den Zustand  $Z_1$  über.

Anschließend überprüft der Automat, ob die linke der beiden 10 cm langen schwarzen Zielmarkierungen kommt. Gegenüber dem tatsächlichen Pixelmuster aus Abbildung 23 prüft der Zustandsautomat mit einer gewissen Toleranz, da Kanten nicht immer direkt zwischen zwei Pixeln liegen werden. So hat der erste Teil der Zielmarkierung beispielweise eine reale Bildbreite von 17,07 Pixeln. Dieses Teilstück wird im Zustandsübergangsdiagramm aus Abbildung 25 mit einer Toleranz von 15 <= n <= 19 als richtig erkannt gewertet, so dass der Übergang von Zustand  $Z_1$  zu  $Z_2$  erfolgen kann. Liegen die Werte außerhalb der Toleranz erfolgt der jeweils dargestellte Rücksprung zu einem früheren Zustand und die Überprüfung erfolgt erneut.

Wird aus  $Z_2$  heraus der weiße Spalt zwischen den beiden schwarzen Zielmarkierungen mit einer Breite von 11 - 15 Pixeln erkannt, erfolgt ein Zustandsübergang nach  $Z_1$ .

Wenn nun der zweite, rechte Teil der Zielmarkierung erkannt wird (Breite wiederum zwischen 15 und 19 Pixel), erfolgt ein erneuter Zustandsübergang von Z 1 nach Z 2.

Wird nun der weiße Bereich zwischen dem rechten Zielmarkierung und dem rechten Fahrbahnrand mit einer Breite von 11 – 15 Pixeln erkannt, geht der Automat in den Zustand Z\_3 über und das Ziel ist damit vollständig erkannt. Danach kann z.B. ein Bremsvorgang eingeleitet werden.

Diese Methode mittels einfachem Zustandsautomaten funktioniert jedoch nur, wenn das Auto auf geradem Weg das Ziel passiert.

Wenn das Fahrzeug schief durch das Ziel fährt, wie in Abbildung 24 dargestellt, wird das Ziel mit dem oben beschriebenen einfachen Zustandsautomaten nicht erkannt. Um das Ziel auch bei schiefer Durchfahrt sicher zu erkennen, ist die Toleranz des Zustandsautomaten noch weiter zu erhöhen. Im finalen Konzept wird nun lediglich überprüft, ob zwischen dem linken und rechten Fahrbahnrand ein dunkler Strich zu sehen ist. Dabei muss der dunkle Strich einen Mindestabstand zu den Rändern aufweisen. Außerdem muss er eine minimale maximale Breite aufweisen. Die minimale Breite ist etwas größer als eine Randstreifenbreite, da nur ein Randstreifen fälschlicherweise als Ziel erkannt werden könnte. Die maximale Breite ergibt sich aus der realen Zielmarkierung bei gerader Durchfahrt. Mit dieser Methode lässt sich die Zuverlässigkeit der Zielerkennung wesentlich verbessern.

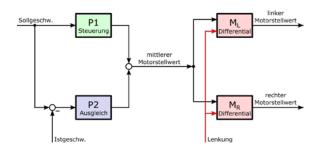

Abbildung 26: Drehzahlregelung (links) der beiden Antriebsmoto-ren  $M_L$  und  $M_R$  (rechts).

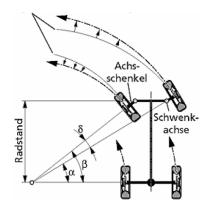

Abbildung 27: Verhalten aller Räder bei Kurvenfahrten (Quelle rechtes Bild: [4]).

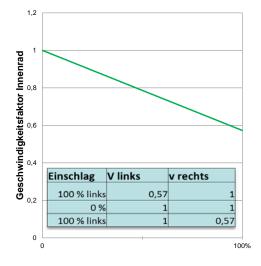

Abbildung 28: Geschwindigkeitsfaktor des inneren Rades im Verhältnis zum äußeren Rad.

### 3) Speed Controller

Der Speed Controller regelt die Drehzahl der beiden Antriebsmotoren  $M_L$  und  $M_R$ , die jeweils das rechte und linke Hinterrad antreiben. Der Regler ist, wie Abbildung 26 zeigt, in zwei Teile aufgeteilt. Der links dargestellte erste Teil regelt die Vorgabegeschwindigkeit des Autos mit Hilfe zweier P-Regler P1 und P2. P2 regelt nach der Differenz zwischen Soll- und Ist-

Abbildung 29: Zustandsdiagramm Betriebsmodi bei autonomer

wert. Der Proportionalitätswert von P2 kann aufgrund von Störungen bei der Erfassung der Geschwindigkeitsmessdaten nicht beliebig hoch gewählt werden. Daher bleibt ein relativ großer Restwert zum Sollwert übrig. Dieser Restwert wird üblicherweise durch einen I-Regler ausgeglichen. Das vorgestellte Konzept verwendet jedoch stattdessen einen weiteren P-Regler, den Regler P1, der nicht regelt, sondern nur nach dem Sollwert steuert. D.h. P2 regelt dann nur noch die letzte verbleibende Differenz aus. Hierdurch wird der Restwert zum Sollwert um ein vielfaches kleiner und es kann auf einen verzögerungsbehafteten I-Regler verzichtet werden. Der wesentliche Vorteil dieses Regelungskonzepts ist, dass es nicht zu Überschwingungen führt.

Der zweite Teil des Speed Controllers, der in Abbildung 26 rechts zu sehen ist, regelt die Drehzahl der beiden Motoren an der Hinterachse abhängig von der Vorgabegeschwindigkeit und dem Lenkungseinschlag. Wenn das Auto eine Kurve fährt, dreht sich das innere Rad, wie in Abbildung 27 dargestellt, aufgrund des kleineren inneren Kurvenradius langsamer als das kurvenäußere Rad. Damit die Räder in einer Kurve nicht über- bzw. unterbelastet werden, wird die Spannung auf dem äußeren Rad entsprechend des Lenkeinschlags erhöht und die Spannung auf dem inneren Rad entsprechend verringert. Der entsprechende Korrekturfaktor für die Geschwindigkeit am Innenrad ist in Abbildung 28 dargestellt. Hieraus resultiert eine stabilere Kurvenfahrt, da bei nicht angepasster Drehzahl das Heck des Fahrzeugs schneller aus der Kurve ausbrechen würde.

### D. Betriebsmodi

Während der Fahrt befindet sich das Fahrzeug in verschiedenen Betriebsmodi, die in Abbildung 29 dargestellt sind. Es wurden die Betriebsmodi Config, Auto, Soft-Brake, Hard-Brake und Manual implementiert, welche, mit Ausnahme des Manual-Modus, bei autonomer Fahrt entsprechend dem dargestellten Zustandsdiagramm durchlaufen werden.

### 1) Config-Modus

Im Config-Modus kann die maximale und minimale Geschwindigkeit des Autos eingestellt werden. Zum Überprüfen der Funktionalität ist die Lenkung bereits in diesem Modus aktiv, jedoch sind die Antriebsmoto-

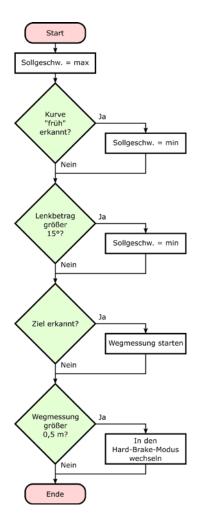

Abbildung 30: Ablaufdiagramm Auto-Modus.

ren inaktiv. 1,5 Sekunden nachdem der Startknopf betätigt wurde, wird in den Auto-Modus gewechselt.

### 2) Auto-Modus

Im, in Abbildung 30 dargestellten, Auto-Modus sind alle Steuerungsmechanismen aktiv. Die Geschwindigkeit wird, wie in Kapitel III.C.3 beschrieben über den Speed Controller geregelt und die Lenkung wie in Kapitel III.C.1 diskutiert über den Steer Controller. Die Kurvenfrüherkennung und die Zielerkennung kann über Schalter ein- bzw. abgeschaltet werden. Die Zielerkennung wird jedoch erst nach 8 Sekunden aktiviert, da erfahrungsgemäß alle Strecken im Wettbewerb mindestens 8 Sekunden lang sind. Damit soll vermieden werden, dass zu früh irrtümlicherweise ein Ziel erkannt wird. Wenn das Ziel erkannt wurde, wird über die Geschwindigkeitsmessung der zurückgelegte Weg gemessen. Sind 0,5 m zurückgelegt, wird in den Hard-Brake-Modus gewechselt.

Abbildung 31: Ablaufdiagramm Hard-Brake-Modus.

### 3) Hard-Brake-Modus

Abbildung 31 zeigt den Hard-Brake-Modus, in welchem auf beide Motoren eine Gegenspannung angelegt wird, um aktiv zu bremsen. Hierdurch wird die Drehrichtung der angetriebenen Hinterräder auf "rückwärts" gestellt. Damit das Auto auch in diesem Modus stabil bleibt, bleibt die Lenkung sowie das Differential auf den Antriebsmotoren aktiv. Da mit dem Geschwindigkeitssensor die Fahrtrichtung nicht erkannt werden kann, muss sichergestellt werden, dass das Auto nicht rückwärts weiter fahren kann. Daher wird in den Soft-Brake-Modus gewechselt, sobald die aktuelle Geschwindigkeit unter 0.35 m/s gefallen oder 1 Sekunde vergangen ist.

### 4) Soft-Brake-Modus

Das Ablaufdiagramm des Soft-Brake-Modus ist in Abbildung 32 dargestellt. Im Soft-Brake-Modus wird eine geringe Gegenspannung auf die Antriebsmotoren gelegt. Diese Gegenspannung ist so gering, dass das Auto damit nicht in der Lage ist rückwärts zu fahren. Normalerweise sollte damit das Fahrzeug in der 2 m langen Bremszone nach dem Ziel sicher zum Stehen kommen. Nach 2 Sekunden wird für eine erneute Fahrt wieder in den Config-Modus gewechselt.

### 5) Manual-Modus

Im Manual-Modus sind alle Steuerungsmechanismen inaktiv. Das Auto steuert sich nicht, wie in Abbildung 29 gezeigt, selbst, sondern kann über den PC ferngesteuert werden. Dies vereinfacht die Entwicklung und Programmierung des Autos enorm,

Abbildung 32: Ablaufdiagramm Soft-Brake-Modus.

da dem Auto z.B. bei Fehlfunktionen nicht mehr hinterher gelaufen werden muss. Zusätzlich kann damit das Auto bei Fehlfunktionen gestoppt werden, um mögliche Beschädigungen des Fahrzeugs oder der Umgebung zu vermeiden. Besonders beim Erreichen von hohen Geschwindigkeiten hat sich die im Manual-Modus verfügbare Stopp-Möglichkeit als sehr nützlich erwiesen.

### IV. ZUSAMMENFASSUNG

Das vorgestellte autonome intelligente Fahrzeug ist in der Lage eine unbekannte Strecke zu bewältigen die den Regeln des NXP-Cups [1] entspricht. Bei mehreren Testfahrten stellte sich heraus, dass die maximale erreichbare Geschwindigkeit für eine korrekte Durchfahrt aller Streckenabschnitte, und aller möglichen Streckenkonfigurationen stark vom intelligenten Zusammenspiel von Hardware und Software-Algorithmus abhängt. Als Beispiel sei hier die Kamera genannt, welche bei ungünstigem Neigungswinkel zu einem schlechteren Kurvenverhalten führt. Aus diesem Grund wurde auf ein Zwei-Kamera-System (Nahund Fernsichtkamera) zur Kurvenfrüherkennung gesetzt. Die maximale Geschwindigkeit des im Projekt entworfenen Fahrzeugs war bei den finalen Testläufen lediglich durch den endlichen Grip der Teststrecke begrenzt.

Das vorgestellte Fahrzeugkonzept gewann souverän die diesjährige nationale Vorentscheidung beim NXP-Cup am 22.03.2016 in Deggendorf mit einer Rundenzeit von 14,30 Sekunden und einem Abstand von 3,5 Sekunden zum Zweitplatzierten. Es nahmen 19 Teams von anderen Hochschulen aus Deutschland und Polen teil.

Beim NXP-Cup EMEA-Finale (Europe, Middle East, Africa) am 09.-10.05.2016 in München belegte

das Team der Hochschule Düsseldorf mit dem vorgestellten Fahrzeug einen hervorragenden 3. Platz. Diesmal auf einem größeren Parcours mit einer Rundenzeit von 16,6 Sekunden und nur knapp hinter dem zweitplatzierten Team aus Rumänien mit 16.4 Sekunden. Sieger wurde ein Team der Haute Ecole ARC Ingenierie aus der Schweiz mit 15,7 s. Um nach München zu kommen, gab es sechs Qualifikationsrunden Marokko, nationale in Frankreich, UK, Rumänien, Deutschland und der Slowakei. Von den anfänglich 120 registrierten Teams mit insgesamt 350 Studenten von 50 Universitäten aus 15 Ländern in Europa sind schließlich 16 Teams mit insgesamt 51 Studenten nach München zur **EMEA-Endausscheidung** gefahren.

Dieses Projekt zeigt auch, dass, mit einem relativ geringen Budget von unter 400 € und überschaubaren Arbeitsaufwand von in Summe unter 400 h, ein Team von drei Studierenden in der Lage ist, innerhalb eines Semesters selbständig ein autonomes Fahrzeug zu entwickeln.

### V. LITERATURVERZEICHNIS

[1] The NXP Cup:

https://community.freescale.com/docs/DOC-1284

[2] AutoCAD:

http://www.autodesk.de/products/autocad/overview

[3] Line-Scan-Camera:

http://shahrulnizam.com/pic-lesson-linescan-camera/

[4] Begriffe der Fahrwerksvermessung www.kfzvermessung.de;

### VI. AUTORENINFORMATION

Dustin Braun, dustin.braun@study.hs-duesseldorf.de Robin Braun, robin.braun@study.hs-duesseldorf.de Christian Epe, christian.epe@hs-duesseldorf.de Bernhard M. Rieß, bernhard.riess@hs-duesseldorf.de

Hochschule Düsseldorf Münsterstraße 156 40476 Düsseldorf

# Delay-Line Analog-Digital-Wandler mit geringer Latenzzeit für digital geregelte Schaltwandler

Samuel Quenzer-Hohmuth, Cedric Jiago, Steffen Ritzmann, Thoralf Rosahl, Bernhard Wicht

Zusammenfassung-Digital geregelte Schaltwandler zeigen weniger Parameterschwankungen, sind flexibler und profitieren mehr von kleiner werdenden Strukturgrößen moderner Halbleitertechnologien als analog geregelte Schaltwandler. Die im digitalen Regelkreis notwendige AD-Wandlung muss zwingend mit geringer Latenzzeit und passender Auflösung erfolgen, um die Regelkreisstabilität nicht zu gefährden. Dieser Beitrag erläutert, weshalb konventionelle AD-Wandler-Konzepte für digital geregelte Schaltwandler ungeeignet sind und zeigt verschiedene Konzepte speziell für den Einsatz in digital geregelten Schaltwandlern. Der Fokus dieses Beitrags liegt auf einem Delay-Line AD-Wandler, dessen mehrstufige Struktur und Funktionsweise beschrieben wird. Es wird außerdem gezeigt, wie das charakteristische nichtlineare Übertragungsverhalten des **Delay-Line** Wandlers korrigiert werden kann. Die schaltungstechnische Implementierung und Simulationsergebnisse eines 6-Bit, 66 ns-Latenzzeit Delay-Line AD-Wandler werden vorgestellt sowie dessen Einsatz in einem 500 kHz-getakteten, 14V-auf-6V, 1A Abwärtswandler mit einer Transitfrequenz von 70 kHz.

Schlüsselwörter—Schaltwandler, digitale Regelung, Analog-Digital-Wandler, Delay-Line Analog-Digital-Wandler, geringe Latenzzeit, Fenster-Konzept.

### I. EINLEITUNG

Zur Regelung der Ausgangsspannung von Schaltwandlern können analoge oder digitale Regelungen eingesetzt werden. Digitale Regelungen weisen im Gegensatz zu analogen Regelungen zahlreiche Vorteile auf. Die bei analogen Reglern aufgrund ihrer Parameterschwankungen störenden Kompensationsbauelemente sind in digitalen Regelungen nicht vorhanden. Bei integrierten Lösungen kommen digitale Re-

Samuel Quenzer-Hohmuth (<u>samuel.quenzer-hohmuth@reutlingen-university.de</u>) und Bernhard Wicht: Hochschule Reutlingen (Robert Bosch Zentrum für Leistungselektronik), Alteburgstraße 150, 72762 Reutlingen

Cedric Jiago, Steffen Ritzmann und Thoralf Rosahl: Robert Bosch GmbH, Tübinger Straße 123, 72762 Reutlingen.

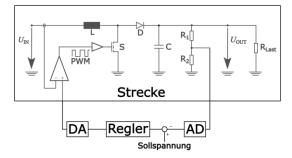

Abbildung 1: Digital geregelter Aufwärtswandler.

gelkreise mit kleinerer Chipfläche aus als vergleichbare analoge Regelkreise. Darüber hinaus lassen sich in digitalen Regelkreisen intelligente, adaptive Regelkonzepte besser umsetzen [1]-[6].

Abbildung 1 zeigt den Regelkreis eines digital geregelten Aufwärtswandlers. Zur digitalen Regelung sind ein AD- und ein DA-Wandler notwendig. Sowohl die AD-, als auch die DA-Wandlung müssen mit geringer Latenzzeit erfolgen. Latenzzeiten in Regelkreisen gefährden die Stabilität, weil sie zu einer unerwünschten Phasendrehung führen. Je höher die Auflösung, desto genauer kann die Abweichung der Ausgangsspannung des Schaltwandlers von der Zielspannung detektiert und korrigiert werden. Gleichzeitig müssen die Auflösungen von AD- und DA-Wandler zwingend zueinander passend gewählt werden, um unerwünschte Schwingungen der Ausgangsspannung zu vermeiden [12], [13].

Dieser Beitrag zeigt in Kapitel II, weshalb Standard-AD-Wandler-Konzepte in digital geregelten Schaltwandlern ungeeignet sind. Spezielle Konzepte für die AD-Wandlung, die ebenso in Kapitel II aufgeführt werden, sind dagegen geeignet.

In Kapitel III wird die mehrstufige Struktur, die Funktionsweise und die schaltungstechnische Implementierung des Delay-Line AD-Wandlers vorgestellt. Weiterhin wird das Fenster-Konzept, mit dem der Delay-Line AD-Wandler arbeitet, eingeführt.

Kapitel IV zeigt durch Simulationsergebnisse eines 500 kHz-getakteten Abwärtswandlers die grundsätzliche Eignung des Delay-Line-AD-Wandlers, auch bei einer hohen Transitfrequenz von 70 kHz. Es wird erläutert, wie das charakteristische, nichtlineare Übertragungsverhalten des Delay-Line AD-Wandlers korrigiert werden kann.

# II. ANALOG-DIGITAL-WANDLUNG IN DIGITAL GEREGELTEN SCHALTWANDLERN

### A. Anforderungen

Die Analog-Digital-Wandlung in einem digital geregelten Schaltwandler muss mit einer geringen Latenzzeit durchgeführt werden, um die Stabilität des Regelkreises nicht zu gefährden. Eine Latenzzeit  $T_{\rm D}$  führt zu einer Phasendrehung  $\Delta \varphi$  im Regelkreis, die mit folgender Gleichung berechnet werden kann:

$$\Delta \varphi = -\omega \cdot T_D$$

Folglich sind die Phasenreserve, und damit auch die Stabilität des Regelkreises, von der Phasendrehung durch die Latenzzeit betroffen. Je höher die Transitfrequenz des Regelkreises, desto größer ist die Auswirkung einer Latenzzeit  $T_{\rm D}$  auf die Phasenreserve. Ein AD-Wandler mit 5  $\mu$ s-Latenzzeit führt zum Beispiel in einem Abwärtswandler mit einer Transitfrequenz von 70 kHz schon zu einer Reduzierung der Phasenreserve um 126° und macht den Regelkreis dadurch instabil [2].

Die Auflösung des Analog-Digital-Wandlers muss bezogen auf die Ausgangsspannung kleiner sein als die Auflösung des Digital-Analog-Wandlers. Wenn diese Anforderung nicht eingehalten wird, kann die Ausgangsspannung infolge der Quantisierung durch Digital-Analog- und Analog-Digital-Wandler von stationären Schwingungen überlagert sein. Diese unerwünschten Schwingungen sind unter Limit Cycle Oscillations bekannt [12], [13]. Gleichzeitig können weder die Auflösung des AD-Wandlers noch des DA-Wandlers beliebig grob gewählt werden, sonst kann die Ausgangsspannung nicht mehr ausreichend genau auf den Zielwert geregelt werden.

Außerdem ist es erforderlich, dass der AD-Wandler monotones Verhalten zeigt. Monotonie-Fehler können zu Schwingungen im Regelkreis führen, weil der Regler auf fehlerhafte Werte reagiert.

### B. Konventionelle AD-Wandler-Konzepte

In integrierten Lösungen spielt der Flächenbedarf des AD-Wandlers eine übergeordnete Rolle. Flash-Wandler und auch Pipeline-Wandler, die hohe Latenzzeit-Anforderungen sehr gut erfüllen, kommen daher bei gleichzeitig hoher Auflösung nicht in Frage. Zur Erfüllung der Flächenanforderung eignet sich ein Delta-Sigma-Wandler. Aufgrund seiner einfachen Grundstruktur und auch der Möglichkeit das notwendige Dezimierfilter flächenarm auszuführen, kann eine hohe Auflösung bei kleiner Fläche erzielt werden. Doch trotz der Möglichkeit Auflösung und Latenzzeit des AD-Wandlers durch Variation des Dezimierfilters zu optimieren, wird in [2] gezeigt, dass ein 400 kSps, 10-Bit Delta-Sigma-Wandler zur digitalen Regelung von einem Abwärtswandler mit 70 kHz-Transitfrequenz nicht leistungsfähig genug ist.

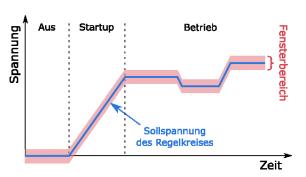

Abbildung 2: Darstellung des Fenster-Konzepts im Spannungs-Zeit-Diagramm.

### C. Spezielle AD-Wandler-Konzepte

[7] schlägt einen speziell für den Einsatz in digital geregelten Schaltwandlern vorgesehenen Voltage-Controlled-Oscillator basierenden Ansatz zur AD-Wandlung vor. Bei diesem Ansatz wird die Ausgangsspannung des Schaltwandlers genutzt, um die Frequenz eines Ringoszillators zu variieren. Nachteil dieses Konzepts ist, dass ein großer Eingangsspannungsbereich abgedeckt werden muss. Zusätzlich verändert sich die Auflösung in Abhängigkeit der Ausgangsspannung des Schaltwandlers.

Auch in [8] wird ein Ringoszillator verwendet, um eine Spannung zunächst in eine Frequenz zu wandeln, die dann wiederum in einen digitalen Wert umgewandelt wird. Im Gegensatz zu [7] wird die Spannungsdifferenz zwischen Ausgangspannung des Schaltwandlers und Sollspannung des Regelkreises ausgewertet (siehe dazu auch Fenster-Konzept, Abschnitt III.A), daher muss kein großer Eingangsspannungsbereich abgedeckt werden. Die Umwandlung der Frequenz in einen digitalen Wert ist im vorgeschlagenen Konzept sehr aufwändig und flächenintensiv, weil eine große Anzahl von Zählern benötigt wird.

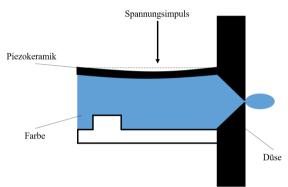

Delay-Line basierende AD-Wandler-Konzepte benötigen keine Zähler. Außerdem muss kein großer Eingangsspannungsbereich abgedeckt werden, weil die Spannungsdifferenz zwischen Sollspannung und Ausgangsspannung des Regelkreises ausgewertet wird. Die Delay-Line AD-Wandler-Konzepte können aufgrund ihrer einfachen Architektur und sich wiederholender Grundelemente mit geringem schaltungstechnischem Aufwand implementiert werden. Beim Delay-Line AD-Wandler wird die Laufzeitdifferenz zweier Signale ausgewertet, die durch kurze Verzögerungsketten propagieren. Dies ermöglicht hohe Wandlungsraten bei sehr kleinen Latenzzeiten [9], [10], [11].

### III. DELAY-LINE AD-WANDLER

### A. Fenster-Konzept

Das Fenster-Konzept eignet sich besonders für digital geregelte Schaltwandler. Charakteristisch für das Fenster-Konzept ist, dass die Ausgangsspannung nur

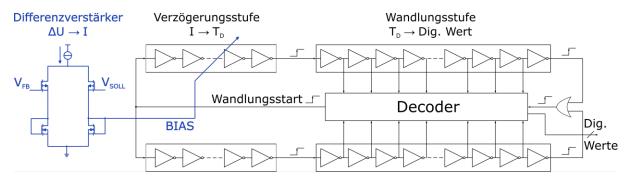

Abbildung 3: Blockschaltbild des Delay-Line AD-Wandlers.

in einem kleinen Bereich (Fensterbereich) um die Sollspannung des Regelkreises herum gewandelt wird. Dies ist zulässig, weil sich im stabilen Regelkreis die Ausgangsspannung des Schaltwandlers immer in einem kleinen Bereich um die Sollspannung befindet. Abbildung 2 zeigt den sich verändernden Fensterbereich in Abhängigkeit der Sollspannung des Regelkreises. Bei konventionellen AD-Wandlern wird dauerhaft der komplette Spannungsbereich gewandelt. Im Gegensatz zu konventionellen AD-Wandlern wird also nur der relevante Spannungsbereich gewandelt. Dadurch kann ein AD-Wandler mit Fenster-Konzept mit einer weitaus geringeren Auflösung (in Bit) auskommen, und dabei dennoch dieselbe Ausgangsspannungsauflösung wie ein konventioneller, hochauflösender AD-Wandler erreichen. Das Fenster-Konzept stellt auch im Startup-Fall (beim Startup wird die Sollspannung rampenförmig von 0 V auf die Zielspannung erhöht) und bei variablen Spannungsveränderungen während des Betriebs keine Einschränkung dar. Der in diesem Beitrag präsentierte Delay-Line AD-Wandler arbeitet nach diesem Fenster-Konzept.

### B. Struktur

Der Delay-Line AD-Wandler kann in drei Stufen unterteilt werden, die Differenzverstärker-, die Verzögerungs- und die Wandlungsstufe.

In der ersten Stufe, in Abbildung 3 ganz links, wird mit Hilfe eines Differenzverstärkers ein zur Spannungsdifferenz zwischen der Sollspannung des Regelkreises  $V_{\rm SOLL}$  und der rückgeführten Ausgangsspannung des Regelkreises  $V_{\rm FB}$  proportionaler Strom  $I_{\rm bias}$  gebildet.

Eine zweite Stufe besteht aus einer variablen Verzögerungsstufe. Die Verzögerung  $T_{\rm D}$  der stromgesteuerten Inverterkette wird durch den von der ersten Stufe bereitgestellten Strom  $I_{\rm bias}$  bestimmt. Eine dazu parallel arbeitende Verzögerungskette wird mit einem konstanten Referenzstrom versorgt und erzeugt damit eine konstante Verzögerung.

Die Wandlungsstufe besteht aus zwei gleichartigen Inverterketten, die mit konstanter Verzögerung arbeiten. Weiterhin beinhaltet die Wandlungsstufe einen Decoder, der die Zustände zwischen den einzelnen Invertergliedern der Verzögerungsketten zum passenden Zeitpunkt abfragen kann. Das Ausgangssignal des Decoders ist der digitale Ausgangswert des AD-Wandlers.

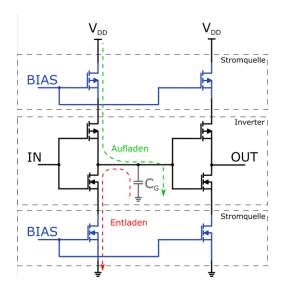

Die Inverterketten aus Stufe zwei und drei sind aus stromgesteuerten Invertergliedern aufgebaut. Abbildung 4 zeigt den Aufbau zweier solcher Inverterglieder.

Der Delay-Line AD-Wandler zeichnet sich mit seinem einfachen Aufbau aus Differenzverstärker, mehreren gleichartigen Inverterzellen und einem Decoder durch geringe Komplexität und geringen schaltungstechnischen Aufwand aus.

### C. Funktionsweise

Eine Wandlung wird durch ein rechteckförmiges Wandlungsstart-Signal gestartet. Dieses Signal breitet sich sowohl in der Referenzverzögerungskette, die eine konstante Verzögerung aufweist, als auch in der variablen Verzögerungskette, die abhängig von der Spannungsdifferenz der Ausgangsspannung des Regelkreises und der Sollspannung des Regelkreises eine variable Verzögerung aufweist, zunächst in der Verzögerungsstufe aus. Das Wandlungsstart-Signal wird dadurch in den beiden Pfaden unterschiedlich verzögert (es sei denn Ausgangs- und Sollspannung des Regelkreises stimmen exakt überein). Die unterschiedlich verzögerten Signale gelangen anschließend in die Wandlungsstufe. Diese wird zur Auswertung der Laufzeitdifferenz benötigt. Das Signal, welches insgesamt schneller durch seinen Verzögerungspfad propagiert, löst das Aufnahme-Signal aus. Sobald dieses Aufnahme-Signal gesetzt wird, liest der Decoder die Zustände in der Wandlungsstufe aus. Der Decoder bildet zunächst die Differenz der beiden gegenüberliegenden Zustände und wandelt anschließend den inhärent entstehenden Thermometer-Code in einen Binärcode um.

Der Delay-Line AD-Wandler zeichnet sich durch eine sehr kurze Latenzzeit aus. Die Latenzzeit wird definiert durch die Zeitdauer von Wandlungsstart bis zur Generierung des Aufnahme-Signals. Dazu kommt noch die Auswertungszeit des Decoders, die aber vernachlässigbar klein ist. Die Latenzzeit wird also in

Abbildung 4: Zwei stromgesteuerte Inverterglieder in Reihenschaltung.

keinem Fall größer werden als die Laufzeit des Signals durch die Inverterkette, die mit konstanter Verzögerung arbeitet. Kleiner wird die Latenzzeit, wenn das Signal durch die Inverterkette mit variabler Verzögerung schneller propagiert als durch die Inverterkette mit konstanter Verzögerung.

Die Auflösung hängt von der Anzahl der Inverterglieder in der Wandlungsstufe ab. Die Auflösung kann daher erhöht werden, indem die Anzahl der Inverterglieder erhöht wird.

Ein Vorteil des Delay-Line Konzepts ist, dass bedingt durch die sequentielle Ausbreitung des Wandlungsstart-Signals keine Monotonie-Fehler auftreten können.

### D. Schaltungstechnische Implementierung

Der eingesetzte Differenzverstärker enthält zusätzlich zum in Abbildung 3 gezeigten Aufbau noch einen Source-Degeneration-Widerstand am Differenzpaar, um die Linearität der Verstärkerstufe zu verbessern.

Die einzelnen stromgesteuerten Inverterglieder (siehe Abbildung 4) sind so dimensioniert, dass bei konstantem Referenzstrom eine nominale Verzögerung von 500 ps pro Inverterglied entsteht.

Die Verzögerungsstufe besteht pro Zweig aus 99 einzelnen Invertergliedern. Dadurch entsteht eine Gesamtverzögerung von 49,5 ns. Eine Reduktion der Anzahl der Inverterglieder in der Verzögerungsstufe wäre denkbar, allerdings muss der Umladestrom dann einen sehr großen Strombereich abdecken, um die notwendigen Verzögerungen einzustellen.

Die Wandlungsstufe setzt sich pro Zweig aus 33 einzelnen Invertergliedern zusammen. Dadurch entsteht hier eine weitere Verzögerung von 16,5 ns.

Der Decoder liest die Zustände zwischen den einzelnen Invertergliedern aus und erzeugt daraus den zugehörigen Binärcode. Dabei wird berücksichtigt, dass die Signale jedes zweite Inverterglied invertiert vor-

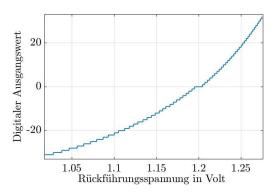

Abbildung 5: Übertragungskennlinie des Delay-Line AD-Wandlers.

liegen. Dieser Digitalteil kann mit Hilfe der Hardwarebeschreibungssprache VHDL erzeugt werden.

Es ergibt sich mit diesem Aufbau eine Latenzzeit von 66 ns (plus Rechenzeit des Decoders). Die Auflösung liegt bei 6 Bit. Die Wandlungsrate des Delay-Line AD-Wandlers kann bis zu 30 MSps betragen.

### IV. SIMULATIONSERGEBNISSE

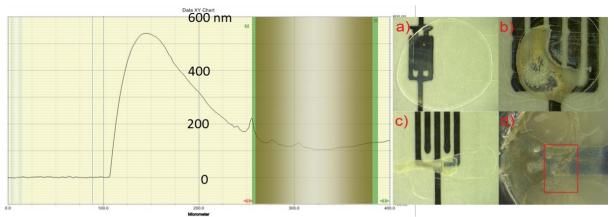

### A. Übertragungskennlinie

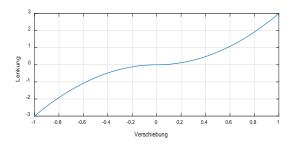

Abbildung 5 zeigt die Übertragungskennlinie des Delay-Line AD-Wandlers als Funktion der Rückführungsspannung. Der Sollwert des Regelkreises liegt bei 1,2 V. Die Rückführungsspannung ist die mit einem hochohmigen Spannungsteiler heruntergeteilte Ausgangsspannung (vgl. Abbildung 1). Die Kennlinie weist streng monotones und nichtlineares Übertragungsverhalten auf.

Das nichtlineare Übertragungsverhalten ist durch das Umschaltverhalten der Inverterkette bedingt. Die Last eines Inverters bestimmt das zeitliche Verhalten der Umschaltung maßgeblich. Bei der verwendeten Inverterkette sind gleichartige Inverter in Reihe geschaltet. Die Last des jeweiligen Inverters ist daher die Gatekapazität  $C_G$  des Folge-Inverters (siehe dazu auch Abbildung 4). Daher ergibt sich nach

$$T_D = \frac{C_G \cdot U}{I_{bias}}$$

ein invers-proportionales Verhalten zwischen der Umschaltezeit  $T_{\rm D}$  und dem Umladestrom  $I_{\rm bias}$ .

Die Übertragungskennlinie zeigt weiterhin, dass die Auflösung mit steigender Rückführungsspannung feiner wird. Auffallend ist außerdem, dass der digitale Ausgangswert "0" über einen breiteren Spannungsbereich erzielt werden kann als die digitalen Ausgangswerte "-1" oder "1". Dies ist hilfreich, es kann dadurch eine hohe Auflösung des AD-Wandlers erzielt werden ohne gleichzeitig Limit Cycle Oscillations im Regelkreis befürchten zu müssen [12], [13].

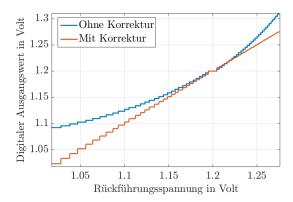

Die digitalen Werte können direkt (ohne Korrektur) weiterverwendet werden. Alternativ können die Werte so korrigiert werden, dass die digitalen Werte den korrekten analogen Spannungswerten zugeordnet

Abbildung 6: Korrigierte und nicht-korrigierte Übertragungskennlinie des Delay-Line AD-Wandlers.

werden. Dazu ist eine Lookup-Tabelle notwendig, die die Zuordnung eines digitalen Ausgangswertes und dem jewiligen analogen Rückführungsspannungswert enthält. Abbildung 8 zeigt das Übertragungsverhalten für eine Weiterverwendung der digitalen Werte ohne Korrektur und Korrektur. mit Auflösungsabhängigkeit der Übertragungskennlinie nach Korrektur der Nichtlinearität bleibt auch bestehen.

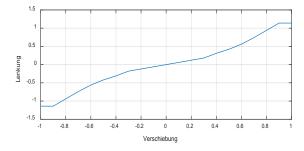

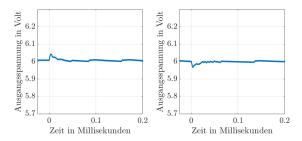

### B. Lastsprungverhalten

Abbildung 7 zeigt das Ausregelverhalten eines digital geregelten 500 kHz-getakteten Abwärtswandlers mit einer Transitfrequenz von 70 kHz. Die Ausgangsspannung liegt bei 6V und die Eingangsspannung ist 14 V. Der Lastsprung erfolgt von 0,6 A auf 0,3 A Laststrom (links) und von 0,3 A auf 0,6 A (rechts). Die Simulationsergebnisse zeigen, dass der Delay-Line AD-Wandler eine passende Auflösung und gleichzeitig eine so geringe Latenzzeit bietet, dass bei 70 kHz keine Stabilitätsprobleme auftreten.

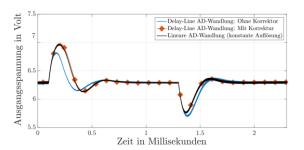

Abbildung 8 zeigt das Lastsprungverhalten von 500 kHz-getakteten Aufwärtswandlern mit 2 kHz-Transitfrequenz. Bei dieser niedrigen Transitfrequenz wird die Auswirkung der Nichtlinearität der Übertragungskennlinie deutlich. Die Ausgangsspannung liegt bei 6,3 V und die Eingangsspannung ist 3,5 V. Der Lastsprung erfolgt von 0,6 A auf 0,3 A Laststrom (und zurück). Dargestellt ist das Lastsprungverhalten eines Aufwärtswandlers mit Delay-Line AD-Wandler ohne Korrektur der Nichtlinearität, mit Korrektur der Nichtlinearität und eines idealen AD-Wandlers mit linearem Verhalten.

Der Aufwärtswandler mit Delay-Line AD-Wandler mit Korrektur der Nichtlinearität und Aufwärtswandler mit idealem AD-Wandler mit linearem Verhalten zeigen nahezu identisches Verhalten. Der Aufwärtswandler mit Delay-Line AD-Wandler ohne Korrektur der Nichtlinearität zeigt dagegen bei Lastabwurf ein verbessertes Ausregelverhalten, während er bei Lastzunahme ein schlechteres Ausregelverhalten zeigt.

Abbildung 7: Lastsprungverhalten eines digital geregelten Ab-wärtswandlers mit 70 kHz Transitfrequenz.

Abbildung 8: Lastsprungverhalten von digital geregelten Aufwärtswandlern

Dieses unterschiedliche Verhalten kann mit Hilfe von Abbildung 8 erklärt werden. Bei hoher Spannung liefert der AD-Wandler aufgrund der Nichtlinearität der Übertragungsfunktion dem Regler eine überhöhte Regelabweichung (siehe rechte Hälfte der Kennlinie). Dementsprechend reagiert der Regler mit einer entsprechend stärkeren Gegenreaktion. Ein solches Verhalten gleicht verschiedenen Ansätzen zur nichtlinearen Regelung [4], [5]. Bei kleiner Spannung (linke Hälfte der Kennlinie) bekommt der Regler die Information, dass die Spannungsabweichung weniger groß ist, als dies tatsächlich ist. Die Reaktion des Reglers fällt dadurch entsprechend zu schwach aus. Der Ausregelvorgang verschlechtert sich.

### V. FAZIT

Digital geregelte Schaltwandler zeigen weniger Parameterschwankungen, sind flexibler und profitieren mehr von kleiner werdenden Strukturgrößen integrierter Chips als analog geregelte Schaltwandler. Die AD-Wandlung in digital geregelten Schaltwandlern muss mit geringer Latenzzeit und hoher Auflösung erfolgen. Konventionelle AD-Wandler-Konzepte sind daher für digital geregelte Schaltwandler meist ungeeignet. Das vorgestellte Delay-Line AD-Wandler-Konzept kommt mit verhältnismäßig geringem Schaltungsaufwand durch Verwendung des Fenster-Konzepts auf eine gute ausgangsspannungsbezogene Auflösung und auf eine äußerst niedrige Latenzzeit. Simulationsergebnisse eines 500 kHz-getakteten Abwärtswandlers zeigen, dass Regelkreise mit hohen Transitfrequenzen mit einem 6-Bit, 66 ns-Latenzzeit Delay-Line AD-Wandler stabil geregelt werden können.

### LITERATURVERZEICHNIS

- [1] B.J. Patella, A. Prodic, A. Zirger and D. Maksimovic, "High-frequency digital PWM controller IC for DC-DC converters," in *IEEE Transactions on Power Electronics*, vol. 18, no. 1, pp. 438-446, Jan 2003.

- [2] S. Quenzer-Hohmuth, S. Ritzmann, T. Rosahl, and B. Wicht, "Challenges and implementation aspects of switched-mode power supplies with digital control for automotive applications", in *Advances in Radio Sciences*, in press, 2016.

- [3] J. Morroni, R. Zane, and D. Maksimovic, "Design and Implementation of an Adaptive Tuning System Based on Desired Phase Margin for Digitally Controlled DCDC Converters," in *IEEE Transactions on Power Electronics*, vol. 24, no. 2, pp. 559-564, Feb. 2009.

- [4] Mingzhi He, and Jianping Xu, "Nonlinear PID in Digital Controlled Buck Converters," in APEC 2007 - Twenty Second Annual IEEE Applied Power Electronics Conference, vol., no., pp. 1461-1465, Feb. 25 2007- March 1 2007.

- [5] V. Yousefzadeh and S. Choudhury, "Nonlinear digital PID controller for DC-DC converters," in APEC 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, Austin, TX, 2008, pp. 1704-1709.

- [6] S. Quenzer-Hohmuth, S. Ritzmann, T. Rosahl and B. Wicht, "Boost converter with load dependent adaptive controller for improved transient response," 2016 12th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Lisbon, Portugal, 2016, pp. 1-4.

- [7] M. Z. Straayer and M. H. Perrott, "A 12-Bit, 10-MHz Bandwidth, Continuous-Time ΣΔ ADC With a 5-Bit, 950-MS/s VCO-Based Quantizer," in *IEEE Journal of Solid-State Circuits*, vol. 43, no. 4, pp. 805-814, April 2008.

- [8] Jinwen Xiao, A. V. Peterchev, Jianhui Zhang and S. R. Sanders, "A 4-µa quiescent-current dual-mode digitally controlled buck converter IC for cellular phone applications," in *IEEE Journal of Solid-State Circuits*, vol. 39, no. 12, pp. 2342-2348, Dec. 2004.

- [9] Huei-Shan Chen, Chun-Hung Yang, Chien-Hung Tsai and Guan-Lin Li, "Design and implementation of window delayline ADC for low-power DC-DC SMPS," 2012 IEEE 13th Workshop on Control and Modeling for Power Electronics (COMPEL), Kyoto, 2012, pp. 1-4.

- [10] A. Parayandeh and A. Prodic, "Programmable Analog-to-Digital Converter for Low-Power DC–DC SMPS," in *IEEE Transactions on Power Electronics*, vol. 23, no. 1, pp. 500-505, Jan. 2008.

- [11] Y. Sun, V. Adrian and J. S. Chang, "Design of a variable-delay window ADC for switched-mode DC-DC converters," 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, 2015, pp. 1642-1645.

- [12] H. Peng, A. Prodic, E. Alarcon and D. Maksimovic, "Modeling of Quantization Effects in Digitally Controlled DC–DC Converters," in *IEEE Transactions on Power Electronics*, vol. 22, no. 1, pp. 208-215, Jan. 2007.

- [13] A. V. Peterchev and S. R. Sanders, "Quantization resolution and limit cycling in digitally controlled PWM converters," 2001 IEEE 32nd Annual Power Electronics Specialists Conference, 2001. PESC, Vancouver, BC, 2001, pp. 465-471 vol.2.

Samuel Quenzer-Hohmuth erhielt den akademischen Grad des Bachelor of Engineering in Elektrotechnik im Jahr 2012 von der Dualen Hochschule Stuttgart und den Grad des Master of Science in Leistungs- und Mikroelektronik im Jahr 2015 von der Hochschule Reutlingen. Er ist derzeit Akademischer Mitarbeiter am Robert Bosch Zentrum für Leistungselektronik an der Hochschule Reutlingen.

Cedric Leonel Jiago Teffo erhielt den akademischen Grad des Bachelor of Engineering in Mechatronik mit dem Schwerpunkt Mikroelektronik im Jahr 2014 von der Hochschule Reutlingen und den Master of Science in Leistungs- und Mikroelektronik im Jahr 2016 am Robert Bosch Zentrum für Leistungselektronik der Hochschule Reutlingen. Er ist derzeit Entwicklungsingenieur bei der Robert Bosch GmbH in Reutlingen.

Steffen Ritzmann erhielt den akademischen Grad des Diplomingenieurs in Technischer Informatik im Jahr 2007 von der Technischen Universität Berlin. Er ist derzeit Entwicklungsingenieur für integrierte Schaltungstechnik bei der Robert Bosch GmbH in Reutlingen.

Thoralf Rosahl erhielt den akademischen Grad des Diplomingenieurs im Jahr 1990 von der Technischen Universität Dresden. Seit 1991 arbeitet er bei der Robert Bosch GmbH als Entwicklungsingenieur für integrierte Schaltungstechnik in Reutlingen.

Bernhard Wicht erhielt den akademischen Grad des Diplomingenieurs im Jahr 1996 von der Technischen Universität Dresden und den Grad Dr.-Ing. im Jahr 2002 von der Technischen Universität München. 2003-2010 war er im Geschäftsbereich Mixed Signal Automotive bei Texas Instruments, Freising, verantwortlich für die Entwicklung von Smart Power ICs. Seit September 2010 ist er Professor für integrierte Schaltungen am Robert Bosch Zentrum für Leistungselektronik an der Hochschule Reutlingen.

# Entwicklung eines Feldbusmodules "CAN" für eine neue Industriesteuerungsgeneration "IndraControl XM"

Mirko Auth

Zusammenfassung—Ein neues Feldbusmodul "CAN" ist für die neue Industriesteuerung "IndraControl XM" von Bosch Rexroth zu entwickeln. Die ersten Schritte sind die Auswahl des Gehäuses, die Evaluierung der verschiedenen CAN Controller Lösungen und die Hardwareentwicklung mit FPGA Core. Danach findet die Inbetriebnahme der Hardware statt. Der abschließende Test des entwickelten Feldbusmoduls "CAN" mit der neuen "IndraControl XM"-Steuerung stellt die Funktion sicher.

Schlüsselwörter—CAN, Industriesteuerung, Hardware, IP-Core, FPGA, Inbetriebnahme

### I. EINLEITUNG

Die Automatisierung, Digitalisierung und Verknüpfung nimmt in der Automobil-, Schifffahrt-, Luftfahrtindustrie und in weiteren Industriezweigen eine immer größere und bedeutendere Rolle ein. Zum Erreichen einer möglichst großen Marktabdeckung ist es für heutige Konzerne wichtig, dass neben schnellen und leistungsfähigen speicherprogrammierbaren Steuerungen (SPS) und Industrie-PC's auch alle bedeutenden Feldbusse, ob zentral oder dezentral, unterstützt werden. Feldbusse dienen der Kommunikation zwischen Steuerungen oder Industrie-PCs mit Aktoren und Sensoren. Einer der bedeutendsten Feldbusse in der Automobilindustrie ist der CAN-Feldbus. Es handelt sich dabei um ein serielles Bussystem mit dem ursprünglichen Ziel, die Kabellängen im Auto zu reduzieren und somit Gewicht zu sparen. Mit der Zeit ist der CAN-Bus im industriellen Umfeld immer bedeutender geworden. In der Automobilindustrie hat sich vor allem das Kommunikationsprotokoll CANopen, basierend auf CAN, durchgesetzt. Dieses Protokoll ist mittlerweile auch in der Schifffahrt zu finden.

### II. ANFORDERUNGEN AN DAS FELDBUSMODUL "CAN"

Ziel ist die Entwicklung eines funktionsfähigen Prototyps des Feldbusmoduls "CAN", das an die neuen

Mirko Auth, mirko.auth@boschrexroth.de, Bosch Rexroth AG Berliner Str. 25 64711 Erbach

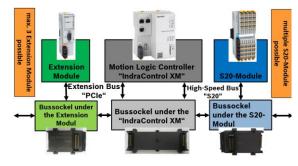

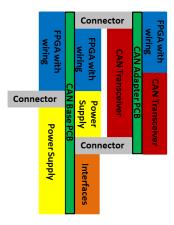

Abbildung 1: Konzept der neuen Industriesteuerungsgeneration "IndraControl XM" .

Industriesteuerungen der Generation "IndraControl XM" anschließbar ist. Dieses Feldbusmodul soll die geforderten EMV-Eigenschaften erfüllen und 4 CAN Schnittstellen besitzen.

Zunächst werden alle Realisierungsmöglichkeiten aufgezeigt, bewertet und die Beste realisiert. Danach werden alle nötigen Bauteile ausgewählt, ein Gehäusekonzept ausgearbeitet und das Schaltbild eingegeben. Es folgen das Layout, die Fertigung und die Bestückung der Leiterplatte. Anschließend findet die Hardwareinbetriebnahme statt. Parallel kann die benötigte Software auf einem Evaluation Board implementiert und später auf die neue entwickelte Hardware übertragen werden. Ein abschließender Test mit einem SPS-Programm und weiteren CAN-Modulen bestätigt die Funktionalität des CAN Feldbusses.

Das Ergebnis der Entwicklung ist ein Prototyp des Feldbusmoduls "CAN" für die Industriesteuerungen der Generation "XMxx" in einem passenden Gehäuse. Dieser Prototyp soll die Anforderungen des Marktes erfüllen.

# III. KONZEPT DER NEUEN INDUSTRIESTEUERUNG "INDRACONTROL XM"

Im Zentrum der neuen Industriesteuerungsgeneration der Bosch Rexroth AG stehen die unterschiedlichen Steuerungen "IndraControl XM" mit ihren festgelegten Schnittstellen zu den Erweiterungsmodulen.

Links können unterschiedliche Extension Module, die verschiedene Feldbusse realisieren, angeschlossen werden. Die Anzahl an Extension Modulen ist abhängig von der Industriesteuerung "IndraControl XM". Auf der rechten Seite besteht die Möglichkeit S20-

Module (z.B. IO-Module) zu ergänzen. Die Anzahl ist nicht begrenzt.

Unterschiedliche "Bussockel", die sich in der Hutschiene befinden, transportieren die Signale von der Industriesteuerung "IndraControl XM" zu den Modulen. Der proprietäre Bus S20 verbindet die S20-Module mit der Industriesteuerung und der Extension Bus, basierend auf PCIexpress, verbindet die Extension Module.

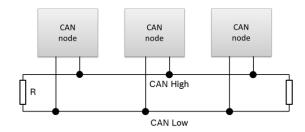

### IV. GRUNDLAGE ZUM FELDBUS "CAN"

Der Controller Area Network (CAN)-Feldbus wurde 1983 von der Robert Bosch GmbH entwickelt. Gemeinsam mit der Fa. Intel ist 1989 der erste CAN-Controller vorgestellt worden.

Beim Feldbus CAN handelt es sich um ein echtzeitfähiges, zweiadriges Bussystem mit Linienstruktur. Die Signalübertragung erfolgt meist über ungeschirmte, verdrillte Drahtleitungen als Differenzspannungsübertragung.

# V. Entscheidungsfindung für die Realisierung des Feldbusmoduls "CAN"

A. Anbindung an die neue Industriesteuerung als S20oder Extension Modul

Das Feldbusmodul "CAN" wird als Extension Modul realisiert aufgrund der höheren Performance von PCIexpress im Vergleich zum S20-Bus. PCIexpress besitzt eine Netto-Bandbreite von 0,5GBit/s und der S20-Bus von 100MBit/s.

Zusätzlich besteht bei PCIe die Möglichkeit die Bandbreite weiter zu erhöhen, indem man auf eine neue PCIe-Version umsteigt. Diese ist beim "S20"-Bus aktuell nicht vorgesehen.

Des Weiteren kann bei PCIe DMA (Direct Memory Access) eingesetzt werden. Mittels DMA ist der Datentransfer vom Modul direkt in den Arbeitsspeicher der CPU, ohne Belastung des Prozessors der Industriesteuerung, möglich.

### B. Softwarerealisierung des CAN-Feldbusses

Im nächsten Schritt werden die verschiedenen Realisierungsmöglichkeiten für den CAN-Feldbus beleuchten, wobei ausschließlich auf die entscheidenden Unterschiede (FPGA, CAN Controller...) eingegangen wird.

Die Ziele bei der Realisierung der CAN Schnittstellen sind:

- hohe Performance / hohe Datenübertragungsrate

- kostenbewusste Lösung (Bauteilkosten, Platzbedarf auf der Leiterkarte)

- Modularität, Erweiterbarkeit und Flexibilität der Lösung (Möglichkeit des Exportierens auf andere Projekte)

Abbildung 2: Struktur des CAN-Fieldbuses

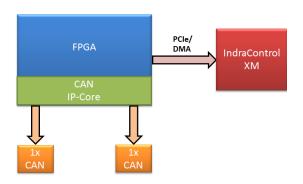

Abbildung 3: Softwarerealisierung - FPGA mit CAN IP-Core

Die folgenden Möglichkeiten werden betrachtet:

• Mikrocontroller mit internen CAN Controllern Bei dieser Lösung können die erforderlichen Datenübertragungsraten erreicht werden, auch wenn ein weiterer IC nötig ist. Dies ist der Fall, da der Mikrocontroller kein PCIexpress Interface besitzt und somit z.B. ein FPGA für die Anbindung an die Industriesteuerung gebraucht wird.

Dadurch steigen die Bauteilkosten und der benötigte Platz auf der Leiterplatte. Des Weiteren sind zwei Mikrocontroller nötig um die 4 CAN Schnittstellen zu realisieren.

### • Stand-alone CAN controller

Die Performance dieser Lösung ist gut wobei auch die stand-alone CAN Controllern kein PCIexpress Interface haben. Außerdem sind 2 ICs nötig um die 4 CAN Schnittstellen zu realisieren. Folglich fallen erneut hohe Bauteilkosten an und es wird ein großer Leiterplattenplatz benötigt.

### • Hochintegrierter Netzwerk-Controller

Der hochintegrierte Netzwerk-Controller besitzt bis zu 3 CAN Schnittstellen. Deshalb sind 2 ICs nötig. Eine PCI zu PCIexpress Bridge muss auf der Leiterplatte vorgesehen werden, da der Controller kein PCIexpress Interface besitzt. Dies bedeutet erneut einen hohen Platzbedarf auf der Leiterplatte und hohe Bauteilkosten.

### • FPGA mit CAN IP-Core

Der Einsatz eines FPGAs mit CAN Controller IP-Core bietet hohe Modularität, Flexibilität und die

maximale Performance durch den Einsatz von DMA. Die Bauteilkosten und der benötigte Leiterplatten Platz sind minimal, da nur ein FPGA nötig ist.

Nach Bewertung aller Vor- und Nachteilen ist die beste Lösung der Einsatz eines FPGAs mit CAN IP-Core; maximale Performance und geringste Kosten.

Als CAN IP-Core kommt der "M\_CAN" von Bosch zum Einsatz.

### C. Gehäuselösung

Die Gehäuse werden durch eine kooperierende Firma hergestellt. Die einzige Möglichkeit ist der Einsatz des schmalen Extension Modul Gehäuses, da dieses einen mechanischen Versteckschutz besitzt. Der Sinn dieses Schutzes ist, dass keine Anwender das Modul auf den S20-Bus als S20-Modul montiert und dadurch die Hardware zerstört. Allerdings sind nur 2 CAN Schnittstellen pro Modul mit diesen Gehäuse realisierbar. Ansonsten ist mehr Leiterplattenplatz nötig und somit ein breiteres Gehäuse. Allerdings besitzen diese keinen mechanischen Versteckschutz und eine Umsetzung dieses Versteckschutzes würde sehr hohe Entwicklungskosten und lange Entwicklungszeit bedeuten.

Folglich ist die einzige mögliche Lösung die CAN Schnittstellen auf 2 pro Modul zu reduzieren. Somit benötigt der spätere Anwender 2 Module für 4 CAN Schnittstellen.

### VI. HARDWAREENTWICKLUNG UND INBETRIEBNAHME

Nachdem nun alle Anforderung an das Feldbusmodul "CAN" feststehen, kann die Hardwareentwicklung beginnen.

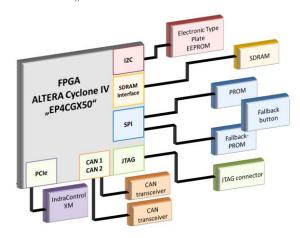

Es sind zwei Leiterplatten nötig. Auf der einen ist die Spannungsversorgung, das FPGA mit PROMs, ein Steckverbinder für den Anschluss an die Industriesteuerung "IndraControl XM" und Steckverbinder zur 2. Leiterplatte. Auf der anderen befinden sich die CAN Transceiver, die die isolierte CAN Spannung und die CAN-Signale CAN\_High und CAN\_Low erzeugen. Zusätzlich sind die Steckverbinder zur anderen Leiterplatte vorhanden.

Zunächst werden alle Komponenten ausgewählt eine Leistungsbetrachtung aller ICs und Verbraucher durchgeführt. Dies ist für die Dimensionierung der Spannungsversorgung wichtig. Danach wird das Schaltbild in das CAE-Tool eingegeben und das Layout der Leiterplatte erstellt. Anschließend werden die Leiterplatten gefertigt und bestückt.

Zuletzt findet die Inbetriebnahme mit Messen der Spannungen und Ströme sowie der Überprüfung der einzelnen Funktionen statt. Zum Beispiel wird die

Abbildung 4: Gehäuse des Extension Moduls CAN.

Abbildung 5: Blockdiagramm Extension Modul CAN.

Oszillatorfrequenz nachgemessen und der Lese- und Schreibvorgang in die PROMs verifiziert.

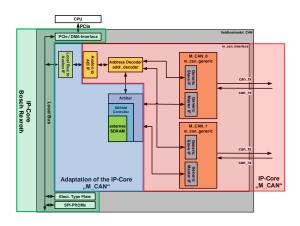

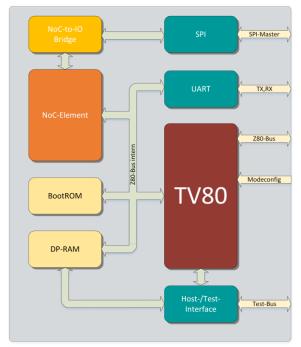

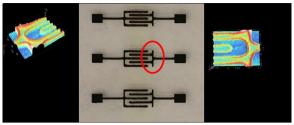

### VII. FPGA SYNTHESE UND VERIFIKATION DES VHDL CODES

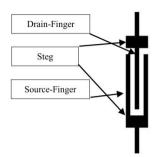

Die FPGA Synthese basiert auf dem CAN IP-Core "M\_CAN" von Bosch ("rot" markierter Bereich, siehe Abbildung 6) und den firmeneigenen IP-Cores ("grün" markierter Bereich, siehe Abbildung 6).

Über das PCIexpress/DMA-Interface wird die Anbindung des Feldbusmoduls "CAN" zu den Industriesteuerungen der Generation "IndraControlXM" hergestellt. Der Datentransfer im Feldbusmodul "CAN" findet über den Local-Bus statt. An diesem sind die IP-Cores des elektronischen Typschilds, der SPI-PROMs und des CANs angeschlossen. Der CAN IP-Core besitzt ein Avalon Interface mit einer Datenwortbreite von 32bit. Da der Local-Bus eine Datenwortbreite von 64Bit hat, ist ein Adapter nötig. (Local-Bus to Avalon Interface).

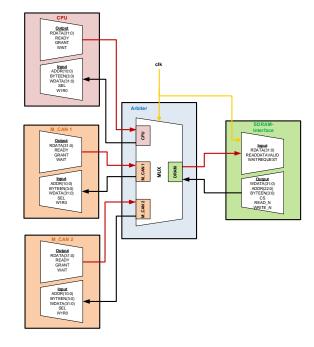

Der IP-Core "M\_CAN" besteht aus einem Address Decoder, der die Adresszuordnung für die beiden CAN Instanzen (M\_C\_AN0 und M\_CAN\_1) und das RAM übernimmt. Jeder CAN Controller hat ein Generic Slave Interface für die Verbindung zur Host CPU und ein Generic Master Interface für den Zugang zum RAM. Die Zugriffsüberwachung auf das RAM übernimmt der Arbiter, der Konflikte und Kollisionen bei gleichzeitigem Zugriff löst.

### A. Adapter vom Local-Bus zum Avalon-Bus

Das Feldbusmodul "CAN" basiert auf dem Local – Bus wobei der CAN IP-Core ein Avalon-Bus Interfase besitzt. Bis auf die Wortbreite sind alle Eigenschaften vergleichbar.

Der Local-Bus basiert auf 64 Bit und der Avalon-Bus auf 32 Bit Daten-Worten. Ein 64-Bit Zugriff wird in zwei 32-Bit Zugriffe umgewandelt. Beide arbeiten mit Wortadressen, nicht mit Byteadressen. Durch Ergänzen einer 0 bzw. einer 1 an die 64-Bit Adresse von rechts entsteht die 32-Bit Adresse.

Beim Schreiben werden die 64 Bit Local-Bus Daten auf zwei 32 Bit breite Avalon-Bus Daten aufgesplittet (Write). Beim Lesen (Read) erfolgt das Zusammenfügen der zwei 32 Bit breiten Avalon-Bus Daten zu einem 64 Bit breiten Local-Bus Datum.

Zum Detektieren, ob die oberen oder unteren Bytes auszuwählen sind, dienen die Byte-Enable Bits des Local-Busses.

# B. Integration des externen SDRAMs mit neuem Arbiter

Da das dual-port message RAM des CAN IP-Cores zu klein ist, wird ein externes SDRAM an das FPGA angeschlossen. Die Timingsignale "waitrequest" und "readdatavalid" vom SDRAM werden vom mitgelieferten Arbiter des CAN IP-Cores nicht analysiert, da dieser nur SRAMs unterstützt. Aus diesem Grund ist ein neuer Arbiter mit Round-Robin Zugriff nötig. Entweder die CPU der Industriesteuerung "IndraControl XM" oder eine Instanz der "M\_CAN" haben Zugriff auf das SDRAM.

Der SDRAM Controller ist ein IP-Core, der vom FPGA Hersteller mitgeliefert wird.

### C. Verifikation des VHDL-Codes

Ausgangsbasis für die Inbetriebnahme des VHDL-Codes ist der Anschluss des Feldbusmoduls "CAN" an eine SPS der neuen Industriesteuerungsgeneration "IndraControl XM". Mittels "C"-Programm, das auf der "IndraControl XM" läuft, ist ein Zugriff auf die PROMs, den "M\_CAN" mit Decoder, Arbiter, SDRAM und CAN-Controllern möglich.

Um Fehler im implementierten FPGA-Code aufzudecken wird das Tool "SignalTap II" von Altera eingesetzt. Dadurch können die Signalpegel von Steuer-, Adress- und Datenleitungen im FPGA betrachtet und

Abbildung 6: Blockdiagramm – FPGA des Feldbusmoduls "CAN" .

Abbildung 7: Blockdiagramm der FPGA Beschaltung.

Abbildung 8: Daten-, Adress- und Kontrollsignale im Arbiter.

mögliche Fehler ausfindig gemacht werden. Dabei ist es wichtig alle Interfaces zu prüfen, da nur so alle Funktionen gewährleistet werden können.

### VIII. FUNKTIONSTEST DES CAN FELDBUS MIT C-PROGRAMM

Ein abschließender Funktionstest der entwickelten Hardware stellt die CAN-Funktionalität sicher. Ein C-Programm, das beim CAN IP-Core "M\_CAN" mitgeliefert wurde, macht dies möglich. Der Algorithmus sendet Datenpakete von einem zum anderen Teilnehmer. Der zweite Teilnehmer empfängt diese und analysiert sie. Über diesen Test kann die komplette Hardware-Funktionalität getestet und verifiziert werden; von der Spannungsversorgung des Moduls über das FPGA und die CAN-Transceiver.

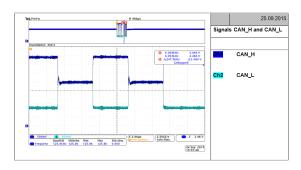

Zusätzlich können die versendeten und empfangenen CAN Protokolle mit einem Oszilloskop gemessen und überprüft werden. Dazu werden die Spannungspegel und die CAN Frames auf Einhaltung der Spezifikation kontrolliert.

### IX. FAZIT

Der Beitrag beschreibt die Realisierung einer Hardwareentwicklung von den Anforderungen bis zum getesteten Prototyp. Ziel war ein Feldbusmodul "CAN", das an die neue Generation von Industriesteuerungen "Indra Control XM" von Bosch Rexroth anschließbar ist.

Zunächst wurden alle Anforderungen betrachtet und die Realisierungsmöglichkeiten aufgezeigt. Danach folgten die Bauteilauswahl, die Schaltbildeingabe ins CAE-Tool, das Layout der Leiterplatten sowie die Fertigung und Bestückung der Leiterplatten. Parallel hat die FPGA-Synthese auf einem Evaluationsboard stattgefunden. Die Inbetriebnahme der entwickelten Hardware und ein abschließender Test der CAN-Funktionalität mit einem C-Programm stellten die Funktionalität des Prototyps sicher.

### LITERATURVERZEICHNIS

- [1] Di Natale, Marco, et al. Understanding and Using the Controller Area Network Communication Protokoll. New York, Dordrecht, Heidelberg, London: Springer, 2012. ISBN 978-1-4614-0313-5.

- [2] Vector Informatik GmbH. Vector Informatik GmbH. [Online] Vector Informatik GmbH, 12. 04 2015. [Zitat vom: 12. 04 2015.] <a href="http://elearning.vector.com/index.php?wbt\_ls\_kapitel\_id=13">http://elearning.vector.com/index.php?wbt\_ls\_kapitel\_id=13</a> 29921&root=376493&seite=vl\_can\_introduction\_de.

- [3] Ravi Budruk, Don Anderson, Tom Shanley. PCI Express System Architecture. Boston, MA: MindShare, Inc., 2004. ISBN: 0321156307.

- [4] Watterson, Dr. Conal. Controller Area Network (CAN) Implementation Guide. Norwood: Analog Devices, 2012.

- [5] Avalon Interface Specifications. [Online] Altera Corporation. [Zitat vom: 09. 05 2015.] https://www.altera.com/content/dam/altera-

Abbildung 9: Oszillogramm: Spannungspegel des CAN Protokolls.

- $www/global/en\_US/pdfs/literature/manual/mnl\_avalon\_spec.\\pdf\ .$

- [6] Bosch. Altera\_FPGA\_Integration\_Guide. [Dokument] s.l.: Bosch, 2015. Rev. 3.2.1.

- [7] Altera. Embedded Peripherals IP User Guide. [Dokument] San Jose: Altera, 2015.

- [8] CAN in Automation. CAN in Automation. [Online] 2001 -2015. [Zitat vom: 31. 01 2015.] http://www.can-cia.org/.

Mirko Auth erhielt den akademischen Grad des Masters of Science in Elektrotechnik im Jahr 2015 von der Hochschule Darmstadt. Er ist Hardwareentwickler bei Bosch Rexroth AG in Erbach.

# Modulares Test- und Emulationssystem für digitale ASIC-Bausteine

Jan-Morten Reiners, Andreas Stiller, Peter Schulz Fachhochschule Dortmund

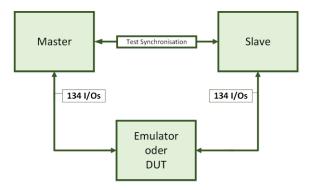

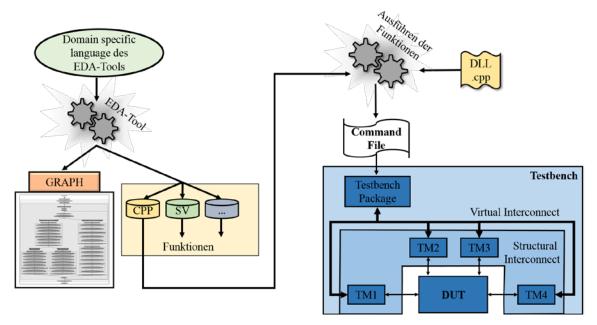

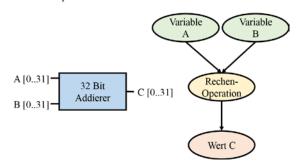

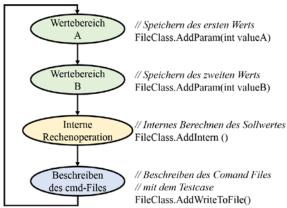

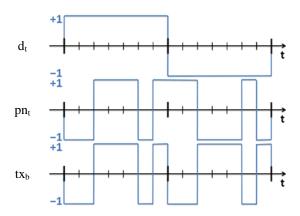

Zusammenfassung—Derzeit befindet sich an der Fachhochschule Dortmund ein ASIC als Test- und Referenzchip für NoC-Komponenten (NoC: Network-on-Chip) in Entwicklung. Für die Prüfung der gefertigten Bausteine wurde ein kombiniertes Test- und Emulationssystem konzipiert.

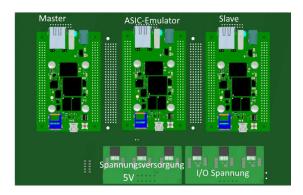

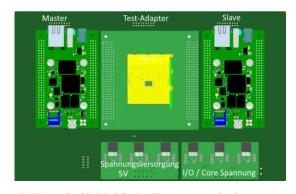

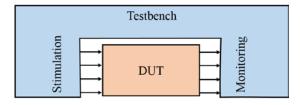

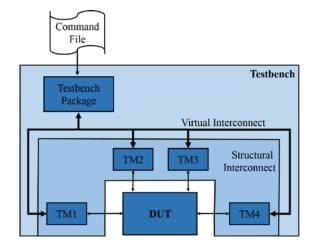

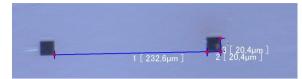

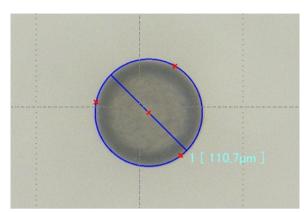

Den Kern dieses Testsystems stellt ein kommerzielles FPGA-Modul mit Dual-Core-ARM (Xilinx Zynq7) dar. Über eine Backplane wird dieses Testermodul an eine DUT-Adaptierung (DUT: Device under Test) angeschlossen. Die DUT-Adaptierung erlaubt alternativ die Bestückung mit einem ASIC-Testsockel-Modul oder einem ASIC-Emulator-Modul. Die Konfiguration mit nur einem Tester-Modul genügt für kleinere ASICs, wie z.B. den via Europractice fertigbaren mini@sics.

Als Ausbaureserve für größere ASIC-Bausteine ist ein Modulplatz für ein zweites Tester-Modul vorgesehen. Bei dem zweiten Tester-Modul kann es sich zukünftig auch um eine Eigenentwicklung zum Testen von Mixed-Signal-ASICs handeln.

Die Modulare DUT-Adaptierung ermöglicht grundsätzlich auch die Konfiguration des Testsystems für den Baugruppentest.

Schlüsselwörter—ASIC-Test, SoPC, FPGA, ASIC-Emulation

### I. EINLEITUNG

Im Rahmen einer Kooperation mit der Universität Bielefeld auf dem Gebiet *Multi-Core-Systems-on-Chip* entwickelt die Fachhochschule Dortmund derzeit einen ASIC-Baustein, mit dem eine NoC-Anbindung von Peripherieschnittstellen demonstriert werden soll (NoC-to-IO-Bridging). Gefertigt wird dieser Chip im Rahmen eines sog. *mini@sic* mit einem 65nm-Prozess von *UMC*. Die Fertigung wird durch das *Europractice Stimulation Program: First IC design Advanced Technology (90nm ... 55nm) – Fabrication* unterstützt.

Ein professionelles Testsystem steht aus Personalund Kostengründen nicht zur Verfügung. Die dann nahe liegende Lösung zum Testen besteht in der Adaptierung des ASIC-Bausteins an ein FPGA-Board, wobei dann FPGA-basierte Stimuli-Generatoren und Auswerteschaltungen ASIC-spezifisch realisiert werden können. Diese Verfahrensweise wird grundsätzlich übernommen. Im Ausbildungsumfeld sind jedoch üblicherweise FPGA-Boards vorhanden, die häufig nur über eine relativ geringe Anzahl an I/Os verfügen. Auf die eigene Entwicklung eines FPGA-Boards sollte wegen der zu erwartenden Komplexität jedoch auch verzichtet werden. Somit wurde im industriellen Bereich nach einer FPGA-Lösung gesucht. Die Wahl fiel letztendlich auf ein Zynq-Modul aus dem sog. SoM-System der Firma Trenz Electronic (SoM: System-on-Module). Mit diesem stehen ausreichend Schnittstellen für den Anschluss kleiner bis mittelgroßer ASICs zur Verfügung.

Wenn für einen neuen Chip das zugehörige Testsystem auch neu und somit unerprobt ist, stellt sich die Frage, wie man in Ermangelung eins *Known Good Die* den Tester testen soll. Zur Lösung dieses Problems wird für das neue Testsystem die Möglichkeit geschaffen, den ASIC mitsamt seiner Testumgebung zu emulieren. Dazu wurde das Testsystem elektromechanisch so ausgelegt, dass es sowohl die Adaptierung an einen Test-Sockel als auch alternativ an ein Emulations-Board ermöglicht. Auch das Emulations-Board basiert auf einem SoM-Modul.

Das Testsystem kann mit einem weiteren SoM-Modul bestückt werden, wenn die Anzahl von 134 I/Os für den zu testenden ASIC nicht ausreicht. Dieses Ergänzungsmodul ist dann dem Zynq-Modul untergeordnet (Master-Slave-Prinzip) und wird über eine schnelle, synchrone Datenschnittstelle mit letzterem verbunden.

Da es sich bei dem oben genannten ASIC um einen Digitalbaustein handelt, wird das Testsystem zunächst nur als Digitaltester und -emulator realisiert. Für den zukünftigen Einsatz als Mixed-Signal-Testumgebung ist vorgesehen, für das Ergänzungsmodul eine entsprechende eigene Hardware zu entwickeln.

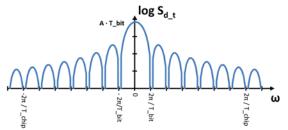

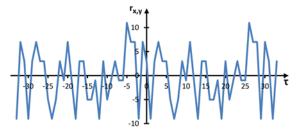

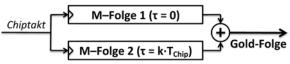

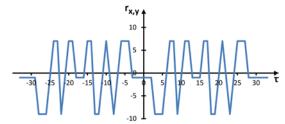

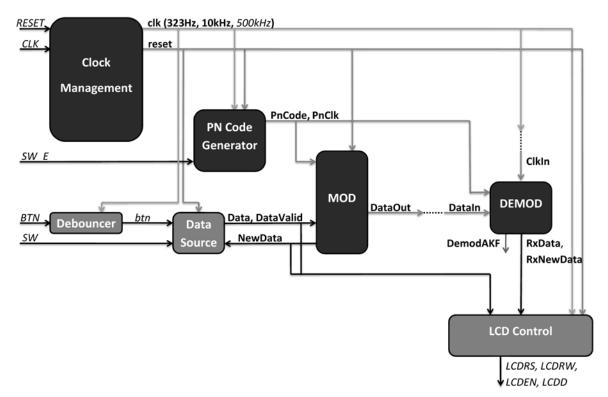

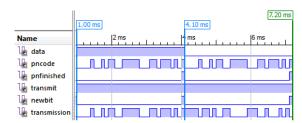

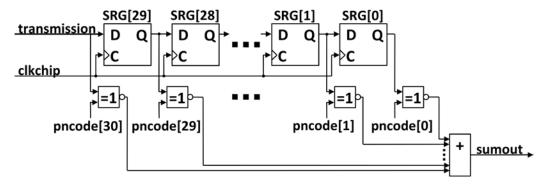

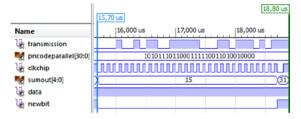

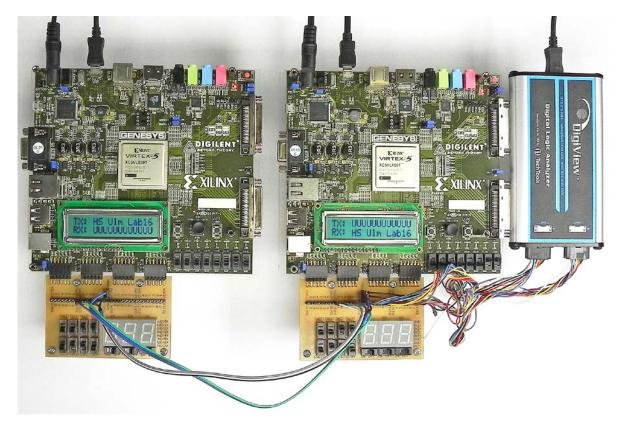

University of Applied Sciences and Arts