Herausgeber: MPC-Gruppe Ausgabe: 67/68 ISSN: 1868-9221 Publiziert: Juni 2025

Workshop: Karlsruhe Januar 2024 Workshop: Düsseldorf Januar 2025

Band 67 Workshop: Karlsruhe Januar 2024

1 Analoges MPP-Tracking mit Spitzenwertdetektion Patrick Mader, Sascha Eckerter, Rainer Merz, Hochschule Karlsruhe

- 9 Materialcharakterisierung basierend auf einem 120 GHz FMCW-Radar Marius Patzer, Nicolas Treier, Marlene Harter, Serdal Ayhan, Herman Jalli Ng, Hochschule Karlsruhe

- Realisierung von elektronischen und sensorischen Komponenten mittels FDM-3D-Druck-Verfahren Jannik Söll, Patrick Hog, Elke Mackensen, Hochschule für Technik, Wirtschaft und Medien Offenburg

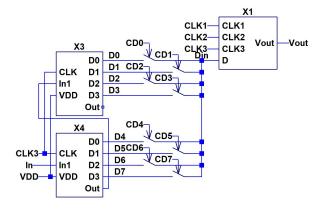

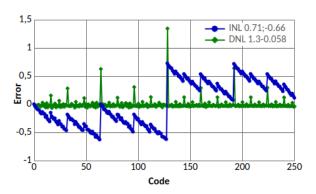

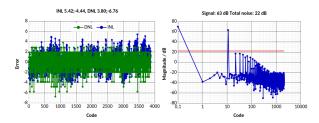

- 23 Low Cost Serial DAC Simulation, Realization, Error Correction and Characterization Jörg Vollrath, Hochschule Kempten

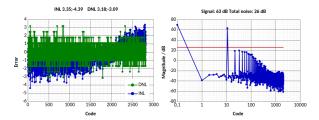

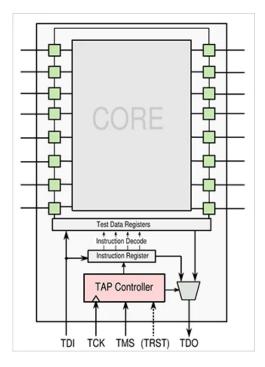

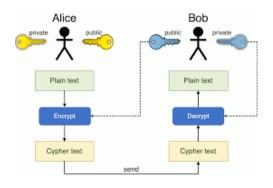

- 31 Improving Hardware Security through Encryption of JTAG TAP Ports: An Analytical Comparison of Algorithms, with a Focus on RSA

Soham Sanjay Dekhane, Andreas Siggelkow, Hochschule Ravensburg-Weingarten

Band 68 Workshop: Düsseldorf Januar 2025

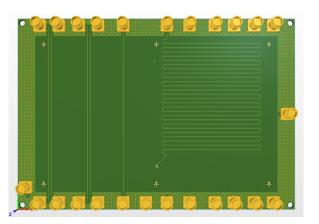

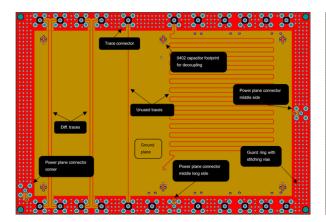

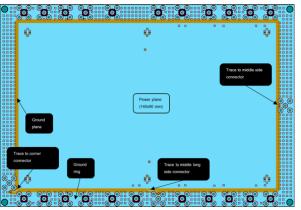

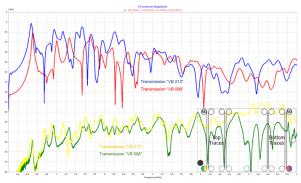

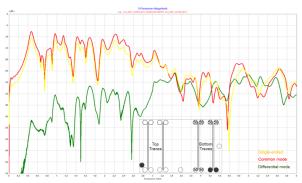

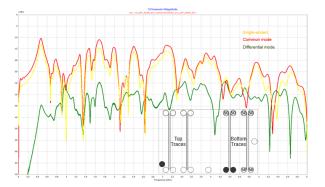

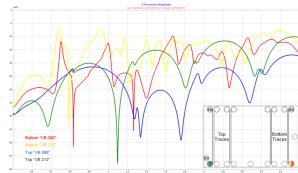

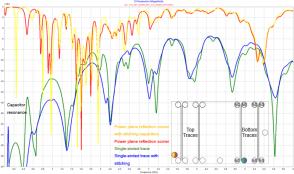

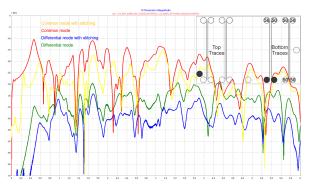

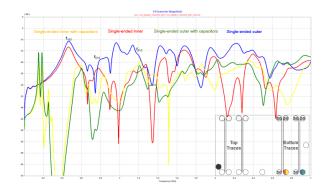

- 37 Coupling between traces and power planes in PCBs. How is it influenced and what are its consequences?

Justus Gottwald, Michael Engelbrecht, Bernhard M. Rieß, Hochschule Düsseldorf

- **47 Evaluation of a new AI driven SoC Design Flow Approach**Thierry Kersten, Thomas Haase, Bernhard M. Rieß, Hochschule Düsseldorf

- 59 Eine Debug- und Testumgebung für AXI-Stream basierte Ethernet-Frame-Verarbeitung in FPGAs Sebastian Haberkern, Marcus Würr, Stefan Eiermann, Hochschule Esslingen

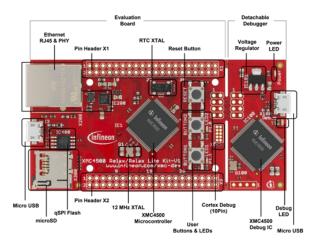

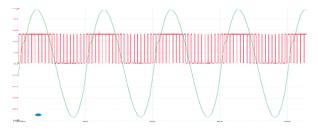

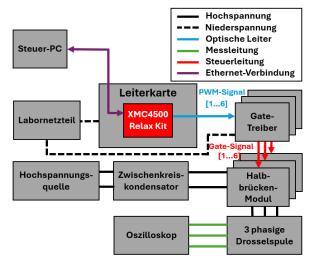

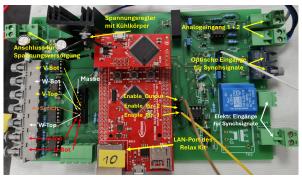

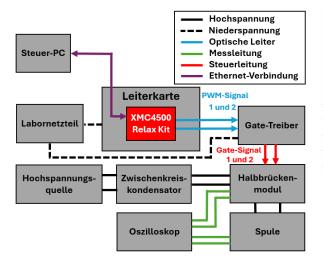

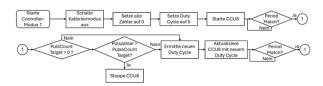

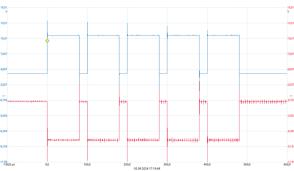

- **Entwicklung und Implementierung eines multifunktionalen PWM Modulators**Maik Greschuck, Clemens Elskamp, Bernhard M. Rieß, Hochschule Düsseldorf

## Inhaltsverzeichnis

Band 67 Workshop: Karlsruhe Januar 2024

| Analoges MPP-Tracking mit Spitzenwertdetektion                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Materialcharakterisierung basierend auf einem 120 GHz FMCW-Radar                                                                                                                                  |

| Realisierung von elektronischen und sensorischen Komponenten mittels FDM-3D-Druck 15 Verfahren  Jannik Söll, Patrick Hog, Elke Mackensen, Hochschule für Technik, Wirtschaft und Medien Offenburg |

| Low Cost Serial DAC Simulation, Realization, Error Correction and Characterization                                                                                                                |

| Improving Hardware Security through Encryption of JTAG TAP Ports: An Analytical                                                                                                                   |

| Band 68 Workshop: Düsseldorf Januar 2025                                                                                                                                                          |

|                                                                                                                                                                                                   |

| Coupling between traces and power planes in PCBs. How is it influenced and what are its 37 consequences?  Justus Gottwald, Michael Engelbrecht, Bernhard M. Rieß, Hochschule Düsseldorf           |

| Coupling between traces and power planes in PCBs. How is it influenced and what are its 37 consequences?                                                                                          |

| Coupling between traces and power planes in PCBs. How is it influenced and what are its                                                                                                           |

Tagungsband zum Workshop der Multiprojekt-Chip-Gruppe Baden-Württemberg Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie.

Die Inhalte der einzelnen Beiträge dieses Tagungsbandes liegen in der Verantwortung der jeweiligen Autoren.

#### Herausgeber:

Lothar Schmidt, MPC-Gruppe, Albert-Einstein-Allee 53, D-89081 Ulm

#### Mitherausgeber (Peer Reviewer):

Joachim Gerlach, Hochschule Albstadt-Sigmaringen, Gartenstraße 15, D-72458 Albstadt

Jürgen Giehl, Hochschule Mannheim, Paul-Wittsack-Straße 10, D-68163 Mannheim

Eckhard Hennig, Hochschule Reutlingen, Alteburgstraße 150, 72762 Reutlingen

Bernhard Jungk, Hochschule Albstadt-Sigmaringen, Gartenstraße 15, D-72458 Albstadt

Elke Mackensen, Hochschule Offenburg, Badstraße 24, D-77652 Offenburg

Andreas Siggelkow, Hochschule Ravensburg-Weingarten, Doggenriedstraße, 88250 Weingarten

Alle Rechte vorbehalten

Diesen Workshopband und alle bisherigen Bände finden Sie im Internet unter: http://www.mpc-gruppe.de/de/workshopbaende.html

# Analoges MPP-Tracking mit Spitzenwertdetektion

Patrick Mader, Sascha Eckerter, Rainer Merz

Zusammenfassung-Moduloptimierer erhöhen Photovoltaik-(PV-)Anlagen Leistungsentnahme von bei Verschattungen, indem sie jedes Modul im Punkt maximaler Leistung (MPP) betreiben, unabhängig von der jeweiligen Einstrahlung. Dafür muss jedes PV-Modul mit einem Moduloptimierer sein, was die Anschaffungskosten der Anlage erhöht. Deshalb ist eine besonders kostengünstige Realisierung von Moduloptimierern wichtig. Dies lässt sich durch Erhöhen der Taktfrequenz der Leistungselektronik und damit einem Verkleinern der passiven Bauelemente erreichen. Da das MPP-Tracking aber in der Regel auf einem Mikrocontroller erfolgt, führt das zu steigenden Kosten für einen schnellen Mikrocontroller. Deshalb stellt dieses Paper einen analogen MPP-Tracker vor, der ein kostengünstiges Erhöhen der Taktfrequenz ermöglicht und gleichzeitig durch Integration von eigener Spannungsversorgung und Treiberschaltung weitere Kosten reduziert. Der MPP-Tracker basiert auf einer Spitzenwertdetektion und wurde in einer analogen anwendungsspezifischen integrierten Schaltung (ASIC) integriert. Messung des ASICs an einer Leistungselektronik zeigen die Funktionsfähigkeit im erforderlichen Arbeitsbereich.

Schlüsselwörter—MPP-Tracking, Analoges MPP-Tracking, Moduloptimierer, ASIC, Photovoltaik, Peak-Detector, Watchdog-Timer, Perturb-And-Observe

#### I. EINLEITUNG

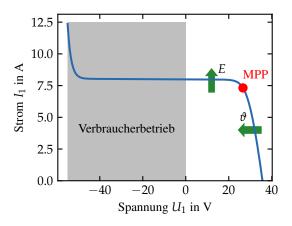

Eine PV-Anlage besteht typischerweise aus mehreren in Serie geschalteten PV-Modulen, die einen Strang bilden. Dadurch ist der Strom I durch jedes Modul gleich und die Modulspannungen addieren sich zur Gesamtspannung. Antiparallel zu jedem Modul befinden sich Bypass-Dioden, diese schützen die Module vor thermischer Überlastung. Denn wie in Abbildung 1 zu sehen, ist der Strom I1 eines PV-Moduls abhängig von der Einstrahlung E und die Spannung  $U_1$ abhängig von der Temperatur  $\vartheta$ . Dadurch ist auch der MPP abhängig von Einstrahlung E und Temperatur  $\vartheta$ . Kommt es z.B. aufgrund einer Verschattung an einem Modul zu einer kleineren Einstrahlung E, dann sinkt der lieferbare Strom des Moduls ab. Liegt nun der Strangstrom, der sich durch die anderen Module ergibt über dem Kurzschlussstrom des verschatteten Moduls, dann verschiebt sich der Arbeitspunkt in den Verbraucherbetrieb des PV-Moduls. Dadurch nimmt das Modul Leistung auf und die Spannung über dem Modul  $U_1$

Patrick Mader, patrick.mader@h-ka.de, Sascha Eckerter, sascha.eckerter@h-ka.de, Rainer Merz, rainer.merz@h-ka.de, Hochschule Karlsruhe – University of Applied Sciences (HKA), Moltkestraße 30, 76133 Karlsruhe.

Abbildung 1. Strom-Spannungskennlinie eines PV-Moduls. Im MPP gibt das Modul die maximal mögliche Leistung ab. Eine steigende Temperatur  $\vartheta$  verschiebt die Kennlinie zu kleineren Spannungen und eine steigende Einstrahlung verschiebt die Kennlinie zu höheren Strömen

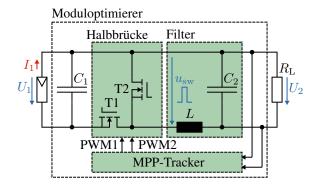

wird negativ. Durch die negative Spannung leitet die Bypassdiode und begrenzt die Verlustleistung des Moduls. Die Bypassdiode verhindert so eine thermische Zerstörung des Moduls. Allerdings liefert das verschattete Modul dann keine Leistung mehr, obwohl auch bei reduzierter Einstrahlung noch Leistung entnehmbar wäre. Eine Abhilfe schaffen hierbei sogenannte Moduloptimierer. Ein typischer Moduloptimierer, wie z.B. in [1] oder [8] vorgestellt, ist in Abbildung 2 zusehen und besteht aus einem Gleichspannungswandler und einem MPP-Tracker. Am Eingang des Moduloptimierers befindet sich das PV-Modul mit der Spannung  $U_1$ und am Ausgang wird der restliche PV-Strang durch einen ohmschen Widerstand  $R_{\rm L}$  mit der Spannung  $U_2$ modelliert. Der vorgestellte Moduloptimierer verwendet als Gleichspannungswandler einen Tiefsetzsteller, der aus einer Halbbrücke mit zwei Transistoren T1, T2 und einem Ausgangsfilter  $L, C_2$  besteht. Die Transistoren werden über komplementäre pulsweitenmodulierte Signale (PWM-Signale) angesteuert. Dabei ist eine wichtige Kenngröße für die PWM-Signale der Tastgrad

$$d := \frac{T_{\text{T1,ein}}}{T} = \frac{T_{\text{T2,aus}}}{T} , \qquad (1)$$

der das Verhältnis von Einschaltdauer  $T_{\rm T1,ein}$  von T1 bzw. Ausschaltdauer  $T_{\rm T2,aus}$  von T2 bezogen auf die Periodenlänge T der PWM-Signale angibt. Die mit den PWM-Signalen angesteuerte Halbbrücke liefert

1

Abbildung 2. Typischer Aufbau eines Moduloptimierers. Halbbrücke T1/T2 und Filter  $L/C_2$  bilden einen Tiefsetzsteller. Durch Ansteuern des Tiefsetzstellers durch den MPP-Tracker arbeitet das PV-Modul mit der Spannung  $U_1$  und dem Strom  $I_1$  im MPP. Als Eingangsgröße verwendet der MPP-Tracker die Ausgangsspannung  $U_2$ . Der Lastwiderstand  $R_{\rm L}$  modelliert den restlichen Modulstrang.

dadurch am Ausgang eine Rechteckspannung  $u_{\rm sw}$  mit dem Gleichanteil [9]

$$U_{\text{sw}} = \frac{1}{T} \int_0^T u_{\text{sw}} dt = d \cdot U_1 \tag{2}$$

und harmonische Oberschwingungen. Die Oberschwingungen werden durch den nachfolgenden Filter gedämpft und es ergibt sich der Zusammenhang

$$\frac{U_2}{U_1} = d (3)$$

des Verhältnisses von Ausgangsspannung  $U_2$  zu Eingangsspannung  $U_1$  und Tastgrad d. Diesen Zusammenhang nutzt der MPP-Tracker, um das angeschlossene PV-Modul im MPP zu betreiben, indem er durch Variieren des Tastgrades und Messen der Ausgangsleistung diesen MPP findet. Dabei verwendet der hier vorgestellte MPP-Tracker lediglich eine Spannungsmessung, um den MPP zu finden, da am ohmschen Widerstand der Zusammenhang

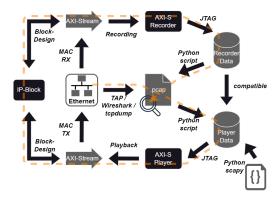

$$U_2 = \sqrt{P \cdot R_{\rm L}} \tag{4}$$

gilt und demnach die Spannung proportional zur Leistung ist.

Da jedes Modul in einem PV-Strang mit einem Moduloptimierer ausgestattet wird, muss auf einen möglichst robusten und kostengünstigen Entwurf der Elektronik geachtet werden. Die meisten Kosten der Elektronik verursachen die passiven Bauelemente L,  $C_1$  und  $C_2$  aus Abbildung 2. Wie die Schaltung angesteuert werden muss, um möglichst niedrige Induktivitätsund Kapazitätswerte verwenden zu können, wird klar, wenn die entsprechenden Dimensionierungsformeln herangezogen werden. Für die Eingangskapazität ergibt sich nach [5] der Zusammenhang

$$C_1 \propto \frac{1}{f} \,,$$

(5)

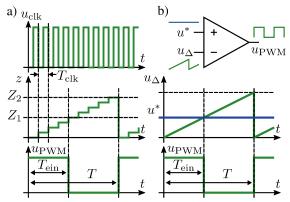

Abbildung 3. a) PWM-Erzeugung mit einem Mikrocontroller. Jeder Takt  $u_{\mathrm{clk}}$  erhöht den Zähler z. Erreicht z das erste Vergleichsregister  $Z_1$  schaltet  $u_{\mathrm{PWM}}$  auf LOW und nach Erreichen von  $Z_2$  ist die PWM-Periode beendet. b) Analoge PWM-Erzeugung mit Komparator durch Vergleich des Sollwerts  $u^*$  mit einem Trägersignal  $u_{\Delta}$ .  $u^*$  bestimmt d und die Frequenz von  $u_{\Delta}$  die PWM-Frequenz.

für die Ausgangskapazität liefert [2] den Zusammenhang

$$C_2 \propto \frac{1}{f}$$

(6)

und für die Induktivität resultiert nach [2] der gleiche Zusammenhang

$$L \propto \frac{1}{f}$$

(7)

Damit lässt sich feststellen, dass das Erhöhen der PWM-Frequenz kleinere Werte für die passiven Bauteile des Tiefsetzstellers erlaubt. Jedoch führt das Erhöhen der PWM-Frequenz f = 1/T bei einem Mikrocontroller gleichzeitig zu einer Verschlechterung der PWM-Auflösung  $d_{\min}$  bei gleichbleibender Frequenz  $f_{\mathrm{clk}}$  des Taktes  $u_{clk}$ , wie auch an Abbildung 3.a) zu erkennen ist. Denn um mit einem heutzutage standardmäßig verwendeten Mikrocontroller eine PWM zu erzeugen, wird ein Zähler  $z \in \mathbb{N}$  verwendet, der nach jeder Periode  $T_{\rm clk}$  des Taktes  $u_{\rm clk}$  hochgezählt wird. Erreicht z das erste Vergleichsregister  $Z_1 \in \mathbb{N}$ , dann wird die PWM-Spannung  $u_{PWM}$  auf LOW geschaltet, somit bestimmt  $Z_1$  die Einschaltzeit  $T_{\rm ein}$  der PWM. Nach dem Erreichen des zweiten Vergleichsregisters  $Z_2$  =  $\{Z_2 \in \mathbb{N} | Z_2 \geqslant Z_1\}$  ist eine PWM-Periode beendet und z beginnt von vorne. Das Vergleichsregister  $Z_2$ bestimmt somit die Periodendauer

$$T = (Z_2 + 1) \cdot T_{\text{clk}} \tag{8}$$

und neben  $Z_1$  auch den Tastgrad  $d=Z_1/(Z_2+1)$ . Weiter lässt sich die Auflösung, also die kleinste mögliche Änderung des Tastgrades mit

$$\Delta d_{\min} = \frac{\partial d}{\partial Z_1} = \frac{1}{Z_2 + 1} \tag{9}$$

berechnen. Für ein effizientes MPP-Tracking mit hoher Taktfrequenz stehen die Gleichungen 8 und 9

allerdings im Widerspruch, da ein Vergrößern von  $Z_2$  zwar die Auflösung verbessert, aber gleichzeitig die Taktfrequenz verkleinert und umgekehrt. Die naheliegende Möglichkeit die Taktfrequenz zu erhöhen, ist das Verwenden eines Mikrocontrollers mit hoher Clock-Frequenz, was allerdings zu einem teuren Mikrocontroller führt. Eine andere Möglichkeit ist die Verwendung eines analogen PWM-Generators, wie in Abbildung 3.b) zusehen. Analoge PWM-Generatoren arbeiten mit einem Komparator, an dem der Sollwert des Tastgrads  $u^*$  mit einem dreieckförmigen Trägersignal  $u_{\Delta}$  verglichen wird. Damit ist die Auflösung

$$\Delta d_{\min} = \lim_{Z_2 \to \infty} \frac{1}{Z_2} = 0 , \qquad (10)$$

bei unendlich vielen Stufen  $Z_2$  und damit theoretisch unendlich groß. Die PWM-Frequenz f kann dadurch kostengünstig mit der Frequenz des Dreieckgenerators erhöht werden. Deshalb beschäftigt sich diese Arbeit mit der Entwicklung eines MPP-Tracking-Verfahrens für einen analogen ASIC. Die Verwendung eines ASICs führt zu zusätzlichen Kosteneinsparungen, da überflüssige Funktionen eines Mikrocontrollers entfallen und benötigte Funktionen, wie Spannungsversorgung und Gate-Treiber auch integriert werden können. Dadurch sinkt auch die Anzahl an externen Bauteilen und somit wird der MPP-Tracker durch die geringere Anzahl an Lötstellen robuster.

Zur Vorstellung des entwickelten ASICs beginnt diese Arbeit zunächst in Abschnitt II mit der Erläuterung des MPP-Tracking-Verfahrens anhand eines Blockschaltbilds. Anschließend werden die wichtigsten Teilschaltungen anhand von Schaltplänen gezeigt. Der Abschnitt III stellt den gefertigten ASIC und die Testschaltung vor und zeigt anschließend die Messergebnisse. Abschließend fasst Abschnitt IV die Arbeit zusammen.

#### II. ANALOGES MPP-TRACKING

Für die Auswahl des Verfahrens zum MPP-Tracking kommen verschiedene Algorithmen infrage, die in der Literatur [6] auch schon in digitale und analoge Implementation klassifiziert sind. Aufgrund der niedrigen Komplexität und der relativ hohen Effizienz wird der Perturb-And-Observe Algorithmus als Grundlage verwendet. Beim Perturb-And-Observe Verfahren wird der Tastgrad solange in die gleiche Richtung Schrittweise verändert, also entweder stetig vergrößert oder stetig verkleinert, bis die im aktuellen Schritt k gemessene Leistung P[k] kleiner als die Leistung P[k-1] aus dem vorherigen Schritt k-1 ist. Erst dann wird die Richtung umgeschaltet und der Tastgrad wieder solange in diese Richtung verändert, bis P[k] < P[k-1] ist und so weiter. Ist der MPP gefunden, dann pendelt der Tastgrad um den Tastgrad im MPP. Beim klassischen Perturb-And-Observe Algorithmus muss demnach immer die Leistung aus dem vorherigen Schritt, z.B. mit

einem Abtasthalteglied gespeichert werden, um dies zu umgehen wird das vorgestellte Verfahren um einen Spitzenwertdetektor erweitert. Der Spitzenwertdetektor erkennt, wenn die aktuelle Leistung P(t) kleiner ist als der Maximalwert

$$P_{\max} = \max_{t \in T_{r,k}} (P(t)) \tag{11}$$

im Zeitabschnitt  $T_{r,k}:=[t_{k-1},t_k)$  mit der aktuellen Richtung und schaltet dann die Richtung um. Die Umsetzung des MPP-Trackings mit Spitzenwertdetektion wird im Folgenden vorgestellt.

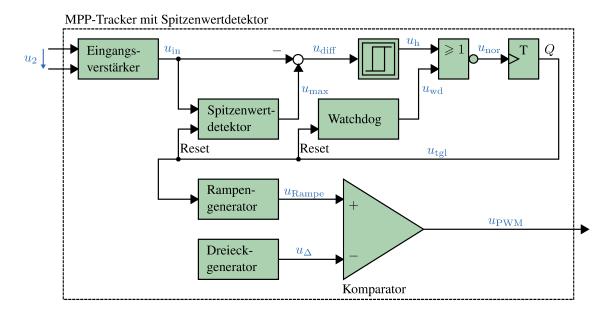

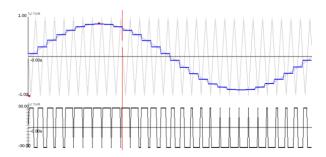

#### A. MPP-Tracking mit Spitzenwertdetektion

Das Blockschaltbild des MPP-Trackers ist in Abbildung 4 zusehen. Das PWM-Signal  $u_{PWM}$  mit steigendem oder fallenden Tastgrad d wird am Komparator durch Vergleich des Dreiecksignal  $u_{\Delta}$  mit dem Signal aus dem Rampengenerator  $u_{\rm Rampe}$  erzeugt. Die Eingangsgröße des Rampengenerators  $u_{\mathrm{tgl}}$  speichert dabei die Information, ob der Tastgrad gerade vergrößert oder verkleinert wird. Die Eingangsgröße des MPP-Trackers ist die Ausgangsspannung des Tiefsetzstellers  $u_2$  aus Abbildung 2, da diese Proportional zur Leistung *P* ist. Diese wird zunächst mit dem Eingangsverstärker auf den internen Spannungspegel  $u_{\rm in}$  des ASICs gewandelt. Anschließend liegt  $u_{\mathrm{in}}$  am Spitzenwertdetektor an. Dieser gibt an seinem Ausgang den im aktuellen Zeitabschnitt  $T_{r,k} := [t_{k-1}, t_k)$  gespeicherten Maximalwert

$$u_{\max} = \max_{t \in T_{r,k}} \left( u_{\text{in}} \right) \tag{12}$$

von  $u_{in}$  aus. Der Zeitabschnitt  $T_{r,k}$  wird von einem Reset-Signal beendet. Die beiden Spannungen  $u_{\rm in}$  und  $u_{\mathrm{max}}$  dienen zum Detektieren des MPP. Denn wenn  $|u_{\mathrm{max}}| \leqslant |u_{\mathrm{in}}|$  gilt, dann steigt  $u_{\mathrm{in}}$  noch und damit auch die Leistung P und der MPP ist noch nicht überschritten. Gilt jedoch  $|u_{\text{max}}| \geqslant |u_{\text{in}}|$ , dann fällt  $u_{\rm in}$  und damit ist der MPP überschritten. Das wird durch die nachfolgende Differenzstelle mit Hysterese-Schaltung ausgewertet und führt zum Umschalten des Toggle-Flip-Flops. Das Toggle-Flip-Flop speichert mit seiner Ausgangsgröße  $u_{\rm tgl}$  die Information in welche Richtung der Tastgrad des PWM-Signals geändert wird. Gleichzeitig setzt jede Flanke an  $u_{\rm tgl}$  den Spitzenwertdetektor und den Watchdog-Timer zurück. Dadurch kann der Spitzenwertdetektor wieder den neuen Maximalwert  $u_{\text{max}}$  von  $u_{\text{in}}$  des neuen Zeitabschnitts  $T_{\mathrm{r},k+1}$  speichern. Für den Fall, indem der MPP-Tracker in einem ungünstigen Betriebspunkt feststeckt und den MPP nicht findet, löst der Wachdog-Timer aus, da es zu keinem Reset durch  $u_{\mathrm{tgl}}$  kommt. Ein ungünstiger Betriebspunkt kann entstehen, wenn das Rampensignal  $u_{\rm Rampe}$  an der positiven oder negativen Spannungsgrenze ist und durch  $u_{\mathrm{tgl}}$  weiter steigen oder fallen

3

Abbildung 4. Blockschaltbild des analogen MPP-Trackers mit Spitzenwertdetektor. Der Eingangsverstärker wandelt die Eingangsspannung  $u_2$  auf den Spannungspegel  $u_{\rm in}$  des ASICs. Der Vergleich von Spitzenwert  $u_{\rm max}$  und aktuellen Wert  $u_{\rm in}$  liefert die Information, wann der MPP überschritten ist und schaltet über das Toggle-Flip-Flop die Suchrichtung  $u_{\rm tgl}$  um. Dieses Umschalten führt zum Zurücksetzen des Spitzenwertdetektors und des Watchdog-Timers. Der Watchdog-Timer dreht die Richtung, wenn es zu keiner Detektion eines MPPs innerhalb der Watchdog-Zeit kommt.  $u_{\rm tgl}$  erzeugt am Komparator zusammen mit  $u_{\rm Delta}$  ein PWM-Signal  $u_{\rm PWM}$  mit steigendem oder fallendem Tastgrad.

soll. Dann bleibt der Tastgrad konstant und die MPP-Erkennung kann keinen MPP finden. Der Watchdog-Timer schaltet dann wie die MPP-Erkennung die Richtung des Tastgrads um. Der nachfolgende Abschnitt stellt die wichtigsten Teilschaltungen des Blockschaltbilds vor.

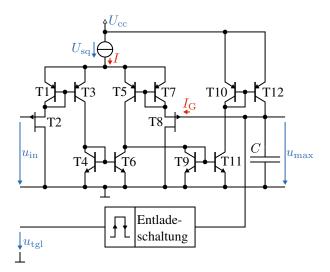

1) Spitzenwertdetektor: Die Aufgabe des Spitzenwertdetektors ist es an seinem Ausgang  $u_{\rm max}$  den aktuellen Maximalwert von  $u_{\rm in}$  zu speichern bis ein Rücksetzbefehl an  $u_{\mathrm{tgl}}$  kommt. Das Grundprinzip basiert dabei auf der Operationsverstärkerschaltung mit Diode am Ausgang und Kondensator mit Rückkopplung auf die Eingänge des Operationsverstärkers, wie sie in [10] vorgestellt ist. Allerdings zeigt sich bei dieser Schaltung, dass ein leichtes Überschwingen der Kondensatorspannung sofort zu einer zu hohen Maximalspannung  $u_{\rm max}$  führt, die wiederum aufgrund der Diode nicht mehr abgebaut werden kann. Deshalb wurde im Zuge der Arbeit ein neuer Spitzenwertdetektor mit einstellbarer Reglerverstärkung entwickelt, dieser ist in Abbildung 5 dargestellt. Der entwickelte Spitzenwertdetektor besteht am Eingang aus einem Differenzverstärker mit Sperrschicht-Feldeffekttransistoren (JFETs), da diese keine Gate-Ströme  $I_{\rm G}=0$  besitzen und somit den Kondensator C nicht über diese laden/entladen. Die Stromspiegelkonfiguration bestehend aus T1, T3 und T5, T7 ermöglicht einen niedrigeren Eingangsspannungsbereich von

$$u_{\rm in} \in [0, U_{\rm cc} - U_{\rm BE} - U_{\rm sq}]$$

(13)

Abbildung 5. Spitzenwertdetektor mit Entladeschaltung. Die Schaltung besteht aus einem Differenzverstärker mit den Transistoren T1 bis T8 und einer Stromspiegelstufe T9 bis T12, die nur einen positiven Strom liefern kann. Dadurch liefert die Schaltung am Ausgang  $u_{\rm max}$  den Maximalwert von  $u_{\rm in}$  bis eine Flanke an  $u_{\rm tgl}$  über die Entladeschaltung den Kondensator C entlädt.

unter der Annahme, dass über der Stromquelle I mindestens  $U_{\rm sq}\approx 1\,{\rm V}$  abfallen muss. Am Ausgang des Differenzverstärkers befinden sich ein NPN- und ein PNP-Stromspiegel, der aus den Transistorpaaren T9, T11 und T10, T12 besteht. Durch die Verwendung von unterschiedlichen Emitterflächen  $n_{{\rm T},i},i\in$

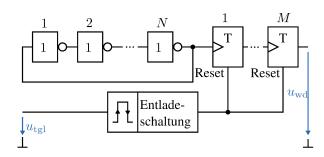

Abbildung 6. Watchdog-Timer mit Entladeschaltung. Der Ringoszillator bestehend aus Invertern 1 bis N generiert den Takt. Toggle-Flip-Flops 1 bis M arbeiten als Frequenzteiler und passen so den Takt auf die erforderliche Watchdog-Zeit  $T_{\rm wd}$  an. Nachdem die Watchdog-Zeit erreicht ist, schaltet Ausgang  $u_{\rm wd}$  von LOW auf HIGH. Die Flanke an  $u_{\rm tgl}$  setzt über die Entladeschaltung den Watchdog-Timer zurück.

$\{9, 10, 11, 12\}$  lässt sich damit die Verstärkung der Stromspiegel [3] mit

$$k = \frac{n_{\rm T11}}{n_{\rm T9}} \frac{n_{\rm T12}}{n_{\rm T10}} \tag{14}$$

einstellen und so lässt sich ein Überschwingen der Kondensatorspannung verhindern. Über die flankensensitive Entladeschaltung wird der Kondensator C entladen, sobald eine fallende oder steigende Flanke an  $u_{\rm tgl}$  entsteht.

2) Watchdog-Timer: Der Watchdog-Timer erkennt, wenn für eine eingestellte Zeit  $T_{\rm wd}$  kein MPP detektiert wird und schaltet dann seinen Ausgang  $u_{\rm wd}$  von LOW auf HIGH. Der Aufbau der Schaltung ist in Abbildung 6 zusehen. Der Takt des Watchdog-Timers entsteht durch einen Ringoszillator [7], der mit den Invertern 1 bis N aufgebaut ist. Durch eine ungerade Anzahl  $N=2n+1, n\in\mathbb{N}$  an Invertern ergibt sich durch die Kette eine Phasenverschiebung des Signals von  $180^{\circ}$ , was zu einer Oszillation führt. Die Frequenz des Oszillators ergibt sich aus der Summe der Verzögerungen  $\tau$  der Inverter zu

$$f = \frac{1}{2N\tau} \ . \tag{15}$$

Der anschließende Frequenzteiler, bestehend aus den Toggle-Flip-Flops 1 bis M verringert die Taktfrequenz auf die benötigte Auslösezeit

$$T_{\rm wd} = N\tau M \ . \tag{16}$$

Über eine flankensensitive Entladeschaltung werden die Toggle-Flip-Flops 1 bis M zurückgesetzt, sobald eine Signaländerung an  $u_{\rm tgl}$  entsteht und der Watchdog beginnt von vorne.

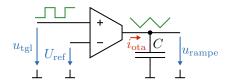

3) Rampengenerator: Der Rampengenerator erzeugt je nachdem ob der Eingang  $u_{\rm tgl}$  auf HIGH oder LOW ist eine steigende oder fallende Rampe und ist in Abbildung 7 dargestellt. Die Schaltung besteht aus einem Transkonduktanzverstärker (OTA), der ausschließlich im Großsignalbereich betrieben wird. Dafür ist die Ausgangsstufe des OTAs angepasst, um sehr

Abbildung 7. Rampengenerator bestehend aus OTA und Kondensator C. Je nachdem ob  $u_{\rm tgl}$  HIGH oder LOW ist, entsteht am Ausgang des OTAs positiver oder negativer Ausgangsstrom  $i_{\rm ota}$ , den der Kondensator zu rampenförmiger Spannung  $u_{\rm rampe}$  integriert.

Abbildung 8. Dreieckgenerator bestehend aus Stromquelle  $I_{\rm c}$ , die den Kondensator C lädt und einer Hystereseschaltung, bestehend aus U1 bis U3 und T1. Erreicht die Kondensatorspannung  $u_{\Delta}$  die obere Schaltschwelle  $U_{\rm ref\_o}$ , dann entlädt die Hystereseschaltung den Kondensator C bis zur unteren Schaltschwelle  $U_{\rm ref\_u}$ . Dadurch entsteht eine dreieckförmige/sägezahnförmige Ausgangsspannung  $u_{\Delta}$ .

kleine Ausgangsströme  $i_{\rm ota}$  erzeugen zu können. Die rampenförmige Ausgangsspannung  $u_{\rm rampe}$  ergibt sich aus der Spannungsdifferenz am Eingang  $u_{\rm tgl}-U_{\rm ref}$  und der OTA-Verstärkung  $g_{\rm ota}:=\partial i_{\rm ota}/\partial (u_{\rm tgl}-U_{\rm ref})$  zu

$$u_{\text{rampe}} = \frac{1}{C} \int g_{\text{ota}}(u_{\text{tgl}} - U_{\text{ref}}) dt + U_0 \qquad (17)$$

und ist je nachdem ob  $u_{\rm tgl}$  HIGH oder LOW ist positiv oder negativ.

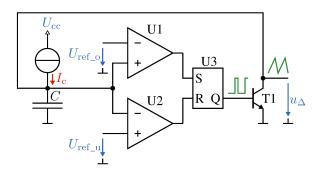

4) Dreieckgenerator: Der Dreieckgenerator liefert ein dreieck-/sägezahnförmiges Signal, das als Träger für die PWM dient. Die Ausführung des Dreieckgenerators ist in Abbildung 8 zusehen und an den RC-Kippschwinger aus [4] angelehnt.

Der Dreieckgenerator besteht aus einer Konstantstromquelle  $I_{\rm c}$  die den Kondensator C lädt und einer Hystereseschaltung mit einer oberen Schaltschwelle  $U_{\rm ref_{-}o}$  und einer unteren Schaltschwelle  $U_{\rm ref_{-}u}$ . Durch die Konstantstromquelle  $I_{\rm c}$  wird der Kondensator C geladen und die Spannung

$$u_{\Delta} = \frac{1}{C} \int_{t}^{t+T_{\Delta}} I_{c} dt + U_{ref_{u}}$$

(18)

steigt rampenförmig an, bis die obere Schaltschwelle  $U_{\mathrm{ref}\_o}$  erreicht ist. Das Erreichen der Schaltschwelle  $U_{\mathrm{ref}\_o}$  führt dazu, dass der Komparator U1 umschaltet und das SR-Flip-Flop U3 setzt. Dadurch schaltet der Transistor T1 und entlädt C in vernachlässigbarer Zeit bis die untere Schaltschwelle  $U_{\mathrm{ref}\_u}$  erreicht ist. Das Erreichen der unteren Schaltschwelle  $U_{\mathrm{ref}\_u}$  führt zum

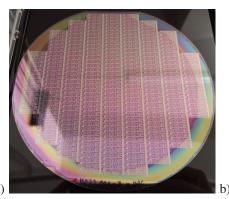

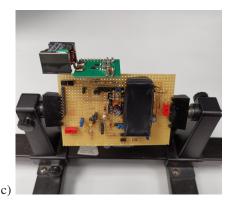

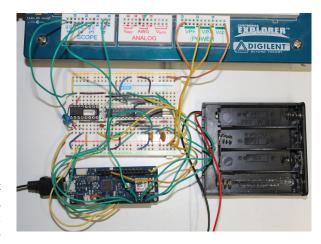

Abbildung 9. a) Produzierter Wafer der entwickelten Schaltung mit dem Smart-BCD Process von Prema Semiconductor. b) In Keramik-Gehäuse verpackter ASIC. c) Entwickelter Testaufbau, bestehend aus Lastpfadplatine mit Tiefsetzsteller und Regelungsplatine mit ASIC.

Umschalten von U2 und damit zum Zurücksetzten von U3, die Schaltung beginnt nun wieder von vorne. Die Frequenz des Dreieckgenerators

$$f_{\Delta} = \frac{I_{\rm c}}{C(U_{\rm ref o} - U_{\rm ref u})} \tag{19}$$

ergibt sich durch Einsetzen von  $u_{\Delta}=U_{\rm ref\_o}$  in Gleichung 18 und anschließendem Auflösen.

#### III. ERGEBNISSE UND DISKUSSION

Der nachfolgende Abschnitt zeigt den realisierten ASIC und stellt die Messergebnisse vor.

#### A. ASIC und Testschaltung

Die vorgestellte Schaltung wurde bei der Prema Semiconductor GmbH im Smart-BCD Process auf einem 6 Zoll Wafer hergestellt. Der Wafer ist in Abbildung 9.a) zusehen. Der Smart-BCD Process ermöglicht NPN- und PNP-Transistoren mit Kollektor-Strömen von bis zu 1 A und Spannungen bis zu 80 V [11]. Anschließend wurde der "Die" des ASICs in einem Dual-In-Line (DIL) Keramik-Gehäuse verpackt (Abbildung 9.b)). Um den ASIC in Betrieb zunehmen, wurde der Hardwareaufbau aus Abbildung 9.c) entwickelt. Der Aufbau besteht aus dem Lastpfad, der über eine Klemmleiste auf die Regelungsplatine aufgesteckt werden kann. Auf der Regelungsplatine befindet sich der entwickelte ASIC, der durch eine schwarze Box gegen eintreffende Photonen geschützt ist, die einen Fehlerstrom verursachen würden. Der Lastpfad besteht aus einem Tiefsetzsteller wie in Abbildung 2 vorgestellt.

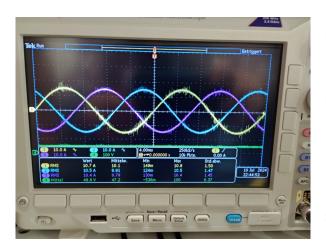

#### B. Messergebnisse

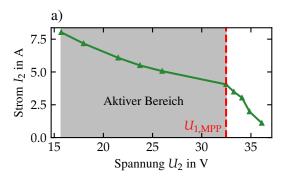

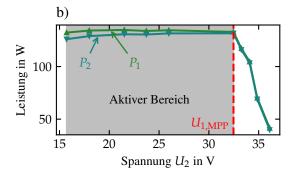

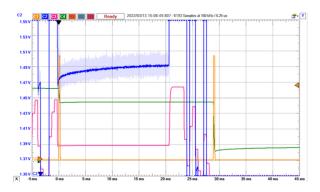

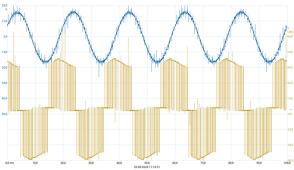

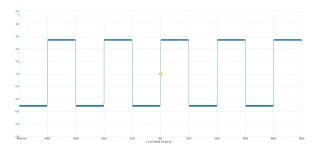

Zur Auswertung des entwickelten ASICs wurde an die Testschaltung ein PV-Modul an den Eingang des Tiefsetzstellers und an den Ausgang ein Lastwiderstand  $R_{\rm L}$  angeschlossen. Dabei wurde der Lastwiderstand variiert, um den Arbeitsbereich des ASICs aufzunehmen. Abbildung 10 stellt die Ergebnisse der

Abbildung 10. Messung der Testschaltung mit ASIC am PV-Modul und Variation des Lastwiderstands  $R_{\rm L}$ . a) Ausgangsstrom  $I_2$  über der Ausgangsspannung  $U_2$  des Tiefsetzstellers. b) Eingangsleistung  $P_1$  und Ausgangsleistung  $P_2$  über der Ausgangsspannung  $U_2$  des Tiefsetzstellers. Leistungen  $P_1$  entspricht im aktiven Bereich der MPP-Leistung.

Messung vor. Dabei zeigt Abbildung 10.a) den Strom-Spannungsverlauf am Ausgang des Tiefsetzstellers. Der aktive Bereich beginnt ab der MPP-Spannung des PV-Moduls, dann kann der Tiefsetzsteller die Spannung  $U_2$  nach dem Zusammenhang aus Gleichung 3 kleiner machen. Im aktiven Bereich ist dann die Eingangsleistung konstant und entspricht der MPP-Leistung, was auch in Abbildung 10.b) zusehen ist. Die Leistung am Ausgang des Tiefsetzstellers  $P_2$  ist aufgrund von Verlusten der Leistungselektronik etwas

kleiner als  $P_1$ . Aufgrund der konstanten Leistung  $P_2$  und dem Zusammenhang am ohmschen Widerstand ergibt sich für den Strom im aktiven Bereich der hyperbolische Verlauf

$$I_2 = \frac{P_2}{U_2} \ . \tag{20}$$

Aus diesem Zusammenhang resultiert die untere Spannungsgrenze des aktiven Bereichs, da der Strom  $I_2$  umso größer wird, je kleiner die Spannung  $U_2$  ist und damit der maximale Strom der Induktivität und der Transistoren erreicht wird. Die Spannungsgrenze wird extern über den Strom  $I_2$  eingestellt. Die Messergebnisse zeigen also das gewünschte Verhalten des MPP-Trackers, das PV-Modul wird im aktiven Bereich im MPP gehalten.

#### IV. ZUSAMMENFASSUNG

Um Moduloptimierer möglichst kostengünstig durch das Erhöhen der Taktfrequenz zu realisieren wurde in diesem Paper ein analoger MPP-Tracker entwickelt, der zur Integration in einen ASIC geeignet ist. Das Verfahren des MPP-Trackers basiert auf dem Perturb-And-Observe Algorithmus, der jedoch um einen Spitzenwertdetektor erweitert wurde. Der Spitzenwertdetektor wurde für diese Arbeit neu entwickelt und basiert auf einem Differenzverstärker mit Stromspiegelausgangsstufe und Kondensator. Anschließend erzeugt ein Rampengenerator zusammen mit einem Dreieckgenerator an einem Komparator das PWM-Signal für die Transistoren. Weiter besitzt die Schaltung einen Watchdog-Timer, um ein Feststecken in einem ungünstigen Arbeitspunkt zu verhindern und sorgt so für einen robusten Betrieb. Die Funktion des ASIC wurde anhand einer Testhardware gezeigt. Dafür wurde der verpackte ASIC auf einer Regelungsplatine zum Ansteuern einer Leistungselektronik verwendet. Die Messergebnisse beweisen die Funktion des ASICs und zeigen, dass das angeschlossene PV-Modul im geforderten Arbeitsbereich der Schaltung im MPP gehalten wird.

#### DANKSAGUNG

Die Autoren bedanken sich bei der BRC Solar GmbH und der Prema Semiconductor GmbH für die Förderung dieser Arbeit und ganz besonders bei Jonas Bargon, Richard Brace und Timm Czarnecki für die fachliche Unterstützung. Weiterhin gilt ein Dank dem Bundesministerium für Wirtschaft und Klima für die Finanzierung der Weiterentwicklung des analogen MPPT im Rahmen des Bundesprojekts Solarpark 2.0 mit der Nummer FKZ: 03EE1135C.

#### LITERATURVERZEICHNIS

- [1] Richard Brace, Angelika Neumann und Rainer Merz. "Kostengünstige Ertragssteigerung teilverschatteter PV-Stränge". In: *Photovoltaische Solarenergie Bad Staffelstein*. Bd. 33. Apr. 2018.

- [2] Robert W. Erickson und Dragan Maksimovic. Fundamentals of Power Electronics. 3. Auflage. Springer-Verlag, 2020. ISBN: 9783030438791.

- [3] Paul R. Gray, Paul J. Hurst, Stephen H. Lewis und Robert G. Meyer. *Analysis and Design of Analog Integrated Circuits*. 5. Edition. Wiley, 2010. ISBN: 978-0470398777.

- [4] A. Grebene. *Bipolar and MOS Analog Integrated Circuit Design*. 1. Auflage. John Wiley & Sons, Inc., 2002.

- [5] How to select input capacitors for a buck converter. Texas Instruments. 2016. URL: https://www.ti.com/lit/an/slyt670/slyt670.pdf?ts=1671014830265&ref\_url=https%253A%252F%252Fwww.google.com%252F.

- [6] H. El-Khozondar, Rifa El-Khozondar, Khaled Matter und Teuvo Suntio. "A review study of photovoltaic array maximum power tracking algorithms". In: *Renewables: Wind, Water, and Solar* 3 (Feb. 2016). DOI: 10.1186/s40807-016-0022-8.

- [7] Mrinal Mandal und Bishnu Charan Sarkar. "Ring oscillators: Characteristics and applications". In: *Indian Journal of Pure and Applied Physics* 48 (Feb. 2010), S. 136–145.

- [8] Angelika Neumann, T Czarnecki und R. Merz. ">99% Spitzenwirkungsgrad mit Low-Cost-MPPT statt Poweroptimizer". In: *Photovoltai-sche Solarenergie Bad Staffelstein*. Bd. 32. März 2017.

- [9] Dierk Schröder und Rainer Marquardt. Leistungselektronische Schaltungen. 4. Auflage. Springer Vieweg, 2019. ISBN: 978-3662553244.

- [10] Ulrich Tietze, Christoph Schenk und Eberhard Gamm. *Halbleiter-Schaltungstechnik*. 16. Auflage. Springer Vieweg, 2019. ISBN: 978-3662485538.

- [11] Triple Well Smart-BCD Process with only 11 Mask Layers A Process of Unsurpassed Simplicity and Modularity. PREMA Semiconductor. URL: https://www.prema.com/index.php/de/know-how/prema-prozess/item/download/47\_01894e25558788835b2d2467ef8f6390.

7

Patrick Mader erhielt den akademischen Grad B.Eng. in Elektrotechnik mit der Fachrichtung Energietechnik und Erneuerbare Energien von der Hochschule Karlsruhe im Jahr 2019. Anschließend erhielt er im Jahr 2023 den M.Sc. in Elektrotechnik mit der Fachrichtung elektrische Antriebe und Leistungselektronik vom Karlsruher Institut für Technologie. Derzeit arbeitet er an der Hochschule Karlsruhe im Bereich Leistungselektronik für Erneuerbare Energien an seiner Promotion.

Sascha Eckerter erhielt den akademischen Grad des Bachelor of Engineering in Mechatronik im Jahr 2020 von der Hochschule Karlsruhe (HKA). Dort erhielt er ebenfalls den akademischen Grad des Master of Science in Elektrotechnik im Jahr 2022 mit Spezialisierung im Bereich Erneuerbaren Energien und Energietechnik. Bis dato arbeitet er an der HKA im Bereich der Regenerativen Energien an seiner Promotion und entwickelt im Zuge seiner Dissertation

eine Simulationsumgebung für den Jahresertrag von Solarparks mit neuer Solartechnik.

Rainer Merz studierte Elektrotechnik, Fachrichtung Opto- und Mikroelektronik an der Universität Stuttgart. Im Anschluss wurde er am Institut für Photovoltaik der Universität Stuttgart promoviert. Von 2011 bis 2014 leitete Rainer Merz die Abteilung Insel und Speichersysteme beim Wechselrichterhersteller REFUsol. Im Herbst 2014 wurde er als Professor für Regenerative Energiesysteme an die Hochschule Karlsruhe berufen.

## Materialcharakterisierung basierend auf einem 120 GHz FMCW-Radar

Marius Patzer, Nicolas Treier, Marlene Harter, Serdal Ayhan, Herman Jalli Ng

Zusammenfassung—Dieses Paper präsentiert eine innovative Methode zur Materialcharakterisierung unter

Verwendung von Millimeterwellen. Ein selbstentwickelter 120 GHz Transceiver-Chip dient als FrequencyModulated-Continuous-Wave-(FMCW)Radarsensor, um

anhand der gemessenen Laufzeitunterschiede eine präzise

Unterscheidung verschiedener Materialien zu ermöglichen. Das ausgeklügelte Messkonzept verursacht deutlich

geringere Kosten als die Messung mit einem VektorNetzwerkanalysator (VNA). Durch die Anwendung eines

hochgenauen Signalverarbeitungsalgorithmus erfolgt eine

detaillierte Auswertung der aufgezeichneten Daten. Diese

innovative Methode eröffnet vielversprechende Perspektiven für weiterführende Forschungen und Entwicklungen.

Schlüsselwörter—Radar, Materialcharakterisierung, relative Permittivität, FMCW, Millimeterwellen

#### I. EINLEITUNG

In der modernen Materialwissenschaft und im Ingenieurwesen ist die präzise Charakterisierung von Materialien von entscheidender Bedeutung für die Entwicklung innovativer Produkte und Technologien. In den letzten Jahren wurden deshalb viele Forschungsarbeiten im Bereich der Materialcharakterisierung getätigt [1][2][3].

Mit dem Einsatz von Frequency-Modulated-Continuous-Wave-(FMCW)Radarsensoren lassen sich detaillierte Analysen verschiedenster Materialien durchführen. Insbesondere der Einsatz von Millimeterwellen ermöglicht es, Materialien mit hoher Auflösung und Empfindlichkeit zu durchdringen sowie eine ausgezeichnete Oberflächenauflösung zu bieten. Durch diese Technologien können Strukturen und Eigenschaften eines Materials charakterisiert werden, ohne die Integrität zu beeinträchtigen [4].

Des Weiteren spielen FMCW-Radare eine wichtige Rolle in der Medizintechnik, insbesondere bei der Bildgebung und Diagnose, indem sie es ermöglichen, Gewebe und biologische Materialien präzise zu analysieren, ohne invasive Eingriffe vornehmen zu müssen. FMCW-Radare bieten außerdem mehrere Vorteile

Marius Patzer maleopa@gmx.de, Serdal Ayhan serdal.ayhan@h-ka.de, Herman Jalli Ng herman-jalli.ng@h-ka.de, Fakultät Elektround Informationstechnik, Hochschule Karlsruhe, 76133 Karlsruhe, Deutschland.

Nicolas Treier nicolas.treier@hs-offenburg.de, Marlene Harter marlene.harter@hs-offenburg.de, Fakultät Elektrotechnik, Medizintechnik und Informatik, Hochschule Offenburg, 77652 Offenburg, Deutschland.

Abbildung 1. Prinzipdarstellung FMCW-Radar.

gegenüber Vektor-Netzwerkanalysatoren (VNAs), wie beispielsweise die Erzielung einer sehr niedrigen Zwischenfrequenz (ZF)-Bandbreite und die Reduzierung der Komplexität und der Kosten der Analog-Digital (AD)-Wandler [5].

#### II. KONZEPT / PRINZIP

#### A. FMCW-Prinzip

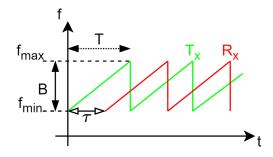

Bei einem FMCW-Radarsensor wird die Frequenz des Sendesignals über die Zeit verändert. Es entsteht eine Frequenzrampe mit einer Bandbreite B und einer Anstiegszeit T (vgl. Abbildung 1).

Das Empfangssignal  $R_x$  wird zur Auswertung mit dem Sendesignal  $T_x$  gemischt. Das daraus resultierende Signal  $s_{ZF}$  besitzt die Frequenz  $f_{ZF}$ , welche als Zwischenfrequenz bezeichnet wird.

$$s_{ZF}(t) = cos(2\pi \cdot f_{ZF} \cdot t + \varphi_{ZF}) \tag{1}$$

$$f_{ZF} = f_{T_X} - f_{R_X} = k \cdot \tau = \frac{B}{T} \cdot \frac{2R}{c_0}$$

(2)

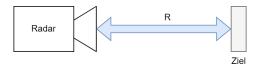

Die Zwischenfrequenz  $f_{ZF}$  ist deutlich niedriger als die ausgesendete Frequenzrampe des Sendesignals. Das resultierende Signal  $s_{ZF}$  kann somit direkt von einem Analog-Digital-Wandler abgetastet werden, ohne vorher heruntergemischt werden zu müssen. Die Variable k gibt die Steigung der Frequenzrampe an. Diese besteht aus dem Verhältnis zwischen der Bandbreite B und der Anstiegszeit T. Proportional mit der Höhe der Zwischenfrequenz  $f_{ZF}$  verändert sich auch die Distanz R zum Ziel (Abbildung 2).

Wenn sich das Ziel im Detektionsbereich des Radarsensors befindet, kann die Laufzeit  $\tau$  des Sende-

Abbildung 2. Darstellung der Signallaufzeit.

Abbildung 3. Laufzeitmessung zur Metallplatte.

und Empfangssignals aus der gemessenen Zwischenfrequenz  $f_{ZF}$  wie in (3) berechnet werden:

$$\tau = \frac{f_{ZF}}{\frac{B}{T}} = \frac{2R}{c_0} \tag{3}$$

Die Ausbreitungsgeschwindigkeit der elektromagnetischen Welle in der Luft wird dabei als die Lichtgeschwindigkeit  $c_0$  angenommen.

#### B. Messung von Laufzeitunterschieden

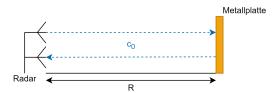

Um ein Material charakterisieren zu können, muss die Ausbreitungsgeschwindigkeit  $c_1$  der elektromagnetischen Welle in diesem Medium bestimmt werden. Dazu wird in einer definierten Distanz R eine Metallplatte platziert (vgl. Abbildung 3) und die Laufzeit des Signals über die gemessene Zwischenfrequenz  $f_{ZF_0}$  ermittelt (siehe (4)).

$$\tau_0 = \frac{f_{ZF_0}}{\left(\frac{B}{T}\right)} = \frac{2R}{c_0} \tag{4}$$

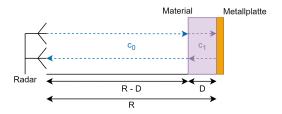

Diese Messung wird im weiteren Verlauf als Referenzmessung bezeichnet. Im nächsten Schritt wird ein Material mit einer bekannten Dicke D vor die Metallplatte gestellt. Die Distanz zwischen der Metallplatte und dem Radarsensor wird dabei nicht verändert (vgl. Abbildung 4).

Das empfangene Signal enthält zwei verschiedene Frequenzen  $f_{ZF_0}$  und  $f_{ZF_1}$ .  $f_{ZF_0}$  entspricht der Distanz zwischen der vorderen Kante des zu charakterisierenden Materials und dem Radarsensor, also R-D. Die Frequenz  $f_{ZF_1}$  entspricht wie in Abbildung 3 dargestellt der Distanz zwischen der Metallplatte und dem Radarsensor. Dadurch lässt sich folgende Gleichung für die Laufzeit  $\tau_1$  aufstellen:

$$\tau_1 = \frac{f_{ZF_1}}{\left(\frac{B}{T}\right)} = \frac{2R}{c_0} - \frac{2D}{c_0} + \frac{2D}{c_1} \tag{5}$$

Die Laufzeit  $\tau_1$  ist größer als  $\tau_0$ , da die Ausbreitungsgeschwindigkeit der elektromagnetischen Welle

Abbildung 4. Laufzeitmessung zu Material und Metallplatte.

im Medium gedämpft wird. Daraus ergibt sich die Differenz der Laufzeiten aus (4) und (5). Diese lassen sich wie folgt nach der Ausbreitungsgeschwindigkeit  $c_1$  auflösen:

$$\tau_1 - \tau_0 = -\frac{2D}{c_0} + \frac{2D}{c_1} \tag{6}$$

$$c_1 = \frac{c_0}{\sqrt{\epsilon_r \mu_r}} = \frac{2D}{\tau_1 - \tau_0 + \frac{2D}{c_0}}$$

(7)

Da die relative Permeabilität  $\mu_r$  in den meisten Materialien nahe bei 1 liegt, kann diese für die weitere Betrachtung vernachlässigt werden. Die relative Permittivität  $\epsilon_r$  eines Materials bestimmt sich daher wie folgt:

$$\epsilon_r = \left(c_0 \cdot \frac{\tau_1 - \tau_0 + \frac{2D}{c_0}}{2D}\right)^2 \tag{8}$$

#### III. HARDWARE

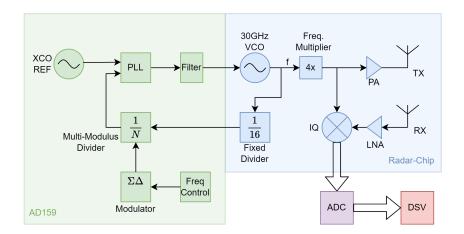

Die für die Messung verwendeten Komponenten lassen sich durch drei wesentliche Funktionsblöcke darstellen (siehe Abbildung 5). Diese Funktionsblöcke werden in den nachfolgenden Abschnitten erläutert.

#### A. PLL

Um den Frequenz-Sweep für das Sendesignal zu erzeugen, wird eine Phasenregelschleife (phase-locked loop (PLL)) eingesetzt. Über diese wird sichergestellt, dass die erzeugten Frequenzen des Sweeps stabil sind und nicht driften.

Der PLL-Chip *ADF4159* befindet sich auf einem Entwicklungsboard von *Analog Devices*. Mithilfe einer USB-Schnittstelle können die Register über ein Computerprogramm passend für den Anwendungsfall konfiguriert werden.

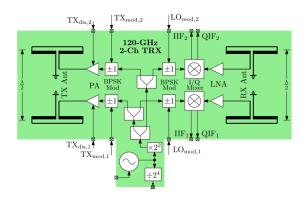

#### B. Sensor

Als Radarsensor wird ein miniaturisierter 120 GHz 2-Kanal-Radarsensor im System-on-Chip-(SoC) Design für Single Input Multiple Output-(SIMO) und Multiple Input Multiple Output-(MIMO) Radaranwendungen verwendet. Dieser Chip ist ausgestattet mit Binary Phase-Shift Keying-(BPSK) Modulatoren und I/Q-Empfänger sowie einem 30 GHz Voltage-Controlled Oscillator (VCO) und einem Frequenzvervierfacher. Die On-Chip gefalteten Dipolantennen

Abbildung 5. Schematische Darstellung der Transceiverarchitektur.

Abbildung 6. Blockdiagramm des 120 GHz Radarsensors [6].

sind mit einer Rückseitenätztechnik aufgetragen [6]. In Abbildung 6 ist das Blockschaltbild des Sensors dargestellt.

Der Radarchip befindet sich auf einer Entwicklungsplatine, auf der die Anschlüsse über Stiftleisten herausgeführt sind. Mit BNC-Kabeln wird ein I/Q Empfangskanal des Radarsensors über ein USB-Oszilloskop ausgelesen.

#### C. Analog/Digital-Wandlung

Die Abtastung des resultierenden Signals  $s_{ZF}$  erfolgt mittels eines USB-Oszilloskop, dem Analog Discovery 2 (AD2) von Digilent. Von dem PLL-Chip aus Kapitel III-A wird ein "Trigger"-Signal gesendet, sobald ein neuer Frequenz-Sweep erfolgt. Dieses Signal startet die Aufzeichnung des Analog/Digital-Wandlers.

#### D. Digitale Signalverarbeitung

Ein Python-Programm übernimmt sowohl die Steuerung des USB-Oszilloskops sowie die Durchführung der digitalen Signalverarbeitung (DSV). Mithilfe der mitgelieferten Dynamic Link Library (DLL) werden die aufgezeichneten Daten aus dem Speicher des USB-Oszilloskops ausgelesen und in einer CSV-Datei abgelegt. Die aufgezeichneten Daten werden anschließend

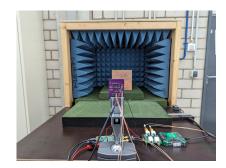

Abbildung 7. Messaufbau mit selbst gebauter Messkammer.

gemittelt, um das Rauschen zu minimieren. Weiterhin wird eine Fast Fourier Transformation (FFT) durchgeführt, um die Lage der Frequenzpeaks zu lokalisieren. Diese können in einem weiteren Schritt mittels einer Zoom FFT genauer analysiert werden. Aus den ermittelten Zwischenfrequenzen und den berechneten Laufzeiten wird nun wie in (8) beschrieben, die relative Permittivität bestimmt.

#### IV. MESSAUFBAU

Der Messaufbau erfolgt nach dem vorgestellten Prinzip aus Kapitel II-B. In einem Abstand von 60 cm wird eine Metallplatte vor dem Radarsensor platziert (vgl. Abbildung 7).

Die Metallplatte befindet sich in einer selbstgebauten Messkammer, die mit Pyramidenabsorber ausgekleidet ist, um die Umgebungseinflüsse zu minimieren. Mithilfe einer Linse auf dem Radarsensor wird sichergestellt, dass nur der Bereich, in dem sich die Metallplatte befindet, erfasst wird.

Nach der Referenzmessung werden verschiedene Dicken von Kunststoffblöcken vor die Metallplatte platziert und die Laufzeit wie in Abbildung 4 ermittelt.

Die verwendeten Kunststoffblöcke sind in Abbildung 8 zu sehen. Tabelle I listet weitere Materialeigenschaften auf.

Abbildung 8. Kunststoff blau und Kunststoff braun.

#### Tabelle I MATERIALEIGENSCHAFTEN

| Material            | Eigenschaften                                                               | Verwendete Größen                                                        |

|---------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Metallplatte        | Kupfer Dichte $8,92 \frac{g}{cm^3}$                                         | Blockgröße: 150 mm × 150 mm<br>Dicke: 2 mm                               |

| Kunststoff<br>braun | SikaBlock® M600 N<br>Polyurethan, hellbraun<br>Dichte 0,6 g/cm <sup>3</sup> | Blockgröße: 150 mm × 150 mm<br>Dicken:<br>25 mm, 50 mm, 75 mm,<br>100 mm |

| Kunststoff<br>blau  | SikaBlock® M960<br>Polyurethan, blau<br>Dichte 1,2 $\frac{g}{cm^3}$         |                                                                          |

#### V. MESSERGEBNISSE

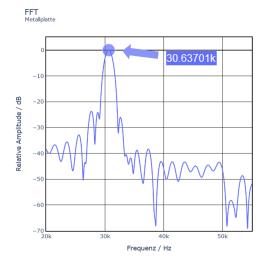

#### A. Auswertung der FFT Daten

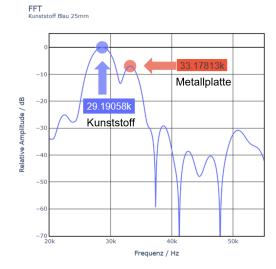

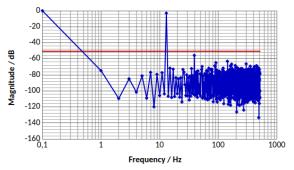

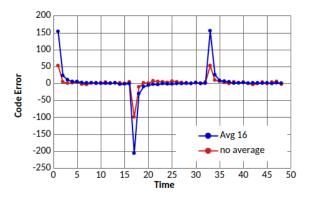

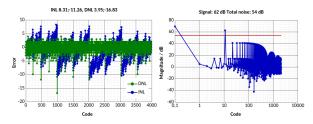

Die aufgezeichneten Daten werden wie in Kapitel III-D beschrieben ausgewertet. In Abbildung 9 ist die FFT der Referenzmessung nach dem Messprinzip aus Abbildung 3 dargestellt. Dabei zeigt sich ein signifikanter Peak bei  $f_{ZF_0}=30,64\,\mathrm{kHz}$ , der von der Metallplatte verursacht wird.

Abbildung 10 zeigt die FFT einer Messung mit Kunststoffblock und Metallplatte. Man erkennt zwei signifikante Frequenzpeaks bei  $f_{ZF_0}=29,19\,\mathrm{kHz}$  und  $f_{ZF_1}=33,18\,\mathrm{kHz}.$  Die erste Frequenz  $f_{ZF_0}$  entspricht der Distanz zwischen der vorderen Kante des Kunststoffblocks und dem Radarsensor. Die Distanz zwischen Metallplatte und Radarsensor wird durch die zweite Frequenz  $f_{ZF_1}$  repräsentiert (vgl. Kapitel II-B).

Unter Annahme einer identischen Ausbreitungsgeschwindigkeit erscheint die Metallplatte weiter entfernt, obwohl die Positionierung der Metallplatte bei beiden Messungen identisch ist. Die Frequenzverschiebung und damit die erhöhte Laufzeit  $\tau_1$  des Signals im Vergleich zur Referenzmessung  $\tau_0$  resultiert jedoch aus der verringerten Ausbreitungsgeschwindigkeit der elektromagnetischen Welle im Kunststoffblock. Durch die bekannte Dicke des Kunststoffblocks und damit der Entfernung zum Radarsensor kann der Messaufbau über die Frequenz  $f_{ZF_0}$  verifiziert werden.

#### B. Auswertung der relativen Permittivität

Wie die Messungen gezeigt haben, können für die Charakterisierung der unterschiedlichen Materialien nicht alle Materialstärken zur Auswertung herangezogen werden. In der FFT des braunen Kunststoffblocks

Abbildung 9. FFT-Plot der Messung mit Metallplatte.

Abbildung 10. FFT-Plot der Messung mit Kunststoffblock und Metallplatte.

mit der Dicke 25 mm sind die beiden Frequenzpeaks überlagert und ermöglichen somit keine eindeutige Bestimmung der Laufzeit.

Die blauen Kunststoffblöcke ab einer Dicke von 50 mm absorbieren das ausgesendete Signal so weit, dass der Frequenzpeak der Metallplatte im Rauschen des Signals verschwindet. Das gleiche Phänomen tritt bei dem braunen Kunststoffblock mit einer Dicke von 100 mm auf.

Aus diesem Grund werden bei dem blauen Kunststoff nur die Dicke 25 mm und bei dem braunen Kunststoff nur die Dicken 50 mm und 75 mm für die Ermittlung der relative Permittivität herangezogen. Die berechneten Werte des braunen Kunststoffs werden anschließend gemittelt. In Tabelle II sind die Ergebnisse aufgelistet:

Es liegen keine Referenzwerte für die verwendeten Materialien bei 120 GHz vor. Daher können die er-

Tabelle II

RELATIVE PERMITTIVITÄTEN DER VERWENDETEN KUNSTSTOFFE

| Kunststoff | Relative Permittivität |

|------------|------------------------|

| Braun      | 2,05                   |

| Blau       | 3,22                   |

mittelten Ergebnisse nur als Anhaltspunkte für weitere Messungen verwendet werden. Durch ein Referenzmaterial mit bekannter relativer Permittivität  $\epsilon_r$  bei  $120~\mathrm{GHz}$  kann das Messprinzip verifiziert werden.

#### VI. ZUSAMMENFASSUNG & AUSBLICK

Die Ergebnisse der Messungen zeigen, dass grundsätzlich eine Bestimmung der relativen Permittivität für unbekannte Materialien möglich ist. Für zukünftige Messungen wird ein Referenzmaterial bei 120 GHz für die Einordnung der Messwerte benötigt. Statistisch signifikante Aussagen sind über mehrere geeignete Materialstärken zu erreichen. Über eine genauere Positionierung der Materialproben kann der Messaufbau optimiert und die Wiederholungsgenauigkeit der Messungen verbessert werden.

Mit dem Radarsensor soll es künftig möglich sein, feine Materialunterschiede und Strukturen zu erkennen.

#### LITERATURVERZEICHNIS

- [1] J. Jebramcik, I. Rolfes and J. Barowski, "A Novel Calibration Technique for FMCW Radar Systems Enabling Material Characterization in Variable Distances," 2019 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Bochum, Germany, 2019, pp. 106-108, doi: 10.1109/IMWS-AMP.2019.8880110.

- [2] S. Battistutta, M. Bressan, M. Bozzi and L. Perregrini, "Material characterization through a full-wave approach based on the BI-RME method," 2017 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Pavia, Italy, 2017, pp. 1-3, doi: 10.1109/IMWS-AMP.2017.8247348.

- [3] G. L. Friedsam and E. M. Biebl, "Precision free-space measurements of complex permittivity of polymers in the W-band," 1997 IEEE MTT-S International Microwave Symposium Digest, Denver, CO, USA, 1997, pp. 1351-1354 vol.3, doi: 10.1109/MWSYM.1997.596579.

- [4] M. S. Hilario et al., "W -Band Complex Permittivity Measurements at High Temperature Using Free-Space Methods," in IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 9, no. 6, pp. 1011-1019, June 2019, doi: 10.1109/TCPMT.2019.2912837.

- [5] S. Abouzaid, T. Jaeschke, J. Barowski and N. Pohl, "FMCW Radar-Based Material Characterization Using Convolutional Neural Network and K-Means Clustering," 2022 24th International Microwave and Radar Conference (MIKON), Gdansk, Poland, 2022, pp. 1-4, doi: 10.23919/MIKON54314.2022.9924681.

- [6] H. J. Ng and D. Kissinger, "Highly Miniaturized 120-GHz SIMO and MIMO Radar Sensor With On-Chip Folded Dipole Antennas for Range and Angular Measurements," in IEEE Trans. on Microwave Theory and Techniques, vol. 66, no. 6, pp. 2592-2603, June 2018.

Marius Patzer wurde 1998 in Karlsruhe geboren. Nach seinem Abitur 2018 absolvierte er ein Bachelorstudium im Bereich Nachrichtentechnik an der Dualen Hochschule Baden-Württemberg (DHBW) Karlsruhe, das er im September 2021 erfolgreich abschloss. Im Anschluss war er ein Jahr lang bei seinem ehemaligen dualen Partner Physik Instrumente (PI) GmbH & Co. KG im Bereich der Sensor- und Firmware-Entwicklung tätig. Seit Oktober

2022 absolviert Marius Patzer den Masterstudiengang im Bereich Informationstechnik an der Hochschule Karlsruhe.

Nicolas Treier schloss sein Bachelorstudium in Elektrotechnik und Informationstechnik an der Hochschule Offenburg (HSO) erfolgreich im Jahr 2021 ab. Im Jahr 2023 beendete er sein Masterstudium an der HSO mit Auszeichnung. Seit Mai 2023 arbeitet er am Institute for Unmanned Aerial Systems als Mitarbeiter mit einem Fokus auf Millimeterwellen-Anwendungen in der Medizin.

Marlene Harter schloss ihr Studium der Elektro- und Informationstechnik zum Dipl.-Ing. an der Universität Karlsruhe (TH) im Jahr 2008 ab. Nach ihrem Studium arbeitete sie als wissenschaftliche Mitarbeiterin an der École Polytechnique de Lausanne und anschließend bei der Siemens AG. Im Jahr 2014 promovierte Marlene Harter in Zusammenarbeit mit der Siemens AG am Karlsruher Institut für Technologie (KIT). Während ihrer Promo-

tion forschte sie über ein dreidimensional bildgebendes Radarsystem mit digitaler Strahlformung für industrielle Anwendungen. Von 2014 bis 2018 arbeitete sie bei der Robert Bosch GmbH in Leonberg im Bereich der radarbasierten Fahrerassistenzsysteme. In dieser Zeit leitete sie mehrere Kundenprojekte und war Projektleiterin für das Seitenradar der 5. Generation für PKWs und LKWs. Im Oktober 2018 wurde Marlene Harter als Professorin an die Hochschule Offenburg im Bereich der Hochfrequenztechnik und Elektronik berufen. Dort ist sie seit 2022 Leiterin des Institute for Unmanned Aerial Systems. Sie erhielt 2008 den Werner von Siemens Excellence Award für ihre Diplomarbeit und den Best Paper Award auf der IEEE CIE International Conference on Radar in 2011. Im Jahr 2023 war sie Technical Program Chair der 20th European Radar Konferenz (EuRAD) in Berlin.

Serdal Ayhan schloss im Jahr 2009 sein Diplomstudium der Nachrichtentechnik/Elektronik und im Jahr 2010 das nachfolgende Masterstudium Informationstechnik an der Hochschule Mannheim ab. Im Jahr 2015 promovierte er am Institut für Hochfrequenztechnik und Elektronik des Karlsruher Instituts für Technologie (KIT) mit Schwerpunkt industrielle Radar-Sensorik für hochgenaue, radarbasierte Abstandsmessungen im Mikrometer-Bereich.

Nach seiner Promotion hat er bei der Valeo Schalter und Sensoren GmbH als Systemingenieur in der Vorausentwicklung für 79 GHz Radarsensoren in Fahrzeugen gearbeitet. In den Jahren 2016-2020 arbeitete er bei der SEW-Eurodrive GmbH & Co KG im Fachkreis Funk & Navigation an der Integration von Radarsensoren in smarte, autonom fahrende Förderfahrzeuge. Seit 2020 ist er an der Fakultät für Elektro- und Informationstechnik der Hochschule Karlsruhe Professor für Hochfrequenz- und Radartechnik.

Herman Jalli Ng schloss im Jahr 2005 sein Studium als Dipl.-Ing.(FH) an der Hochschule Karlsruhe in Deutschland ab und erwarb 2014 den Doktortitel in Mechatronik an der Johannes Kepler Universität Linz in Österreich. Von 2005 bis 2009 war er als ASIC-Entwickler bei der Robert Bosch GmbH in Reutlingen tätig, bevor er von 2009 bis 2015 als wissenschaftlicher Mitarbeiter an der Johannes Kepler Universität Linz arbeitete. In den Jahren

2015 bis 2020 leitete er erfolgreich die mm-Wave Wireless Forschungsgruppe am IHP Microelectronics. Seit 2020 ist er Professor an der Hochschule Karlsruhe. Er hat über 100 Zeitschriften- und Konferenzartikel verfasst, sowohl als Autor als auch als Co-Autor. Für seine wegweisenden Arbeiten im Bereich integrierter skalierbarer mm-Wellen-Radar-Transceiver in SiGe-BiCMOS-Technologien wurde ihm der VDE ITG-Preis 2018 und der APMC Best Paper Award 2019 verliehen. Zudem war er Mitpreisträger des IEEE Microwave Prize Award 2023 der IEEE Microwave Theory and Technology Society (MTT-S), des VDE/VDI GMM-Preises 2017 und des GAAS Association Student Fellowship 2019.

# Realisierung von elektronischen und sensorischen Komponenten mittels FDM-3D-Druck-Verfahren

Jannik Söll, Patrick Hog, Elke Mackensen

Zusammenfassung—Im Rahmen dieses Papers wird auf die Realisierung von elektronischen und sensorischen Komponenten mittels FDM-3D-Druck-Verfahren unter Einsatz von leitenden Filamenten eingegangen. Präsentiert werden Untersuchungsergebnisse leitfähiger Filamente, daraus abgeleitete Designrichtlinien und die Ergebnisse aus der Realisierung beispielhafter Komponenten.

Schlüsselwörter—3D-Druck, gedruckte Schaltungen, gedruckte Elektronik

#### I. EINLEITUNG

Gedruckte Elektronik wird zu diesem Zeitpunkt üblicherweise durch zweidimensionale Druckverfahren hergestellt. Etablierte Verfahren zweidimensionalen Drucks sind klassische Verfahren wie die PCB-Herstellung mittels Ätztechniken und der Druck funktionaler Tinten oder leitender Pasten auf flache Oberflächen. Beispiele hierfür sind der Tiefdruck, der Siebdruck oder der Tintenstrahldruck. Auf Grund der zunehmenden Verfügbarkeit zuverlässiger, kostengünstiger 3D-Drucker und leitfähiger Filamente gewinnt die Herstellung von leitfähigen, dreidimensionalen Strukturen zunehmend an Bedeutung. Die Möglichkeit mittels leitfähiger Materialien eine zusätzliche PCB-Fertigung einzusparen und leitfähige Pfade sowie elektronische oder sogar sensorische Komponenten direkt in ein Produkt einzubetten, sind nur einige Beispiele für die Motivation sich mit dieser Thematik zu beschäftigen.

Nach einem kurzen Überblick zum Stand der Technik wird im Rahmen des Papers auf die elektrischen Eigenschaften experimentell untersuchter leitfähiger Filamente eingegangen. Es wird aufgezeigt, welcher Einfluss der 3D-Druck auf die finalen Eigenschaften von 3D-gedruckten elektronischen und sensorischen Komponenten hat, welche Herausforderungen hierbei bestehen und welche generellen Designrichtlinien sich für den 3D-Druck elektronischer Systeme ableiten lassen. Zudem werden die Messergebnisse aus dem Druck beispielhafter Komponenten wie Widerständen, Kondensatoren, einem Füllstandssensor und einem kleinen kompletten Produkt vorgestellt.

Jannik Söll, jsoell@stud.hs-offenburg.de, Patrick Hog, patrick.hog@hs-offenburg.de, Elke Mackensen, elke.mackensen@hs-offenburg.de. Hochschule für Technik, Wirtschaft und Medien Offenburg, Badstraße 24, 77652 Offenburg.

Abbildung 1. Aufbau eines 3D-Druckers in Gantry-Bauweise.

#### II. STAND DER TECHNIK

Beim 3D-Druck handelt es sich um ein additives Fertigungsverfahren, bei dem Material, z.B. Kunststoff, Metall oder Keramik, mittels eines 3D-Druckers Schicht für Schicht aufgetragen wird, um ein dreidimensionales Objekt zu erzeugen. Ausgangsbasis ist ein digitales 3D-Modell des Objektes, das gefertigt werden soll. Das digitale 3D-Modell wird üblicherweise durch eine spezielle Software in eine Vielzahl von dünne Schichten zerlegt und dann als G-Code-Format exportiert. Dieser Code dient zur Ansteuerung des 3D-Druckers. Jede Schicht entspricht der exakten 2D-Form eines Abschnitts oder einer Scheibe des Objekts [1].

Es gibt eine Vielzahl an 3D-Drucktechnologien. Die bekanntesten Verfahren in diesem Bereich sind die Filament-Extrusion (engl. "Fused Filament Fabrication" bzw. "Fused Deposition Modeling", kurz FFF bzw. FDM) und die Vat-Photopolymerisation (kurz VPP, engl. "vat" = Tank) mit den Unterverfahren Stereolithografie (SLA), "Digital Light Processing" (DLP) sowie "Masked Stereolithography" (MSLA).

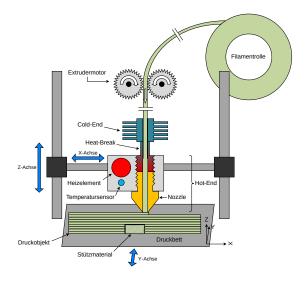

Für die Untersuchungen, deren Ergebnisse im Rahmen dieses Beitrags vorgestellt werden, wurden FDM-Drucker verwendet, um 3D-gedruckte elektronischen und sensorischen Komponenten zu fertigen. FDM-

Abbildung 2. Schematischer Aufbau leitfähiger Filamente.

Drucker ermöglichen kostengünstige und schnelle Prototypenfertigung. Abbildung 1 zeigt den Aufbau eines FDM-Druckers, hier in Gantry-Bauweise [2]. Das FDM-Verfahren verwendet zur additiven Fertigung ein auf Rollen aufgewickeltes Kunststoff-Filament. Das Filament wird in einem Extruder aufgeschmolzen und durch eine Düse mit definiertem Durchmesser (= Nozzle) gepresst bzw. extrudiert. Das aufgeschmolzene Material wird dann durch Bewegung des Druckkopfes schichtweise auf dem Druckbett aufgetragen. Der Extruder selbst besteht aus mehreren Teilen. Das Filament wird vom Extrudermotor in Richtung Nozzle bewegt. Die restlichen Teile auf dem Weg des Filaments bis zum Verlassen der Nozzle werden als Cold-End, Heatbreak und Hot-End bezeichnet. Beim Cold-End handelt es sich um einen Kühlkörper, der die vom Hot-End und der Düse aufsteigende Wärme ableitet, um ein zu frühes Erweichen des Filaments zu verhindern. Die Heatbreak erhöht durch einen geringen Querschnitt den Wärmewiderstand und begünstigt so zum einen die Kühlung durch das Cold-End, und zum anderen das Aufheizen und Halten der Temperatur des Hot-End. Das Hot-End besteht aus dem Heizblock mit Heizelement und Temperatursensor sowie der Druckdüse. Innerhalb des Hot-End wird das Filament aufgeschmolzen und durch das vom Extrudermotor nachgeförderte Filament aus der Düse gepresst. Die Druckdüsen gibt es in verschiedenen Größen, Öffnungsgrößen und Materialien. Weit verbreitet sind Messingdüsen mit einem Öffnungsdurchmesser von 0,4 mm [2].

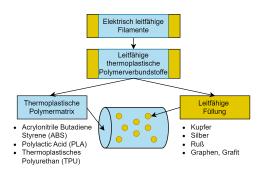

Die Herstellung von leitfähigen 3D-Strukturen wird durch leitfähige Filamente ermöglicht. Elektrisch leitfähige Filamente bestehen, wie in Abbildung 2 dargestellt, aus einem leitfähigen thermoplastischen Polymerverbundstoff. Dieser besteht aus einer thermoplastischen Polymermatrix als Basismaterial und einer leitfähigen Füllung, die in dem Polymermatrixmaterial eingebettet ist. Das Polymermatrixmaterial wird verwendet, um die leitfähige Füllung zu umhüllen und eine stabile Form zu erhalten. Bei den in Abbildung 2 angegebenen Stoffen handelt es sich um Polymermaterialien, die üblicherweise für den FDM-Druck verwendet werden. Die leitfähige Füllung kann aus

Materialien wie Kupfer, Silber oder auf Kohlenstoff basierenden Materialien wie Ruß, Graphen, Grafit, Kohlenstoffnanoröhren, Graphitfolie und anderen Kohlenstoffmaterialien bestehen und dient als Stromleiter im Filament. Die Verfügbarkeit verschiedener Verbundwerkstoffe erzeugt eine Vielzahl mechanischer, elektrischer und thermischer Eigenschaften [3, 4, 5].

Verschiedene Forschungsgruppen beschäftigen sich weltweit mit der Realisierung von elektronischen Komponenten basierend auf 3D-druckbaren leitfähigen thermoplastischen Filamenten. Jangid, Strong et al. haben den Druck von flexiblen Schaltkreisen auf Papier mittels leitfähiger Filamente untersucht. Dabei wurden jedoch nur die Leiterbahnen gedruckt [3]. Flowers et al. haben die Dual-Material-Fused-Filament-Fertigung für den 3D-Druck elektronischer Komponenten und Schaltungen genutzt. Dabei sind beispielsweise experimentell Leiter, Widerstände, Kondensatoren und Induktoren und andererseits auch komplexere Komponente wie Hochpassfilter und Empfängerspulen für die drahtlose Energieübertragung entstanden [6]. Kwok et. al. haben neben einfachen eingebetteten Leiterbahnen unter anderem auch einen Temperatursensor realisiert [7]. Die in der Literatur vorzufindenden Ergebnisse haben alle gemeinsam, dass die Ergebnisse für die Realisierung elektronischer Komponenten weitestgehend experimentell erzielt wurden, aber nicht auf beschriebenen Designrules basieren. Im Rahmen dieses Papers werden anhand der Untersuchungsergebnisse elektrisch leitfähiger Filamenten erste Designrichtlinien formuliert (siehe Abschnitt III). Aufbauend auf den ermittelten Eigenschaften und den formulierten Gestaltungsrichtlinien wurden gezielt beispielhafte elektronische und sensorische Komponenten entwickelt, die in Abschnitt IV vorgestellt werden.

#### III. ERGEBNISSE AUS DER UNTERSUCHUNG ELEKTRISCHER EIGENSCHAFTEN VON LEITFÄHIGEN FILAMENTEN

Es wurden unterschiedliche leitfähige Filamente untersucht. Hierbei handelt es sich um.

- Proto-Pasta (= PP) [8]

- AIMPLA FILI (= AF) [9]

- Multi3D Electrifi (= EL) [10]

Als FDM-Drucker kamen der Ultimaker S5 und der Prusa i3 MK3S für die Fertigung der Untersuchungsobjekte sowie der elektronischen/sensorischen Komponenten zum Einsatz. Vorgestellt werden die Ergebnisse, die mit dem Proto-Pasta-Filament erzielt wurden.

Die generelle Vorgehensweise bei den Untersuchungen war wie folgt: Zunächst wurde ein CAD-Modell für 3D-Proben aus dem leitenden Filament entworfen. Danach wurden die Proben gedruckt. Vor der Messung wurde die Oberfläche der Probe noch mit Leitsilber veredelt, um einen möglichst geringen Übergangswiderstands zwischen Mess-Spitze und Oberfläche der

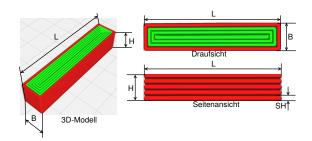

Abbildung 3. CAD-Modell der Messprobe in 3D-Ansicht, Draufsicht und Seitenansicht.

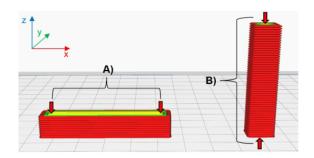

Abbildung 4. Messung des Widerstandes in X-Richtung (A) und in Z-Richtung (B).

Probe zu erhalten. Danach wurden die Messungen durchgeführt. Je nach Messung wurden die Proben variiert, z.B. in der Länge, Breite und Höhe.

#### A. Untersuchung des resistiven Verhaltens

In diesem Abschnitt werden Messergebnisse vorgestellt, die mit dem Filament Proto-Pasta (= PP) aufgenommen wurden. Die Messergebnisse können aber auch auf die anderen untersuchten Filament-Typen übertragen werden. Generell ist anzunehmen, dass sich der Ohmsche Widerstand R eines gedruckten Objektes nach Formel (1) verhält:

$$R = \rho \cdot \frac{L}{B \cdot H} \tag{1}$$

mit  $\rho$  = Spezifischer Widerstand des Materials

L = Länge des Objektes B = Breite des Objektes H = Höhe des Objektes

Zunächst wurde der im Datenblatt angegebene spezifische Widerstand des Filaments messtechnisch überprüft. Das CAD-Modell der Material-Probe (ohne die Messanschlüsse), mit der die Messung durchgeführt wurde, ist in Abbildung 3 dargestellt. In der Seitenansicht sind deutlich die übereinander gedruckten Schichten zu erkennen, die eine Höhe SH aufweisen. In der Draufsicht ist zu erkennen, dass die einzelnen Schichten in Bahnen verlaufen, die abhängig vom Durchmesser der Druckdüse sind.

Dem Datenblatt des PP-Filaments kann entnommen werden, dass der spezifische Widerstand des Materials

Abbildung 5. Proben zur Messung des Widerstandes in X-Richtung.

abhängig von der Richtung des Stromverlaufs in der Probe (siehe Abbildung 4) ist. Im Fall A ist der Stromfluss in X-Richtung, im Fall B ist der Stromfluss in Z-Richtung. Den Datenblättern der anderen Filamente konnte hierzu keine Angabe entnommen werden, es ist jedoch anzunehmen, dass entsprechendes Verhalten vorzufinden ist, da eine Stromflussrichtung in Z-Richtung bedeutet, dass sich das Material beim Drucken zwischen den Schichten deutlich schlechter verbindet und inhomogener ist, als in X-Richtung.

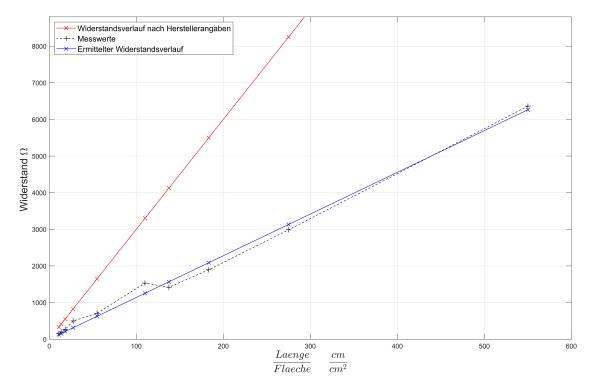

Entsprechend Abbildung 4 wurden Proben gedruckt, um den Widerstand zu messen und damit den spezifischen Widerstand des Materials zu berechnen. Abbildung 5 zeigt die Proben zur Messung des Widerstandes R der Proben und zur Ermittlung des sich daraus ergebenden spezifischen Widerstand ρ. Abbildung 6 zeigt die Messung des Widerstands für das Material PP bei einer Messung des Widerstandes in X-Richtung (siehe Abbildung 4A). Im Vergleich dazu ist der theoretische Widerstandsverlauf auf Grund der Datenblattangaben des Herstellers dargestellt, der den spezifischen Widerstand bei Messung in X-Richtung mit  $\rho_x = 30 \,\Omega$  cm angibt. Aus der Messung ergibt sich ein tatsächlicher spezifischer Widerstand von  $\rho_{ist,x}$  =  $11,39\,\Omega\,\mathrm{cm}$ . Ähnlich Resultate wurden bei der Ermittlung des spezifischen Widerstandes durch Messung des PP-Materials in Z-Richtung (siehe Abbildung 4B) erzielt. Laut Datenblattangaben des Herstellers gibt dieser den spezifischen Widerstand bei Messung in Z-Richtung mit  $\rho_z = 115 \,\Omega\,\mathrm{cm}$  an. Aus der Messung ergibt sich ein tatsächlicher spezifischer Widerstand von  $\rho_{\text{ist},z} = 19,56 \,\Omega \,\text{cm}$ .

Bei beiden Messungen zeigte sich, dass der tatsächliche spezifische Widerstand  $\rho_{\rm ist}$  stark von den Herstellerangaben abweicht. Beide Ergebnisse legen nahe, dass der Druckprozess einen starken Einfluss auf die resultierenden elektrischen Eigenschaften des Endprodukts hat. Aus diesem Grund wurde in einem nächsten Schritt jeweils die Längen, Breiten und Höhen der Proben geändert und die gleiche Probe auf zwei unterschiedlichen Druckern gedruckt (einem Prusa und einem Ultimaker). Bei den Messungen

Abbildung 6. Messung des Widerstandes von PP-Proben in X-Richtung in Abhängigkeit der Länge pro Fläche.

Tabelle I

ERMITTELTER SPEZIFISCHER WIDERSTAND BEI MESSUNG DES

WIDERSTANDS DER PP-PROBEN IN X-RICHTUNG UND

VARIATION DER LÄNGEN, BREITEN UND HÖHEN DER PROBEN

UND DRUCK DER PROBEN AUF UNTERSCHIEDLICHEN

FDM-DRUCKERN

| Variierte Größe                           | Drucker                             | $ ho_{{ m ist},m{x}}$                                                     |

|-------------------------------------------|-------------------------------------|---------------------------------------------------------------------------|

| Probenlänge<br>Probenbreite<br>Probenhöhe | Prusa<br>Prusa<br>Prusa             | $12,\!80\Omega{\rm cm} \\ 12,\!76\Omega{\rm cm} \\ 12,\!18\Omega{\rm cm}$ |

| Probenlänge<br>Probenbreite<br>Probenhöhe | Ultimaker<br>Ultimaker<br>Ultimaker | $9,18\Omega\mathrm{cm} \\ 9,73\Omega\mathrm{cm} \\ 9,18\Omega\mathrm{cm}$ |

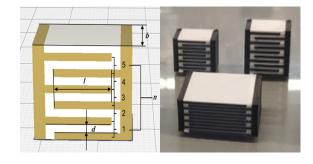

Abbildung 7. 3D-gedruckte Plattenkondensatoren.

zeigte sich, dass der Widerstand sich entsprechend der obigen Gleichung (1) verhält. Auch bei dieser Messung konnte festgestellt werden, das der ermittelte spezifische Widerstand  $\rho_{\text{ist},x}$  (siehe Tabelle I) von den Herstellerangaben abweicht, aber je nach verwendetem Drucker in der gleichen Region liegt (Ultimaker im Bereich  $9\,\Omega$  bis  $10\,\Omega$ , Prusa im Bereich von  $12\,\Omega$  bis  $13\,\Omega$ ).

#### B. Untersuchung des kapazitiven Verhaltens

Zur Untersuchung des kapazitiven Verhaltens wurden Plattenkondensatoren entsprechend Abbildung 7 gedruckt, deren Kapazitäten sich nach Formel (2) berechnen lassen:

$$C = n \cdot \epsilon_r \cdot \epsilon_0 \cdot \frac{A}{d} \tag{2}$$

mit

C = Kapazität des Kondensators

n = Anzahl der Plattenpaare des Kondensators

d = Abstand zwischen Platten des Kondensators

A = Überlappungsfläche der Kondensatorplatten

$\epsilon_0$  = Dielektrizitätskonstante des Vakuums

$\epsilon_0$  = relative dielektrische Permittivität des Dielektrikums: 2,4 - 2,8 bei einem Filament aus Polylactic Acid (= PLA)

Die Messergebnisse sind in Tabelle II dargestellt. Es zeigte sich ähnlich wie bei der Untersuchung des resistiven Verhaltens, dass sich die Kapazität gemäß Gleichung (2) verhält, auch dann wenn der Abstand der Platten und die Plattenfläche variiert wird. Allerdings weichen auch hier die tatsächlichen Messwerte immer von den erwarteten Kapazitätswerten ab.

Tabelle II

MESSERGEBNISSE AUS DEM DRUCK VON

PLATTENKONDENSATOREN BEI VARIATION DER ANZAHL DER

PLATTENPAARE

| Proben<br>Nr. | Platten-<br>paare n | Erwartete<br>Kapazitätswerte | Gemessene<br>Kapazitätswerte |

|---------------|---------------------|------------------------------|------------------------------|

| 1             | 1                   | $2,36\mathrm{pF}$            | $6,84\mathrm{pF}$            |

| 2             | 2                   | $7.07\mathrm{pF}$            | $15,68  \mathrm{pF}$         |

| 3             | 3                   | $11,78  \mathrm{pF}$         | $25,78  \mathrm{pF}$         |

| 2             | 4                   | $16,49  \mathrm{pF}$         | $34,06  \mathrm{pF}$         |

| 5             | 5                   | $21,20\mathrm{pF}$           | $44,32\mathrm{pF}$           |

Abbildung 8. Verschmelzung der Filamente am Rande des Dielektrikums bei gedruckten Kondensatoren.

Auch bei diesen Messungen liegt es nahe, dass der Druckprozess einen Einfluss auf die elektrischen Eigenschaften einer Kapazität hat. Die Messungen an einem gedruckten Kondensator zeigten, dass der Plattenabstand d und die Fläche A der Platten den im CAD-Modell vorgegebenen Abmessungen entsprachen. Jedoch zeigte sich, dass bei der Erzeugung der Proben sich während des Druckprozesses die leitfähigen und isolierenden Schichten zu einem gewissen Grad verschmelzen (siehe Abbildung 8). Diese Verschmelzung beeinflusst die dielektrischen Eigenschaften des verwendeten isolierenden PLA-Materials.

### C. Einfluss der Druckparametern auf die Eigenschaften elektrischer Komponenten

Am Beispiel des resitiven Verhaltens wurde detailliert untersucht, welchen Einfluss die folgenden Druckparameter auf die Eigenschaften elektrischer Komponenten haben:

- Druckdüsendurchmesser (nozzle size) des 3D-Druckers

- Höhe SH der gedruckten Schichten

- Drucktemperatur

Es wurden hierzu wieder Proben gemäß Abbildung 4 gedruckt. Dabei wurden jeweils die oben genannten Parameter geändert. Von diesen Proben wurde jeweils der Widerstand gemessen und dann wiederum der sich ergebende spezifische Widerstand errechnet. Zuvor wurden folgende Hypothesen aufgestellt:

Tabelle III

ERMITTELTER SPEZIFISCHER WIDERSTAND BEI MESSUNG DES

WIDERSTANDS VON PP-PROBEN IN X-RICHTUNG UNTER

VARIATION JEWEILS EINES DRUCKPARAMETERS

| Druckparameters            | Spezifischer Widerstand $ ho$ |

|----------------------------|-------------------------------|

| Nozzle Durchmesser: 0,4 mm | $11,94\Omega\mathrm{cm}$      |

| Nozzle Durchmesser: 0,6 mm | $11{,}12\Omega\mathrm{cm}$    |

| SH: 0,15 mm                | $12,65\Omega\mathrm{cm}$      |

| SH: 0,30 mm                | $10,37\Omega\mathrm{cm}$      |

| Drucktemperatur: 190 °C    | $14,01\Omega\mathrm{cm}$      |

| Drucktemperatur: 230 °C    | $10{,}41\Omega\mathrm{cm}$    |

**H1:** Je größer der Druckdüsendurchmesser, desto geringer der spezifische Widerstand  $\rho$ . Grund dafür ist, dass für das Drucken einer Schicht weniger Bahnen gedruckt werden müssen (siehe Abbildung 3), also homogenere Schichten mit einer geringeren Anzahl an Grenzbereichen entstehen.

**H2:** Je höher die Schichtstärke SH beim Druckprozess, desto geringer der ermittelte spezifische Widerstand  $\rho$ . Hierdurch werden insgesamt weniger Schichten für das Objekt benötigt, was zu weniger Grenzbereichen im Objekt führt.

**H3:** Je höher die Drucktemperatur desto geringer der spezifische Widerstand  $\rho$ . Dies liegt daran, dass bei höherer Temperatur die einzelnen Bahnen und Schichten besser miteinander verschmelzen und dadurch das Material weniger Grenzbereiche aufweist, also auch hier homogener wird.

In Tabelle III sind die entsprechenden Messergebnisse aufgeführt. Alle oben aufgeführten Hypothesen konnten messtechnisch bestätigt werden. Um also kleine Widerstandswerte zu erzielen, sollte das Bauteil aus möglichst wenigen Bahnen und Schichten bestehen und bei einer hohen Temperatur gedruckt werden.

Auch für die gedruckten Kondensatoren wurde die Drucktemperatur variiert. Hier zeigte sich, dass die gemessene relative dielektrische Permittivität des Dielektrikums bei der Fertigung mit niedrigeren Drucktemperaturen geringe Abweichungen gegenüber der bekannten relativen dielektrischen Permittivität des PLA-Filaments aufzeigte, während hohe Drucktemperaturen zu großen Abweichungen führte.

## IV. DESIGN UND REALISIERUNG BEISPIELHAFTER ELEKTRONISCHER UND SENSORISCHER KOMPONENTEN

#### A. Realisierung von Widerständen

Mit den zuvor gewonnenen Erkenntnissen wurden verschiedene elektrische Widerstände mit vorgegebenen Werten aus Proto-Pasta-Filament ausgelegt und hergestellt. Die Druckparameter waren wie folgt:

• Schichthöhe: 0,2 mm

• Druckdüsendurchmesser: 0,6 mm

• Drucktemperatur: 219 °C

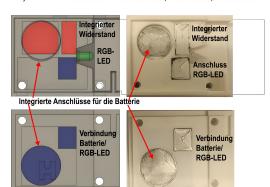

A) Alte Variante Namensschild mit Leiterkarte, Batteriehalter, Widerstand...

B) CAD-Modell und gedrucktes 3D-Objekt

C) Neue Variante Namensschild mit integrierten gedruckten Leitungen, Widerständen...

Abbildung 9. Realisierung eines beleuchteten Namensschildes im 3D-Druckverfahren mit integrierten leitenden Komponenten.

Der zuvor ermittelte tatsächliche spezifische Widerstand des Materials ist  $\rho=11\,\Omega\,\mathrm{cm}.$  Die Widerstände konnten erfolgreich realisiert werden. Es ergab sich eine Toleranz von ca.  $\pm15\,\%$  in der Genauigkeit der Auslegung der Widerstandswerte, und eine Toleranz von ca.  $\pm8\,\%$  in der Reproduzierbarkeit der Widerstandswerte.

#### B. Realisierung von Kondensatoren

Mit den zuvor gewonnenen Erkenntnissen wurden verschiedene Kondensatoren mit vorgegebenen Werten aus Proto-Pasta-Filament für die Kondensatorplatten und PLA-Filament für das Dielektrikum entworfen und hergestellt. Die Druckparameter waren wie folgt:

• Schichthöhe: 0,2 mm

• Druckdüsendurchmesser: 0,6 mm

• Drucktemperatur: 203 °C

Die zuvor ermittelte tatsächliche relative dielektrische Permittivität des Dielektrikums ist  $\epsilon_r=3,1$ . Die Kondensatoren konnten erfolgreich realisiert werden. Dabei ergab sich eine Toleranz von ca.  $\pm 12\,\%$  in der Genauigkeit der Auslegung der Kapazitätswerte.

C. Realisierung einer einfachen elektrischen Baugruppe

Anhand einer einfachen elektrischen Baugruppe sollte der mögliche Mehrwert aufgezeigt werden, der durch den 3D-Druck elektronischer Systeme entstehen kann. In diesem Fall handelt es sich um ein beleuchtetes Namensschild (siehe Abbildung 9), das in seiner alten Version (Abbildung 9A) aus einer Leiterkarte, einer RGB-LED, einer Batterie mit Batteriehalter, einem Vorwiderstand, einer Zenerdiode und einem 3D-gedruckten Gehäuse sowie einer gelaserten Plexiglasplatte bestanden hat. Ziel war es nun, mit dem 3D-Design die ursprünglichen Abmessungen des Namensschilds nicht zu überschreiten, die Gehäuseform also beizubehalten und final bis auf die RGB-LED und eine Batterie keine weiteren elektronischen Komponenten für das Namensschild zu benötigen.

Abbildung 9B links zeigt das CAD-Modell des neuen Gehäuses. Abbildung 9B rechts zeigt das gedruckte 3D-Gehäuse, gedruckt aus leitendem PP-Filament sowie PLA-Filament. Es ist zu erkennen, dass die Batteriehalterung direkt in das Gehäuse integriert wurde. Ebenso die Leiterbahnen und Anschlüsse, an welche die RGB-LED angelötet werden kann. Bei dem Vorwiderstand handelte es sich bisher um einen  $33\,\Omega$ -Widerstand. Aufgrund des hohen spezifischen Widerstand der Filamente kann der Widerstand als einfache leitende Fläche im Gehäuse umgesetzt werden. Die Auslegung des integrierten Widerstandes wurde so vorgenommen, dass eine Zener-Diode nicht mehr notwendig war.

Abbildung 9C zeigt die neue Variante des beleuchteten Namensschildes, bei dem, gegenüber dem alten Design, die Komponenten Leiterkarte, Batteriehalter, Vorwiderstand und Zenerdiode eingespart werden konnten.

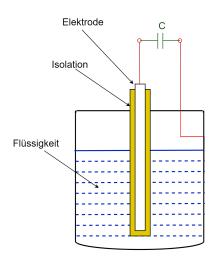

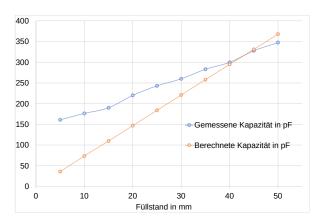

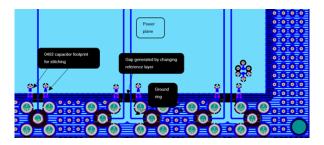

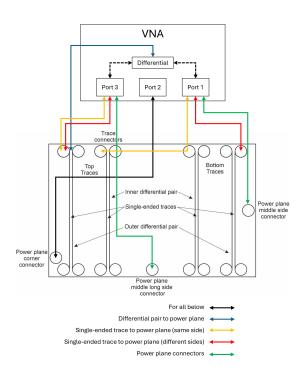

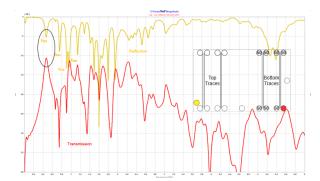

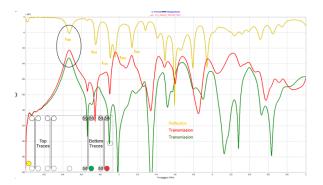

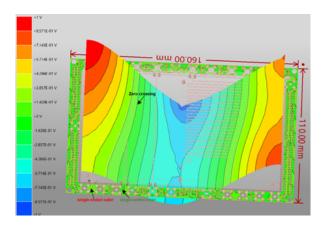

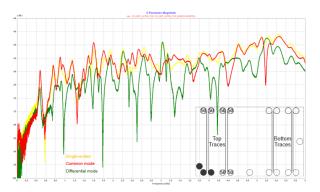

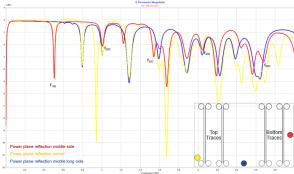

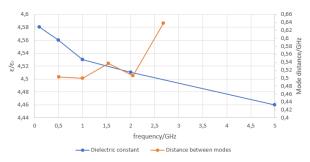

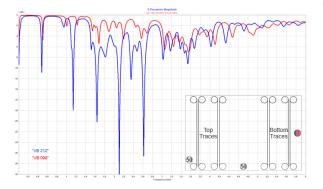

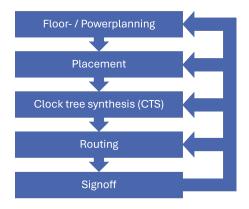

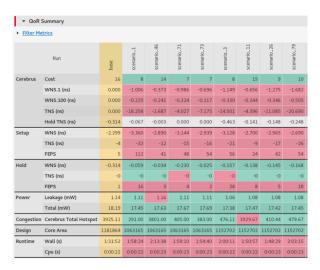

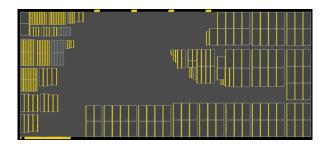

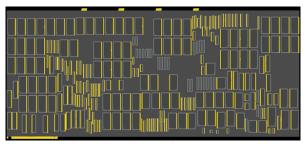

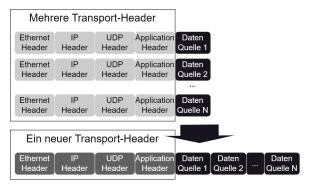

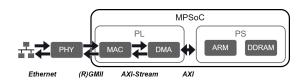

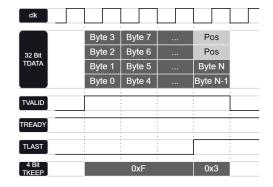

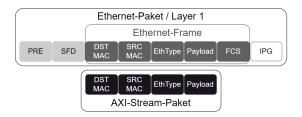

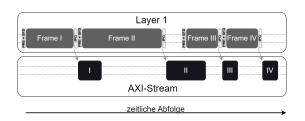

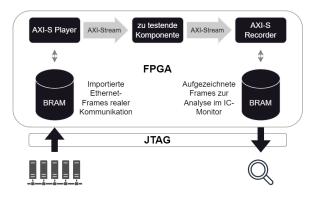

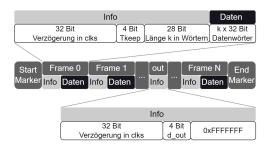

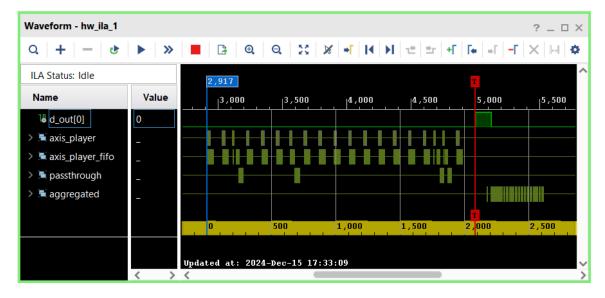

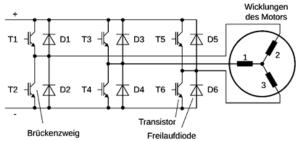

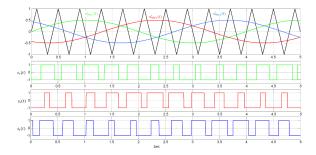

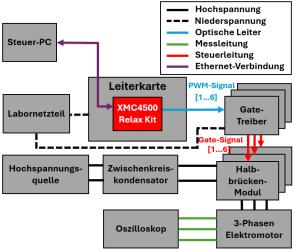

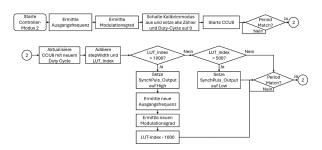

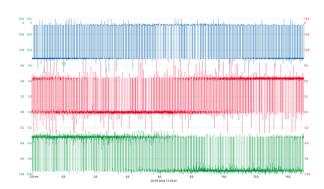

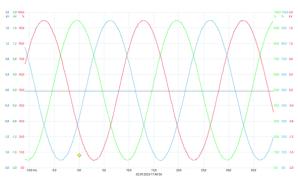

#### D. Realisierung eines kapazitiven Füllstandssensors