# MULTIPROJEKT CHIP-GRUPPE

BADEN-WURTTEMBERG

WORKSHOP JANUAR 1990

MANNHEIM

HERAUSGEBER: FACHHOCHSCHULE ULM

Das Werk und seine Teile sind urheberrechtlich geschützt. Jede Verwertung in anderen als den gesetzlich zugelassenen Fällen bedarf deshalb der vorherigen schriftlichen Einwilligung des Herausgebers.

### Vorwort

Für den Workshop WS 1989/1990 der Multiprojekt Chip-Gruppe konnten erneut Vertreter der Industrie gewonnen werden. Den Herren Dr. Killius vom Institut für Mikroelektronik Stuttgart und Dr. Glauert von der Robert Bosch GmbH sei an dieser Stelle nochmals für ihre interessanten Beiträge gedankt.

Neben den Fachvorträgen wurde als weiterer Schwerpunkt die Problematik der Ausbildung im IC-Entwurf behandelt. Diese Thematik ist gegenwärtig besonders aktuell, da mit der jetzt allen FHs zur Verfügung stehenden Hard-und Software möglichst bald eine effektive Ausbildung auf dem Gebiet des Entwurfs Integrierter Schaltungen zu erreichen ist.

Ulm, Januar 1990

Prof. Führer Fachhochschule Ulm

### INHALTSVERZEICHNIS

Vorwort

A. Führer FH Ulm

- 1. ASICs : Historische Entwicklung u. Wirtschaftlichkeit

- P. Killius Institut für Mikroelektronik Stuttgart

- 2. Programm zur Berechnung des zeit- u. frequenzabhängigen Sperrschichttemperaturverlaufs von Leistungshalbleitern mit Kühlkörpermontage

- R. Rudloff FH Aalen

- Entwurf eines Uhren-IC als Vollkunden-Schaltkreis mit Zeitzeichen-Empfänger

- R. Lieder, G. Kampe, A. Volk FHT Esslingen

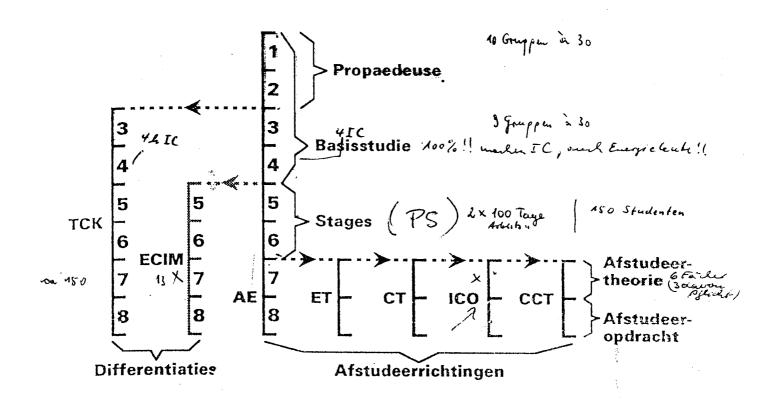

- 4. Lehre des Entwurfs Integrierter Schaltungen

- K. Schmidt

FH Furtwangen

- 5. Ausbildung im IC-Entwurf Blick in den FH-Bereich in Holland

- K. Schmidt

FH Furtwangen

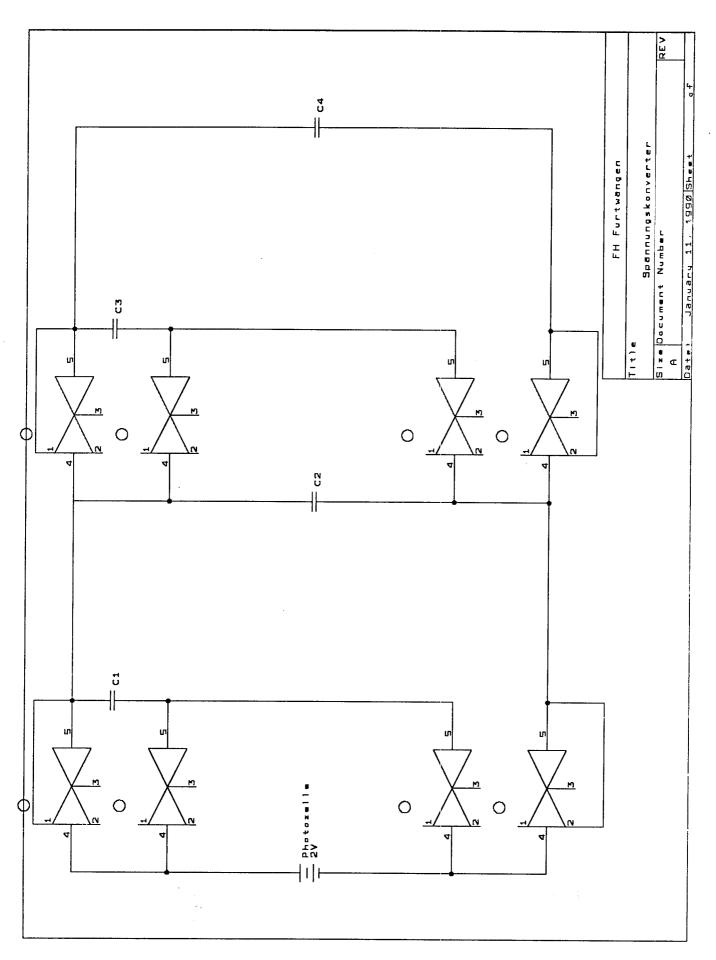

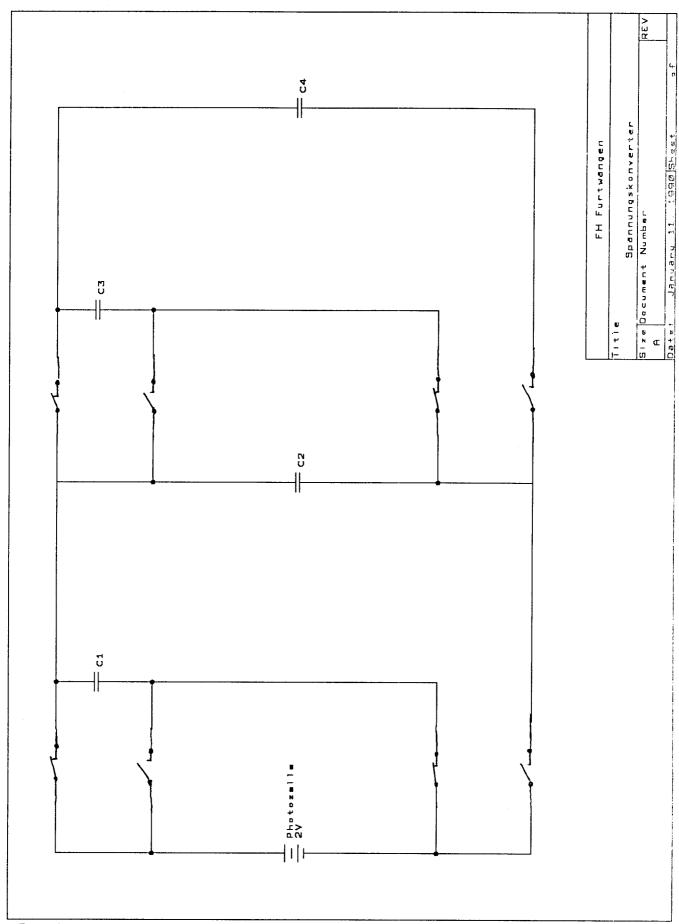

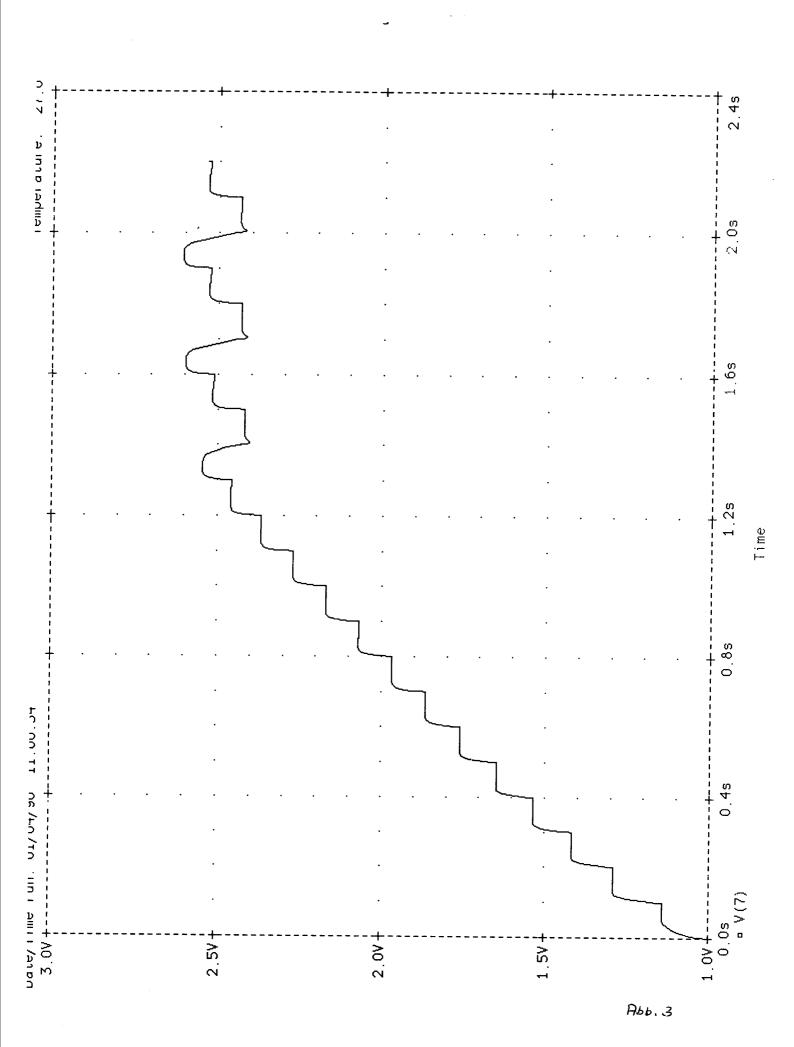

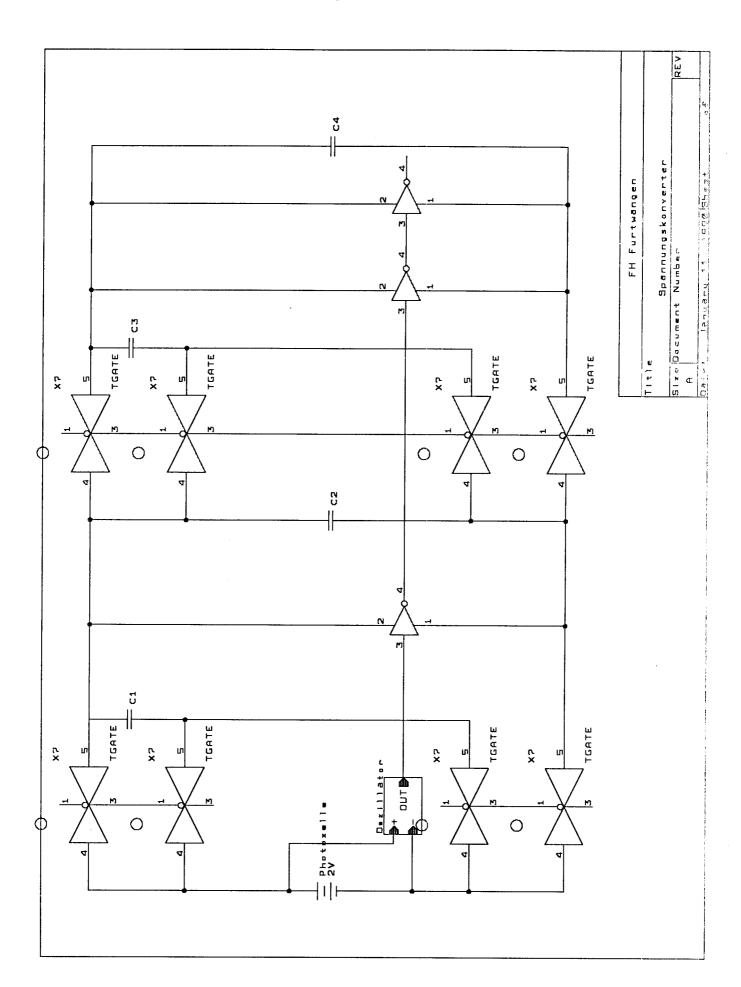

- 6. Design u. Layout eines 2 auf 6 Volt Spannungskonverters

- W. Zerweck FH Furtwangen

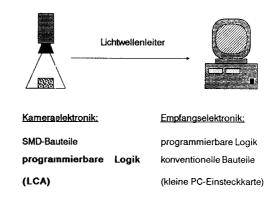

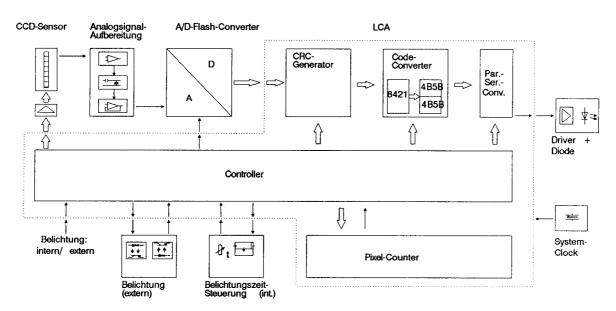

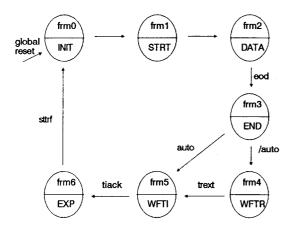

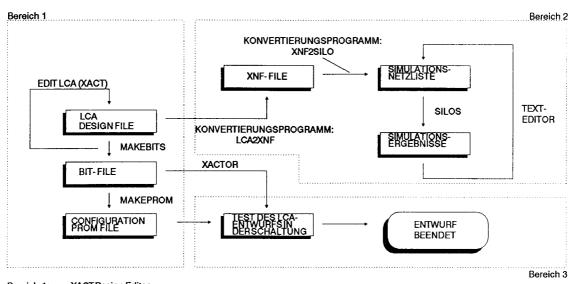

- 7. Entwurf eines Logic-Cell Arrays (LCA) für eine Lichtwellenleiterübertragungsstrecke von einer CCD-Kamera zu einem Personal-Computer

- B. Reinke

FH Offenburg

- 8. DECUS-Software

- G. Albert FHT Mannheim

### **VORTRAG**

"ASICs: Historische Entwicklung und Wirtschaftlichkeit"

Mannheim, 12.01.1990

Dr. Peter Killius, Institut für Mikroelektronik Stuttgart

Dr. Peter Killius hat an der TU Berlin Physik mit der Ausrichtung experimentelle Festkörperphysik studiert. Nach einer Tätigkeit bei IBM in Schönaich und Sindelfingen folgten 3 Jahre als wissenschaftlicher Mitarbeiter am Institut für Mineralogie-und Kristallchemie der Uni Stuttgart, die er mit der Promotion abschloß. 1972 trat er in das Forschungszentrum der SEL in Stuttgart ein, wurde dort Leiter der MOS-Gruppe und später Leiter des Labors für hochintegrierte Kundenschaltungen. Auf Tagungen wie der Electronica/ Productronica sowie an der Technischen Akademie Esslingen hielt er Vorträge über Schaltungstechnik und Mikroelektronik. In diese Zeit fielen auch die ersten Kontakte zu Prof. Höfflinger an seinem damaligen Dortmunder Lehrstuhl. 1984 wurde er Geschäftsführer/Direktor der Dectroswiss Electronic Design AG in der Schweiz. Seit dem 15.1.1989 ist er Leiter des Bereichs Design und Test am IMS und zusätzlich mit Marketingaufgaben und der Abwicklung unserer ASIC-Projekte betraut.

### 1. EINLEITUNG

Technologische Eckdaten

1948 : Transistor (bipolar, Ge)

1959 : Si-Planartechnik

1969 : Erste Standardzellen (ohne SW)

1970 : Mikroprozessor

1972 : 1 K RAM

1976 : MEAD - CONWAY (Lambda-Regeln)

1985 : ASIC - Durchbruch

1990 : 16 M RAM (Muster)

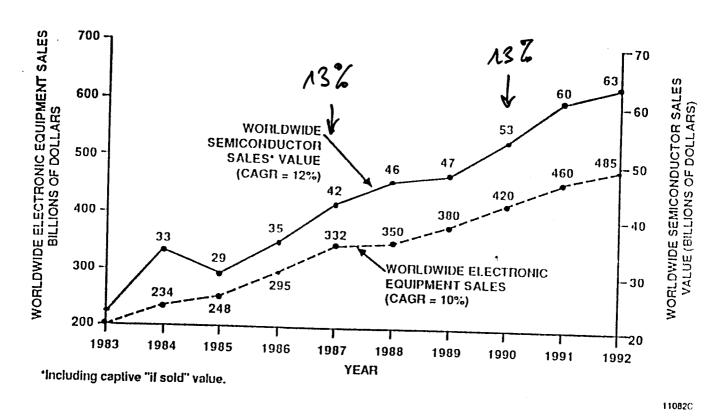

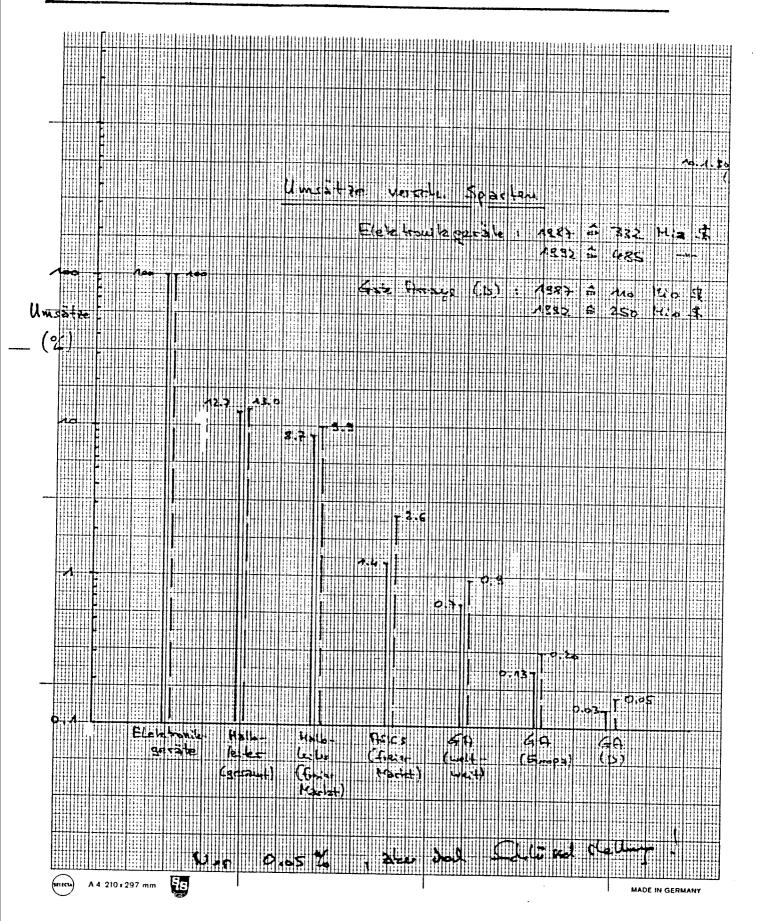

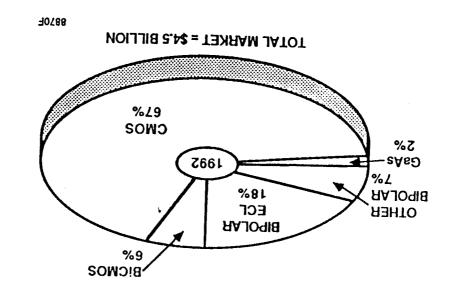

Umsätze (1990) weltweit

- Elektronikgeräte: 400 Mrd \$

- Halbleiter (≙ 13%): 50 Mrd \$

### 2. HISTORISCHE ENTWICKLUNG

### 2.1 Technologie

- Germanium: Betriebstemperatur zu niedrig

- Si-Planartechnologie erlaubte Integration (physikalischer Glücksfall: Si -> Si Operation Isolator) und revolutionierte Schaltungstechnik (ein einziges BE)

- zunächst PMOS

- dann NMOS

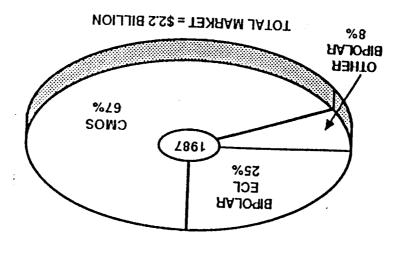

- schließlich CMOS-Technologie wegen sehr kleiner Verlustleistung führend

- Bipolartechnologie zunächst wesentlich schneller, aber deutlich kleinerer Integrationsgrad und vor allem höhere Verlustleistung;

- MOS-Skalierung w/l, Sättigungsstrom = konst.

- Bipolar-Skalierung Tr.Fläche, Sättigungsstrom Fläche

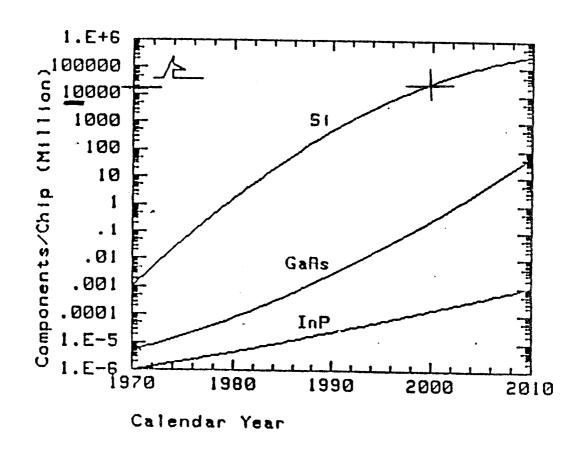

- GaAs sehr schnell (aber nicht mehr wesentlich schneller als Si), <u>aber</u> keine hohe Komplexität, Prozeß teuer und vor allem keine gute Störsicherheit

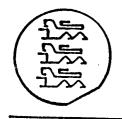

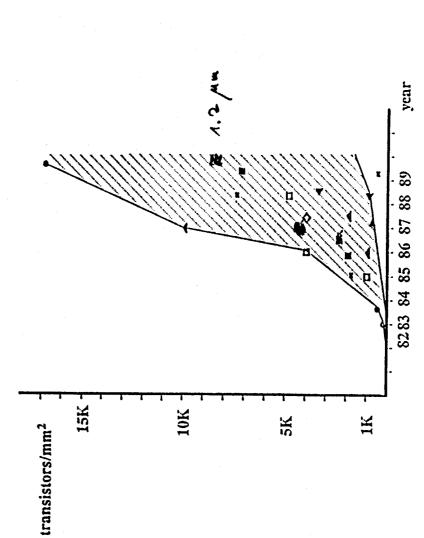

MEMOPY INCREASE = 1.5/YEAR MPU MCREASE = 1.35 YEAR

Source: Intel 11745

Figure 5-27. IC Density Trends

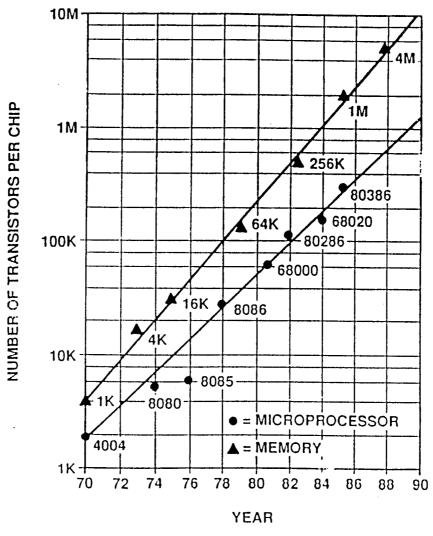

MEMORY INCREASE = 1.13/YEAR

MPU INCREASE = 1.13/YEAR

Source: Intel

11746

Flgure 4-14. IC Die Size Trends

### HARDWARE / SOFTWARE

### Bis Ende 60er Jahre

- Im wesentlichen SSI-Schaltungen

- fast nur Vollkundenschaltungen, jeder Transistor noch einzeln berechnet (Rechenschieber)

- allererste Simulatoren

- erste Bibliotheken (FAIRCHILD), die jedoch mangels geeigneter Software nicht zum Tragen kommen

- physikalische Realisierung durch "Konstruktions"-Mentalität

- IC's waren teuer und ein Abenteuer zugleich, d.h. viele Redesigns

### CAD DIGITIZER

(1980)

11743 ©1984 TORRIC CORPORATION

FIGURE 3-8

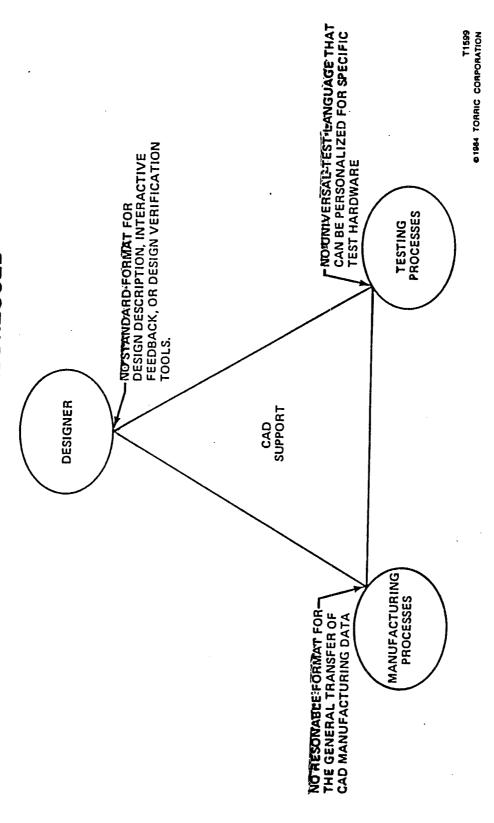

# THE THREE NARROW INTERFACES THAT ARE POORLY ADDRESSED

FIGURE 4-9

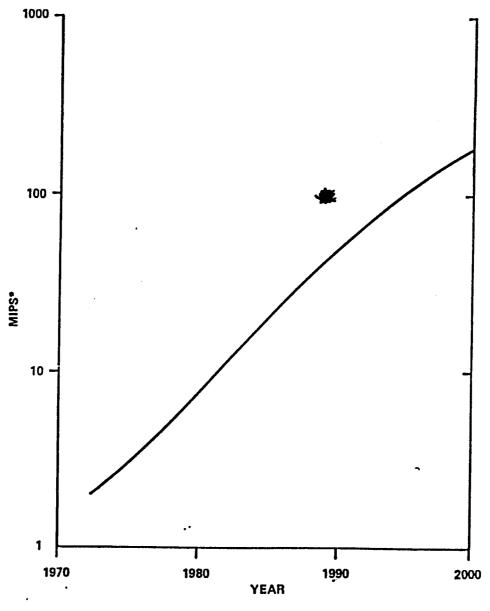

### GROWTH OF MAXIMUM PROCESSING POWER

•(MILLIONS OF INSTRUCTIONS PERFORMED PER SECOND)

After Keyes FIGURE 2-74

T1554

-FIGURE 2-75

### HARDWARE / SOFTWARE

### Bis Ende der 70er Jahre

- Dekade der "Mikrorechner", d.h. Software-Euphorie ("Universalität")

- als Rechner dienten weitgehend "mainframes" (IBM, 10 MIPS) und PRIME

- Design-Möglichkeiten der Technologie weit voraus; Simulationen setzen sich auf breiter Front durch

- falls Hardwarelösung, Vollkundenschaltungen dominierend; nur IBM nutzt früh "Gate-Arrays"

- wegen kompatibler Technologien sind Bibliotheken amortisierbar ("multi sourcing")

- Design durch spezialisierte Firmen (z.B. AMI) bzw. Geschäftsbereiche oder Designzentren von Großfirmen

- Designer waren so etwas wie "Künstler" mit viel Technologie-Hintergrund

- übliche Schnittstelle: Spezifikation (besser Pflichtenheft)

### HARDWARE / SOFTWARE

### 1. Hälfte der 80er Jahre

- Rückbesinnung auf Hardware-Lösungen

- Mikrorechner oft zu langsam

- Softwareaufwand "explodiert"

- Kopierschutz

- große Halbleiterhersteller entdecken den ASIC-Markt und steigen massiv ein in Entwicklungswerkzeuge (Kunden = Designer)

- Mini-Rechner (DEC, 1 MIPS) erscheinen und lassen sich vernetzen

- Design-System aufgebaut aus Einzelprogrammen

- Industrie für ASIC-Software und entsprechender Fertigung entsteht (LSI Logic, VTI), mit Schnittstelle "simulierte Netzliste"

- NMOS-Technologie löst PMOS ab

### HARDWARE / SOFTWARE

### 2. Hälfte 80er Jahre

- Workstations (0.3 MIPS) mit "geschlossenenem Designsystem" werden einsatzfähig (DAISY), ebenso erste Si-Compiler

- "formalisierte" Design-Methoden setzen sich auf breiter Front durch (Gate-Arrays)

- billige und bedienungsfreundliche Design-Werkzeuge erlauben dezentrale ASIC-Aktivitäten (Lernkurven)

- Optimierungsdruck bei Si verschwindet (Kostenverschiebung Si -> Design)

- Preiszusammenbruch bei Design-Leistungen wegen Kampf um Marktanteile

- CMOS wird die ASIC-Technologie

- starke Fusionswelle spez. bei SW-Häusern

- standardisierte Datenschnittstellen setzen sich durch (VHDL, EDIF)

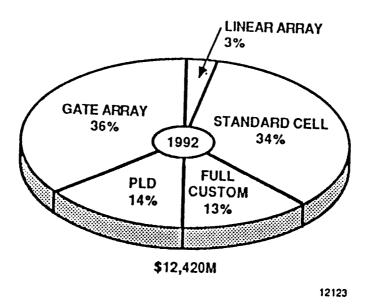

Figure 1-4. Electronic Equipment Sales and Semiconductor Sales Trends (1983 - 1992)

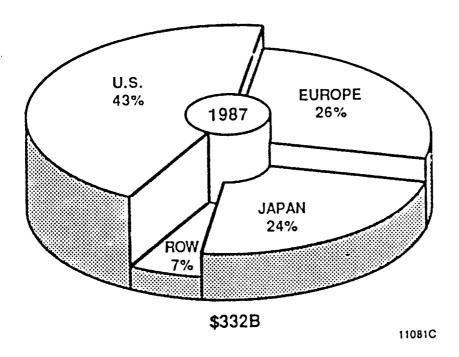

Figure 1-5. Electronic Equipment Production

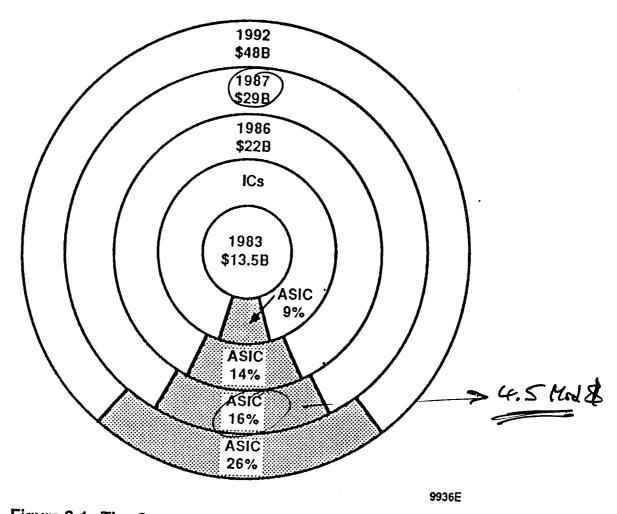

Figure 6-1. The Growing Worldwide Merchant ASIC Market

\*Does not include IBM and DEC.

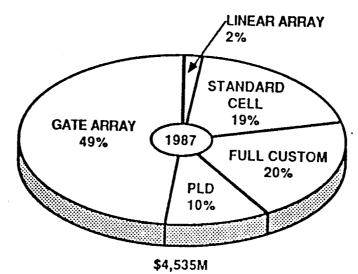

Figure 6-2. Worldwide ASIC Production\*

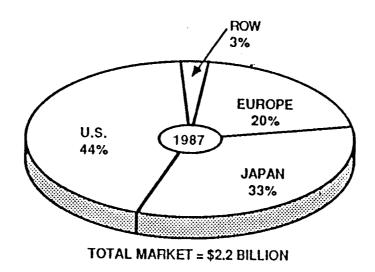

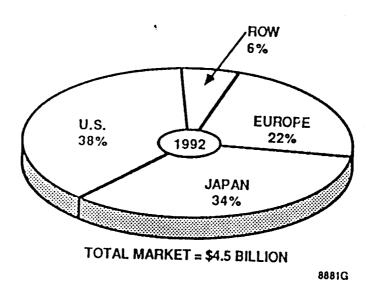

Figure 6-6. Worldwide Gate Array Market by Geographical Sector

| Rang    | Firmenname        |            | 1987 |       | 1988    |      |       |  |

|---------|-------------------|------------|------|-------|---------|------|-------|--|

|         |                   | BIPOLAR    | MOS  | TOTAL | BIPOLAR | MOS  | TOTAL |  |

| 88      | FUJITSU           | 240        | 150  | 390   | 290     | 235  | 525   |  |

| (2)     | NEC               | 84         | 185  | 269   | 110     | 250  | 360   |  |

| 3       | LSI LOGIC         |            | 250  | 250   | _       | 350  | 350   |  |

| 3       | TOSHIBA           | _          | 200  | 200   | -       | 260  | 260   |  |

| 5       | MOTOROLA          | 95         | 8    | 103   | 115     | 15   | 130   |  |

| 6       | HONEYWELL         | 33         | 67   | 100   | 40      | 80   | 120   |  |

| 7       | PLESSEY/FERRANTI  | 65         | 15   | 80    | 75      | 25   | 100   |  |

| 8       | HITACHI           | 30         | 36   | 66    | 40      | 60   | 100   |  |

| 9       | AT&T              | 60         | -    | 60    | 60      | -    | 60    |  |

| மி      | SEIKO-EPSON       | -          | 47   | 47    | -       | 60   | 60    |  |

| 11      | SIEMENS           | 40         | 1    | 41    | 40      | 3    | 43    |  |

| 6       | MATSUSHITA        | · <b>-</b> | 40   | 40    | -       | 80   | 80    |  |

| 13      | NATIONAL SEMIC.   | _          | 38   | 38    |         | 48   | 48    |  |

| 14      | MARCONI           |            | 30   | 30    |         | 32   | 32    |  |

| 15      | GOULD             | _          | 30   | 30    | _       | 35   | 35    |  |

| 6       | OKI               |            | 30   | 30    |         | 45   | 45    |  |

| 17      | VLSI TECHNOLOGY   |            | 27   | 27    |         | 4,0  | 40    |  |

| 18      | GE SOLID STATE    | -          | 26   | 26    | -       | 25   | 35    |  |

| (9)     | MITSUBISHI        | -          | 25   | 25    | _       | 40   | 40    |  |

| 20      | AMCC              | 24         | -    | 24    | 27      |      | 27    |  |

| 21      | TEXAS INSTRUMENTS | 6          | 9    | 15    | 9       | 13   | 22    |  |

| 22      | RICOH             | -          | 15   | 15    |         | 25   | 25    |  |

| 23      | SGS-THOMSON       |            | 14   | 14    | -       | 25   | 25    |  |

| 24      | SIGNETICS         | 12         | -    | 12    | 15      | e-um | 15    |  |

| ?5      | CDI               | -          | . 11 | 11    |         | 18   | 18    |  |

| 26      | IMI               | -          | 10   | 10    |         | 12   | 12    |  |

| TOTAL   |                   | 689        | 1264 | 1953  | 821     | 1786 | 2607  |  |

| Andere  |                   | 13         | 84   | 97    | 44      | 119  | 163   |  |

| TOTAL . |                   | 702        | 1348 | 2050  | 865     | 1905 | 2770  |  |

Die größten Gate-Arrav-Hersteller mit ihren Umsatzzahlen (in Millionen Dollar)

Quelle: ICE

Table 1

Estimated Worldwide Gate Array

Design Starts

| •                          | Design Starts |        |        |        | lay U  |        |        |        |

|----------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|

|                            | 1985          | 1986   | 1987   | 1988   | 1989   | 1990   | 1991   | 1992   |

| Total Design Starts        | 8,795         | 10,377 | 11,603 | 13,668 | 15,837 | 17.614 | 20,621 | 24,040 |

| MOS ·                      | 6,096         | 7,776  | 8,815  | 10,631 | 12,638 | 14,298 | 17,006 | 20,065 |

| Bipolar                    | 2,699         | 2,601  | 2,788  | 3,037  | 3,199  | 3,316  | 3,614  | 3,975  |

| Merchant Design Starts     | 6,341         | 7,559  | 8,573  | 10,242 | 12,011 | 13,482 | 15,936 | 18,748 |

| HOS                        | 4,560         | 5,894  | 6,761  | 8,249  | 9,896  | 11,284 | 13,541 | 16,114 |

| Bipolar                    | 1,781         | 1,665  | 1,612  | 1,993  | 2,113  | 2,198  | 2,395  | 2,634  |

| Intracompany Design Starts | 2,454         | 2,818  | 3,030  | 3,427  | 3,826  | 4,132  | 4,685  | 5,292  |

| HOS                        | 1,536         | 1,882  | 2,054  | 2,383  | 2,740  | 3,014  | 3,466  | 3,951  |

| Bipolar                    | 918           | 936    | 976    | 1,044  | 1,086  | 1,118  | 1,219  | 1,341  |

Source: Dataquest July 1988

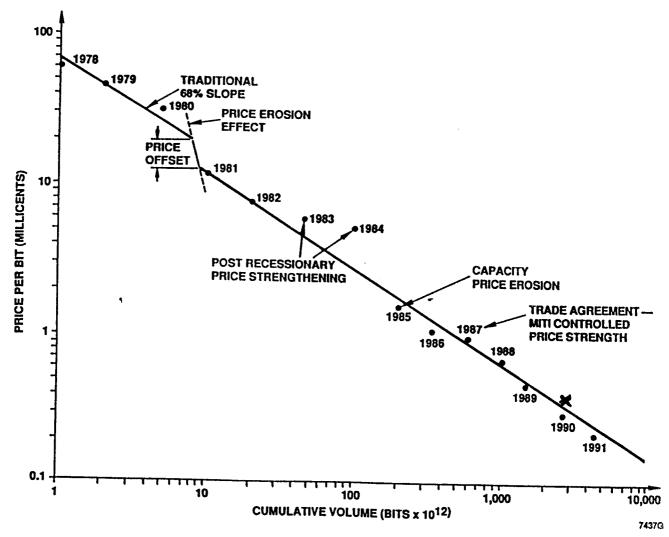

Figure 7-53. Price Curve for MOS Dynamic RAM

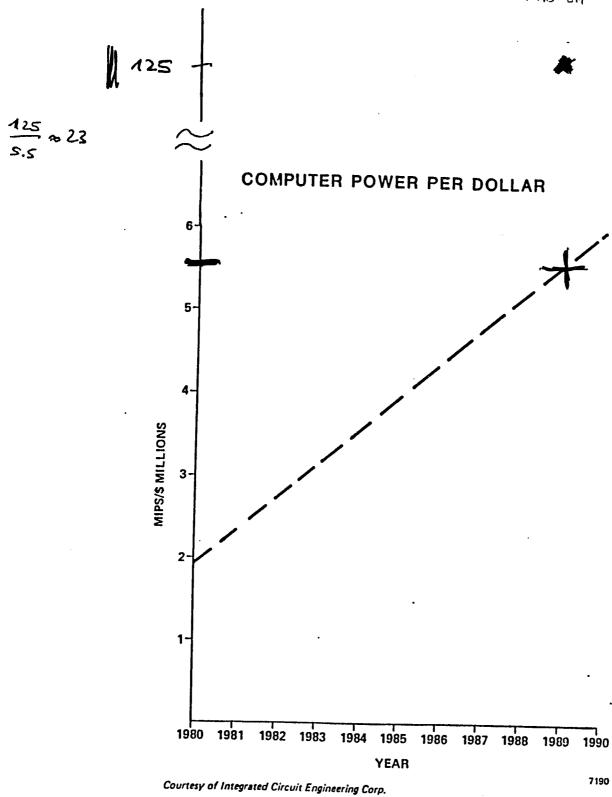

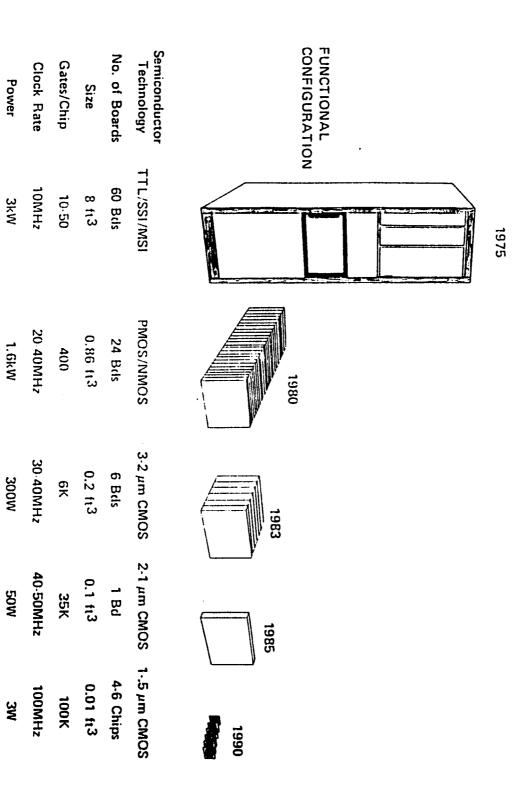

# SEMICONDUCTOR TECHNOLOGY IMPACT AT SYSTEMS LEVEL

Courtesy of Integrated Circuit Engineering Corp.

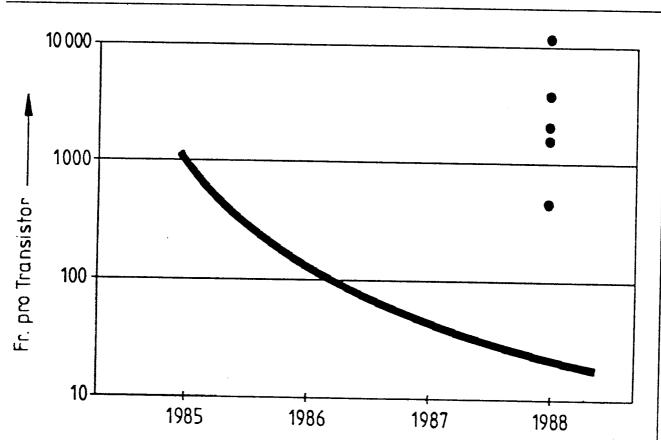

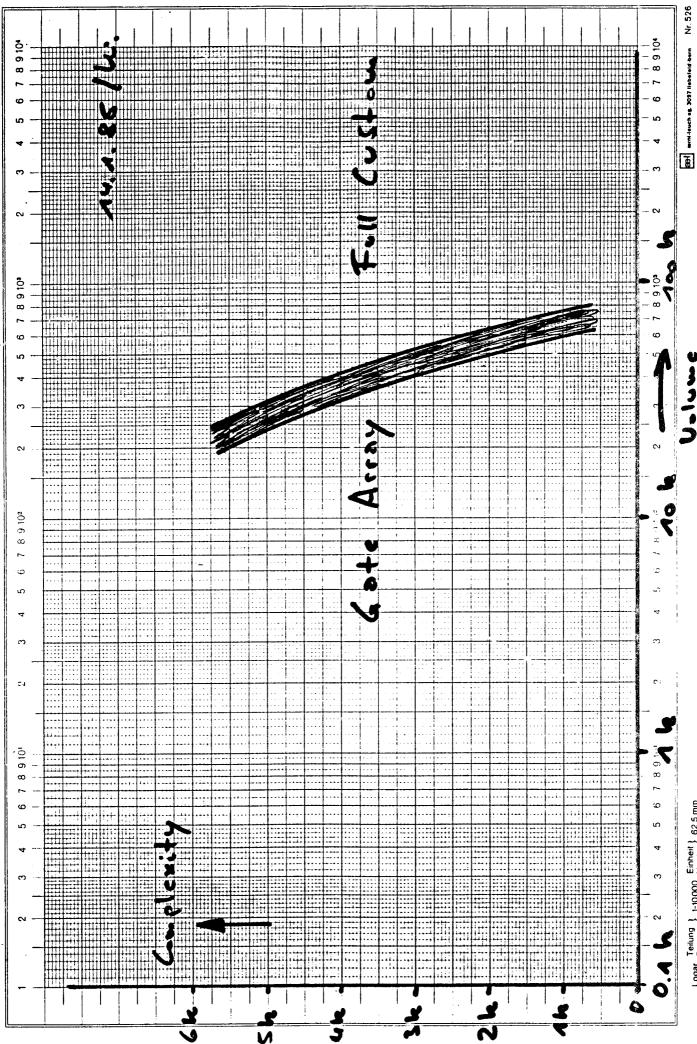

Bild 1. "Lernkurve" bei Dectroswiss (durchgezogene Linie): Durch stetige Verbesserung der Effektivität und Produktivität rd im 4.Jahr das unter Profis übliche Kostenniveau erreicht (für Prototypen, in sFr. je Transistor für gemischt digital/analoge Schaltungen, mit typisch 10 000 Transistoren Komplexität); Größe des ASIC-Zentrums: 20 Mitarbeiter. Die Punkte geben Momentaufnahmen singulärer ASIC-Aktivitäten (2–5 Mitarb./Gruppe) eines Großkonzerns wieder: Zusätzlich zu den höheren Kosten je Transistor dürfte auch die Lernkurve wegen des geringeren Spezialisierungsgrades und nur "Teilzeit-ASIC-Einsatzes" deutlich flacher verlaufen

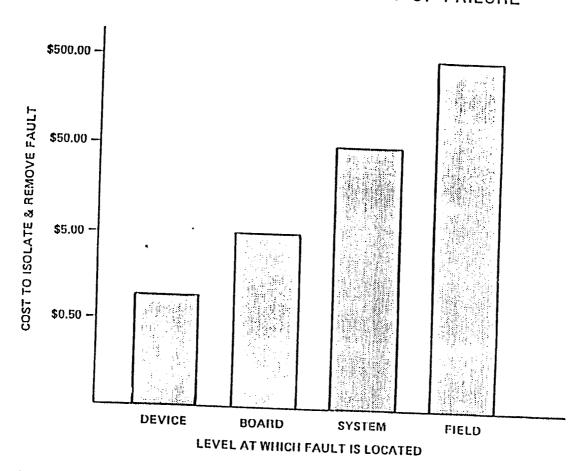

### REPAIR COSTS RELATED TO POINT OF FAILURE

Courtesy of Integrated Circuit Engineering Corp.

7052

FIGURE 2-71

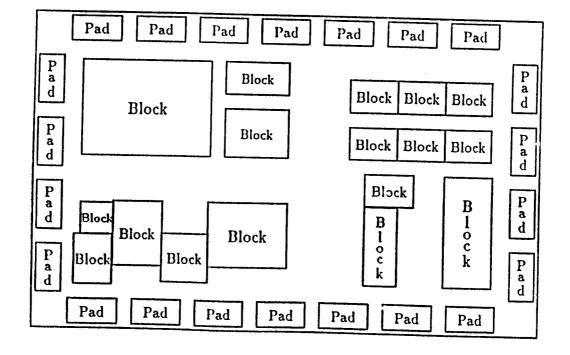

### DESIGN OF CUSTOM ICS

### • DESIGN METHODOLOGIES

### Gate Array

Fixed chip size

Fixed cell count

Fixed basic cell

Fixed routing ch.

Fixed pin count

### Standard Cells

variable chip size

variable cell count

fixed cell height

variable routing ch.

variable pin count

variable cell width

Full Custom (man. layout)

variable chip size

variable cell count

variable cell size

variable routing channel

variable pin count

$\frac{\text{Fig. l}:}{\text{Designed Integrated Circuits}}$

Réference : Journées d'Electronique et de Microtechnique, Lausanne, 1984.

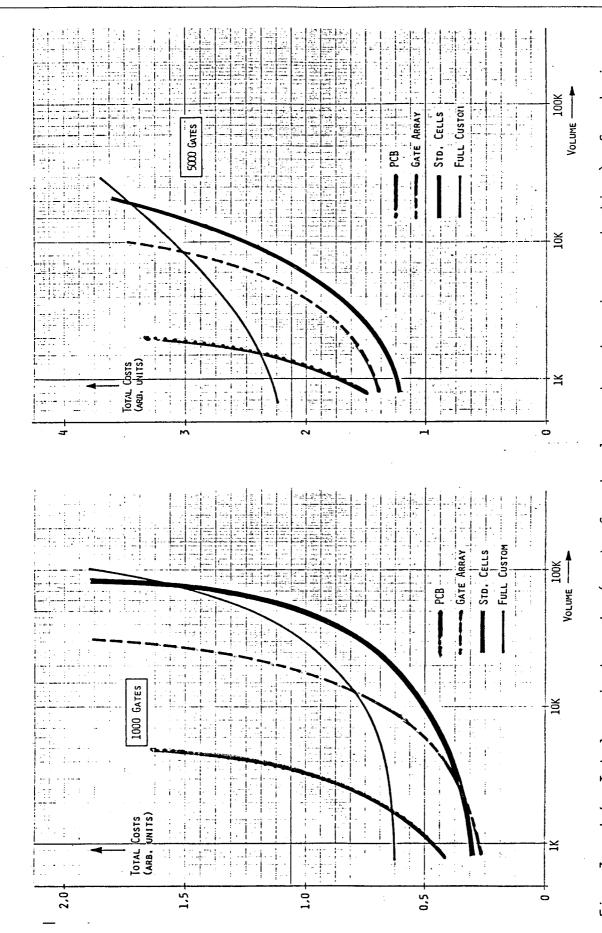

Vollkundenschaltung

a function of volume. 150 and 650 development costs resp., 300 and 1200 volume Total project costs (costs for development and series production) of a device with 1000 and 5000 gates resp. as Assumptions used for PCB solution: and 4:

Réference : Journées d'Electronique et de Microtechnique, Lausanne, 1984.

Logar Teitung } 1-10000 Einheit } 62.5 mm

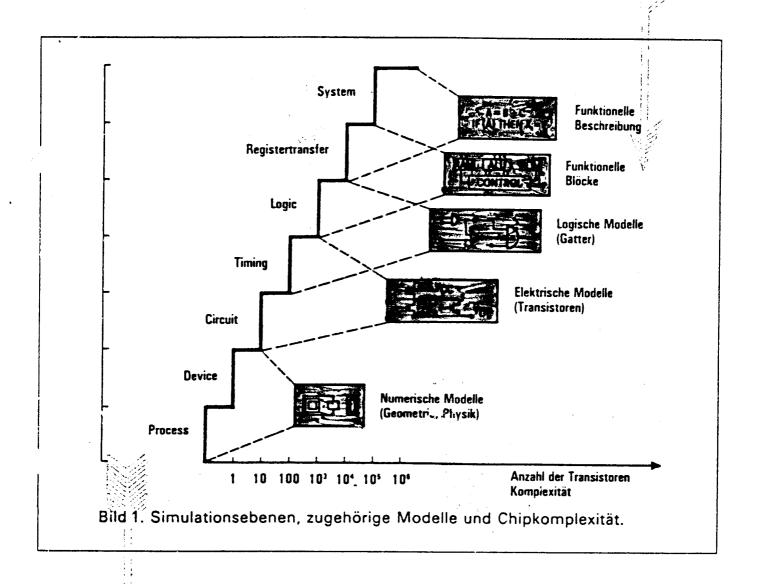

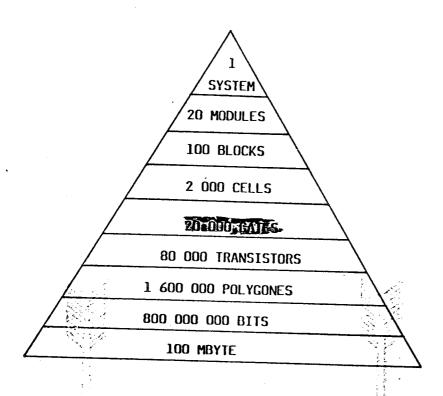

#### INTRODUCTION: LEVELS OF HIERARCHY

Source: H. Rüchardt, NTG-Fachbericht 86 VDE Verlag 1984

#### INTRODUCTION

#### SUPPORT BY COMPUTER

Number of units per level or hierarchy

These amounts of data cannot be handled furthermore "manually"

# **Gate Forest**

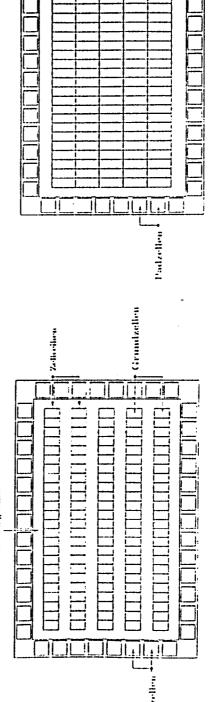

# 1.1 Semi-Custom Arrays

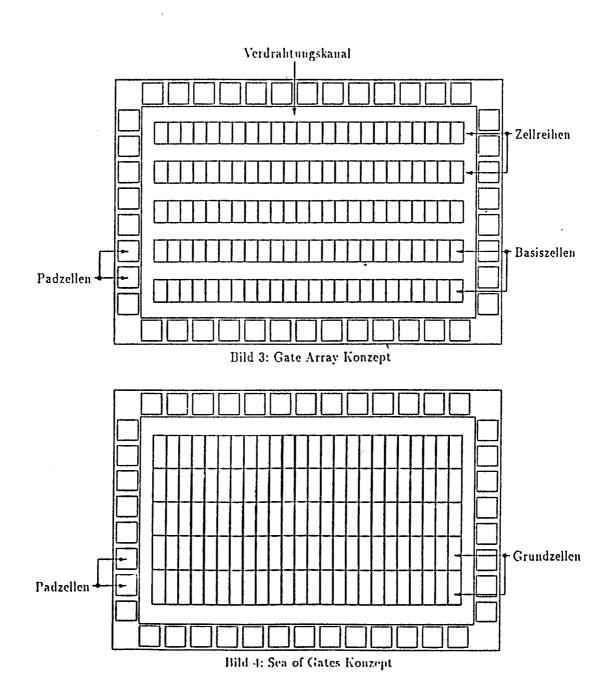

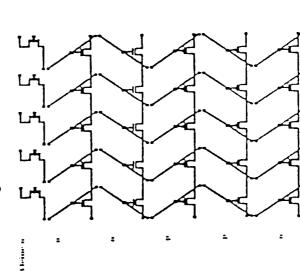

## Gate Array

Grundzellen mit 2-4 Transistoren Zellreihen wechseln sich mit Verdrahtungskanälen ab

# Sea of Gates

Regelmäßige Anordnung der Grundzellen keine expliziten Verdrahtungskanäle

# Conventional Array

C. Y. LSI LOGIC CORPORATION

# 1.2 Aufbau des Gate Forest **Gate Forest**

Anordnung der Grundzellen (Makroarchitektur): Gate Isolation und geometrische Isolation

Technologie

: 2µm zwei Metallagen P-Wannen CMOS

mehrere Array-Größen : bis zu 280 000 Transistoren Array Dichte : 2050 Transistoren/mm²

**Array Dichte**

Gate Forest Grundzelle (Mikroarchitektur):

1 P-Kanal Transistor (W = 14 µm)

2 N-Kanal Transistoren (W = 9 μm)

1 N-Kanal Transistor (W = 4 µm)

Verhältnis P:N = 1:3

45° -Orientierung der Poly-Gates

# Second Generation Semi-Custom Arrays

Hughes

Sperry

VLSI Technology

Motorola

Fujitsu

= Mitsubishi= Hitachi

SWI = MS

= Toshiba

n = LSI Logic Inc.

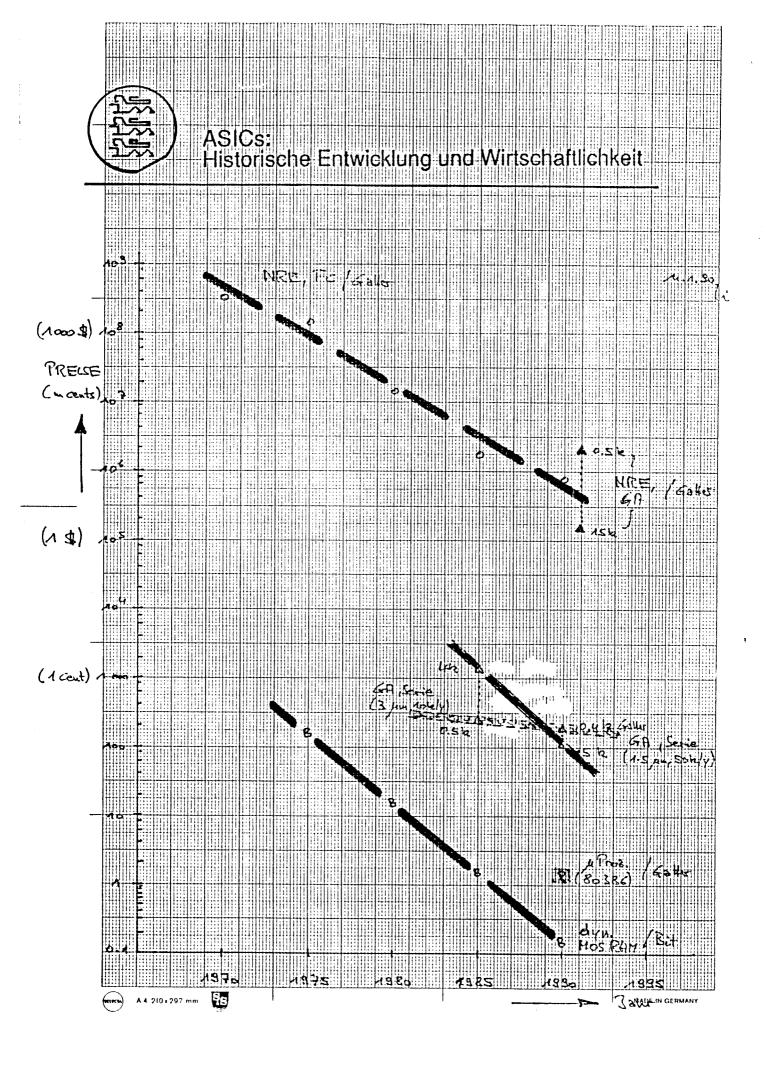

## ASICs: Historische Entwicklung und Wirtschaftlichkeit

| Variante                          | Nutzbare Chipgröße<br>in mm<br>(gerundet)          | Nutzfläche<br>in mm <sup>2</sup><br>(gerundet) | Transistor-<br>anzahl<br>x10 <sup>3</sup> | Padanzahi<br>(I/O)     | 2-Input NAND Gate Äquivalent x10 <sup>3</sup> |

|-----------------------------------|----------------------------------------------------|------------------------------------------------|-------------------------------------------|------------------------|-----------------------------------------------|

| GFXX1<br>GFXX2<br>GFXX4<br>GFXX9S | 13,3 x 13,3<br>9,6 x 8,8<br>6,7 x 6,6<br>4,3 x 4,3 | 177<br>84<br>44<br>18                          | 284<br>119<br>53<br>16                    | 220<br>134<br>96<br>56 | 28,4<br>12,0<br>5,3                           |

### Design and Analysis of Semi-Custom Architectures

Michiel A. Beunder Institute for Microelectronics Stuttgart West-Germany

#### IMS VLSI High-ASIC-Strategie

#### 1. CMOS Semicustoum

Logik sowie frei-formatierte PLA's und Speicher (ROM, Multi-Port RAM, CAM) auf dem gleichen Chip

- 2. Personalisieren durch schnelles direktes Elektronenstrahlschreiben auf dem Wafer

- 3. Komplette Technologie für 0,5 um Gates und 3 um Metall-Pitch

- 4. Offenes Design-Interface, vorzugsweise für Logik- und Symbol-Ebene

- 5. Kooperationsprojekt mit potenten Anwendern

==== : 10<sup>5</sup> Gatter/Chip

:5·10<sup>4</sup> Gatter/Chip

(ohne Gehäuse)

Das dreiteitige Mittelstandsprogramm des Instituts für Mikroelektronik Stuttgart wurde 1988 erfolgreich implementiert. Neben dem Beratungsprogramm und bilateralen Projekten mit mittelständischen Unternehmen wurden drei mögliche Schwerpunktprogramme in mehreren Workshops, an denen über 20 Firmen teilnahmen, definiert.

Zwei Programme konnten gestartet werden, indem Entwicklungsziele, die Partnerschaft und die finanzielle Beteiligung mit jeweils vier Firmen vertraglich vereinbart wurden.

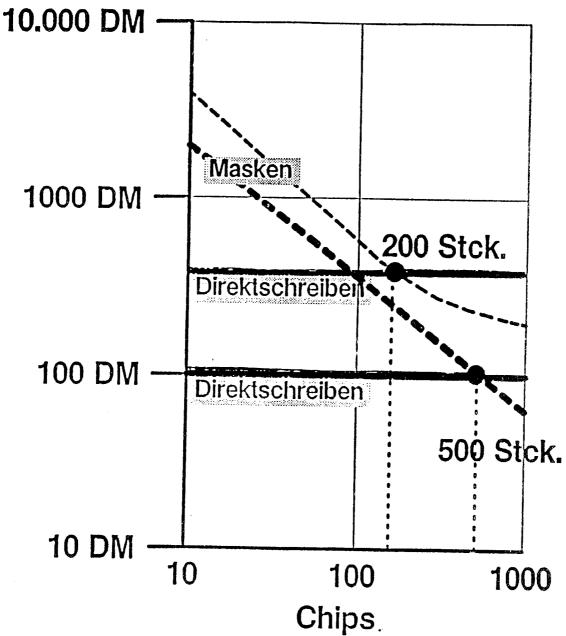

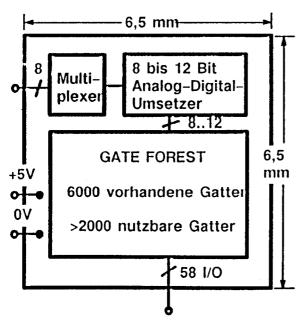

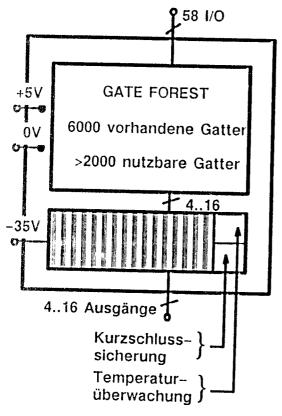

Das eine Programm betrifft einen personalisierbaren Analog/Digital-Umsetzer, der auf einem Chip mit über 2.000 nutzbaren Gattern CMOS-Logik in einem Standard-CMOS-Prozess integriert ist. Abbildung I zeigt ein Blockdiagramm dieses Chips. Das Chip soll mehrere Analog-Signale je nach Anwendung mit 8- bis 12-bit Genauigkeit digital umsetzen und soviel digitale Logik bieten, daß, wiederum je nach Anwendung, einfache Signalverarbeitungsaufgaben, Controller-Funktionen oder Schnittstellen zu verschiedenen Datenbussen implementiert werden können.

Abb. 1: Blockdiagramm eines Chips, mit dem bis zu acht Analog-Signale in Digital-Signale mit 8...12bit Genauigkeit umgesetzt werden und für die digitale Weiterverarbeitung 6.000 Gatterplätze zur Verfügung stehen. Mit der Personalisierung der Gatterfunktionen wird zugleich der Multiplexer und der Analog/Digital-Umsetzer für die spezifische Anwendung personalisiert.

Dabei sollen für die jeweilige spezifische Anwendung des Chips die Entwicklungs-, Werkzeug- sowie Herstellkosten und Zeit minimiert werden. Es wird eine Semicustom-Lösung erarbeitet, deren Features allen Entwicklungspartnern und anderen Anwendern gleichermaßen nützt, und die schnell sowie kostengünstig für den einzelnen Anwender spezifisch und unter Schutz seines Know-Hows personalisiert werden kann.

Der Chip-Master enthält einen auf einen industriellen Standard-CMOS-Prozess schnittenen und mit 5V betriebenen genauen Digital/Analog-Umsetzer sowie einen GATE FOREST mit 35.000 Transistoren, die 6.000 Gatteräquivalenten entsprechen. Die Chips werden auf Scheiben in großen Losen zu 80% einheitlich vorgefertigt. Die Personalisierung findet dann in vier spezifisch hergestellten Ebenen (2 Kontaktloch- und 2 Metallisierungsebenen) statt. Für diese Personalisierung wird das am Institut schnelle Direktschreiben von Strukturen mit dem Elektronenstrahl eingesetzt. Damit können auch kleinste Stückzahlen wirtschaftlich und schnell hergestellt werden.

Die Entwicklungspartner bei diesem Projekt sind Boehringer (Mannheim), Hellige (Freiburg), IKA Analysentechnik (Heitersheim), LTG Lufttechnische Gesellschaft (Stuttgart).

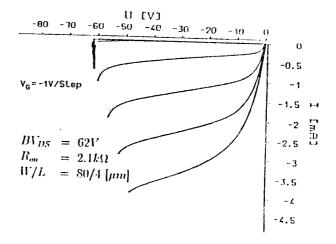

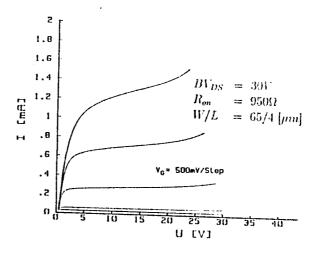

Wie das erste Projekt, reflektiert auch das zweite typische Problemstellungen in der Industrieelektronik. Während das erste zeigt, daß man in der Industrieelektronik immer irgendwie von analogen Eingangssignalen auszugehen hat, zeigt das zweite, daß die Digital-Technik ausgangsseitig häufig Signalhübe von 24-40V und höhere Ströme anbieten muß, als die 5V-Digital-Technik normalerweise bietet. Durch entsprechende Vorarbeiten hatte das Institut gezeigt, daß mit einem industriellen Standard-5V-CMOS-Prozess 60V Transistoren ohne eine Technologieänderung hergestellt werden können (s. Abb. 2b)

Auf dieser Grundlage wurde mit einer weiteren Firmengruppe ein Chip spezifiziert, dessen Blockdiagramm in Abbildung 2a wiedergegeben ist. Wiederum handelt es sich um ein Master-Konzept mit über 35.000 GATE FOREST Transistoren, wobei nun auf dem gleichen Chip 16 Elementar-Transistoren mitintegriert sind, die -angesteuert von 5V-Spannungshübe bis 40V und Ströme von

25 mA je Element liefern. Zusätzlich ist eine Kurzschlußsicherung und eine Temperaturüberwachung integriert. Für eine spezifische Anwendung sind wiederum Kosten und Zeit dadurch minimiert, daß Silizium-Scheiben in großen Losen 80% vorgefertigt bereitstehen und mit der nachfolgenden, anwendungsspezisischen Personalisierung über 2.000 spezisische digitale Gatterfunktionen eine spezifische Zusammenschaltung der Hochspannungs-Elementar-Transistoren ie Strombedarf und die Einstellung spezifizierter Kurzschlußströme sowie Temperaturgrenzen erfolgt. Auch hier kann für das Personalisieren optimal das Direktschreiben mit dem Elektronenstrahl eingesetzt werden.

An diesem Projekt sind die Firmen Autodisplay (Stuttgart), Gebhard Balluff (Leinfelden), Bizerba Werke (Balingen), RAFI (Ravensburg) beteiligt.

Abb. 2a: Blockdiagramm eines Mikrochips, auf dem neben 35.000 5V Transistoren 16 40V Transistoren für Ausgangstreiber zur Verfügung stehen. Zugleich mit der Personalisierung der Gatterfunktionen wird die Zahl der tatsächlich benötigten Ausgänge und der Strom je Ausgang (bis zu 200 mA) durch Zusammenschalten der Elementar-Transistoren personalisiert.

Hervorzuheben ist an diesem Programm, daß hier in einer Entwicklungsgemeinschaft mit mittelständischen Anwendern eine richtungsweisende Chip-Spezifikation und -Entwicklung initiiert wurde, die mit größter Wahrscheinlichkeit auch für andere mittelsständische Unternehmen von Nutzen sein wird, und daß die Industriepartner hier Pionierarbeit geleistet haben, die ihrer Industrie allgemein zugute kommen wird.

Anzumerken ist auch, daß dieses Projekt essentiell von der Möglichkeit des Direktschreibens mit dem Elektronenstrahl profitiert, die es am IMS nur infolge der weitsichtigen und substantiellen Forschungsförderung durch Bund, Land und die Großindustrie gibt.

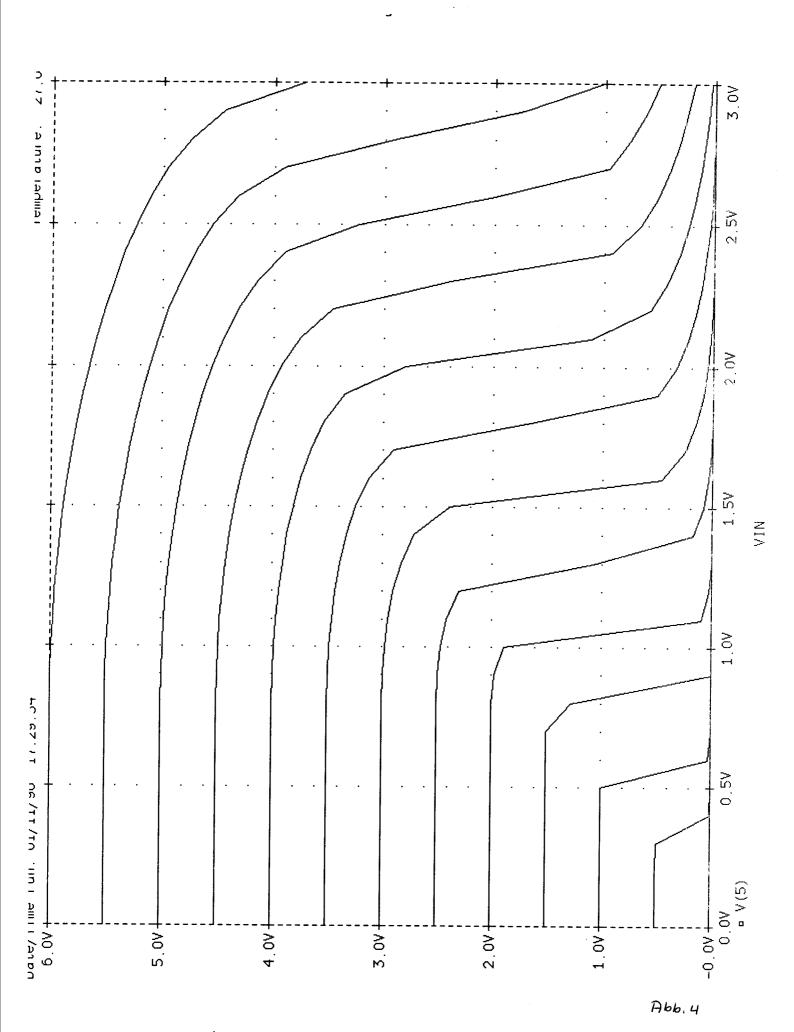

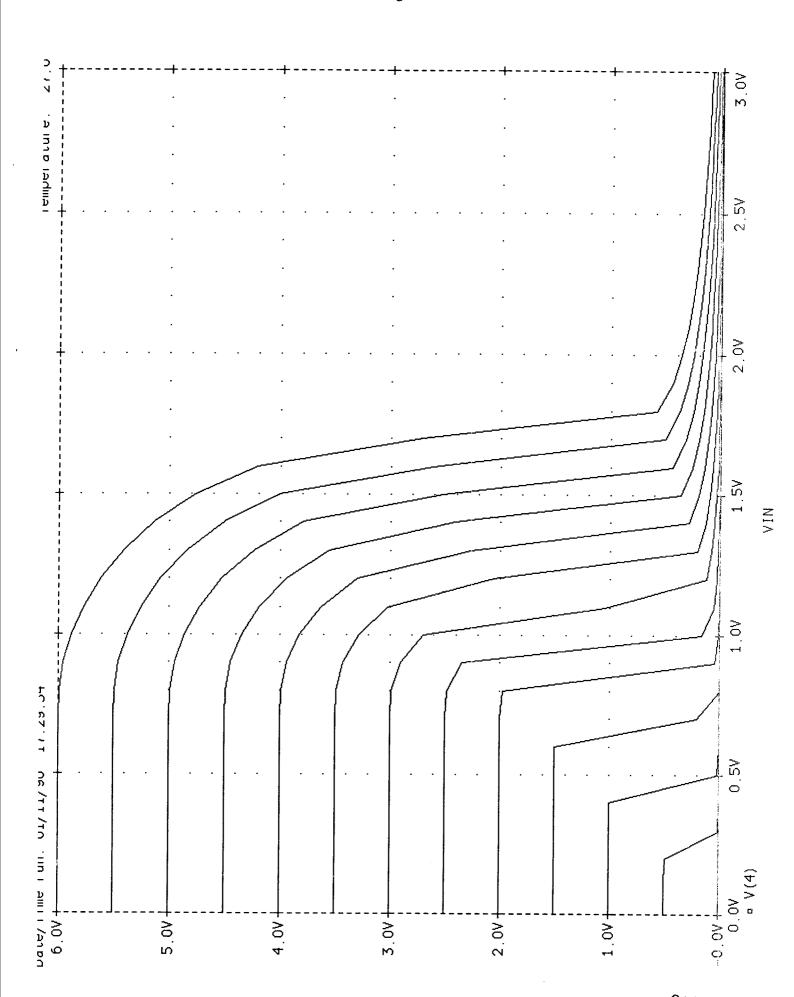

Abb. 2b: Ausgangskennlinienfelder von PMOS- (oben) und NMOS- (unten) Hochspannungstransistoren, die mit dem Standard-5V-CMOS-Prozess am Institut entwickelt und hergestellt wurden.

Ø Ø Ø Ø • Ø 0 0 Q 4 8 a ₽ 0000000 <u>ប្រជាសិទ្ធខ្មុជាប្រជា</u> ស្ថេច០០០០០២២ 8.8.8.888888888 p 0 THUJIFIER OF T

THE SECRET PROPERTY AND ADDRESS OF THE SECRET PROPERTY PROPERTY OF THE SECRET PROPERTY PROPERTY OF THE SECRET PROP

一年

**29** 10

Đ

0000

0000

യായിയ

0 8

CIG. 0 0 98 0000 0 0 0 000 da. 0 0 C G 0 - D **a a** 0000 jo P ďυ. 0 0 000 ERSENDING ARCHIVE M 8 8 8 8 8 8 8 8 8 8 C) a 🔝 G D 即山東 45 0 0 (2) D 0 B 0 9 He L 6 · 8 77-10 Ø ្រាស់ ព្រះ

Manager 10

#### ASICs: I-listorische Entwicklung und Wirtschaftlichkeit

#### 5. AUSBLICK / TRENDS

#### **TECHNOLOGIE**

- CMOS wird weiter skaliert bis Sub um-Bereich und dominante Technologie bleiben, getrieben durch Speicherentwicklung

- Bipolar hat feste analoge Nischen

- BICMOS eher zögernd zugenommen, weil Hybrid-Lösungen attraktiver sind

- Elektronenstrahl-Direktschreiben erlaubt schnelles und kostengünstiges Prototyping, speziell für kleine Stückzahlen

- Komplexitäten bis 100 Mia (10<sup>11</sup>) Transistoren möglich -> Ein-Chip-System

- Testbarkeit wird mitentscheidend sein, ob die technologischen Möglichkeiten überhaupt ausgenutzt werden können

### ASICs: Historische Entwicklung und Wirtschaftlichkeit

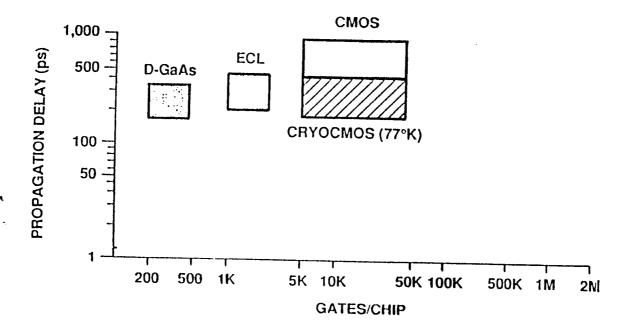

Figure 5-7. CryoCMOS Speed Performance

#### ASICs: Historische Entwicklung und Wirtschaftlichkeit

#### AUSBLICK / TRENDS

#### HARDWARE / SOFTWARE

- Kostengünstige Workstations (UNIX), für jeden Ingenieur (100 MIPS)

- Schaffung einer "integrierten Design-Umgebung ("framework"): mit geeigneten Schnittstellen

- Öffnung käuflicher Design-Systeme (CADENCE, SCS)

- Verknüpfung mit Bibliotheken der Halbleiterhersteller bewirkt "Single Sourcing"

- Designs direkt von System-Ingenieuren (Kunde), wobei bei digitalen Schaltungen die "Schlauheit" im Programm steckt

#### ASICs: I-listorische Entwicklung und Wirtschaftlichkeit

**Integration Complexity Trends**

## Fachbochschule Aalen Fachbereich Elektronik

Programm zur Berechnung des zeit- und frequenzabhängigen Sperrschichttemperaturverlaufs von Leistungshalbleitern mit Kühlkörpermontage

Verfasser: Prof. Rudolf Rudloff

Präsentation: Workshop an der Fachhochschule Mannheim,

12. Januar 1990

Programm zur Berechnung des zeit- und frequenzabhängigen Sperrschichttemperaturverlaufs von Leistungshalbleitern mit Kühlkörpermontage

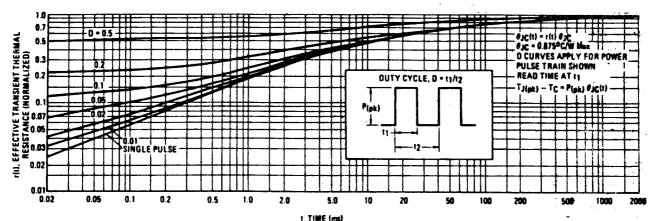

<u> Übersicht:</u> Das Programm ST (Sperrschicht-Temperatur) bietet dem Anwender ein leistungsfähiges Werkzeug zur Berechnung der zeit- und frequenzabhängigen Sperrschichttemperturänderungen von Leistungshalbleitern mit Kühlkörpermontage. Folgende zeitabhängige Verlustleistungsverläufe P(t) stehen zur Verfügung: Sprungfunktion, Rechteck mit einstellbarem Tastverhältnis und Treppenfunktion mit fünfzig einstellbaren Treppenstufen. Es lassen sich der Einschwingvorgang in einem vorzugebenden Zeitbereich und der eingeschwungene Zustand berechnen. Zur Bestimmung des Frequenzgangs der Sperrschichttemperaturänderung berechnet das Programm den Frequenzgang des thermischen Widerstandes  $\underline{Z}(w) = \underline{\mathscr{G}}(w)/\underline{P}(w)$ . Grafische und tabellarische Ausgabe der Rechenergebnisse sind möglich. Die allen Rechnungen zugrunde liegenden thermischen Ersatzbilder in Partialbruchschaltung des Leistungshalbleiters und des Kühlkörpers können vom Anwender direkt eingegeben und auch nachträglich noch geändert werden. Sind die sog. normierten transienten Wärmewiderstände r, (t) der Bauelemente bekannt, dann berechnet das Programm die thermischen Ersatzbilder in Partialbruchschaltung aus den einzugebenden Wertetabellen r, (k). Der Anwender des Programms ST wird durch eine leicht verständliche Menüführung unterstützt.

#### 1 Der transiente Wärmewiderstand

Nach DIN 41 862 ist der transiente Wärmewiderstand  $Z_{th}(t)$  (eines Halbleiterbauteils) der Quotient aus Sprungantwort der inneren Ersatztemperaturänderung  $\Delta \hat{V}_j(t)$  (Ersatzsperrschichttemperatur-Änderung) gegenüber einem äußeren thermischen Bezugspunkt mit konstanter Temperatur  $\hat{V}_c$  (Gehäuse) und Sprunghöhe  $P_o$  der sprungförmigen Verlustleistungsänderung  $P(t) = P_o \cdot \sigma(t)$ , die diese Temperaturänderung verursacht. Es wird vorausgesetzt, daß das Halbleiterbauteil für t < 0 die konstante Bezugstemperatur  $\hat{V}_c$  angenommen hatte.

Normierung mit  $Z_{th}^{(\infty)}$  ergibt den normierten transienten Wärme-widerstand  $r(t) = Z_{th}^{(\infty)}(t)/Z_{th}^{(\infty)}$ .

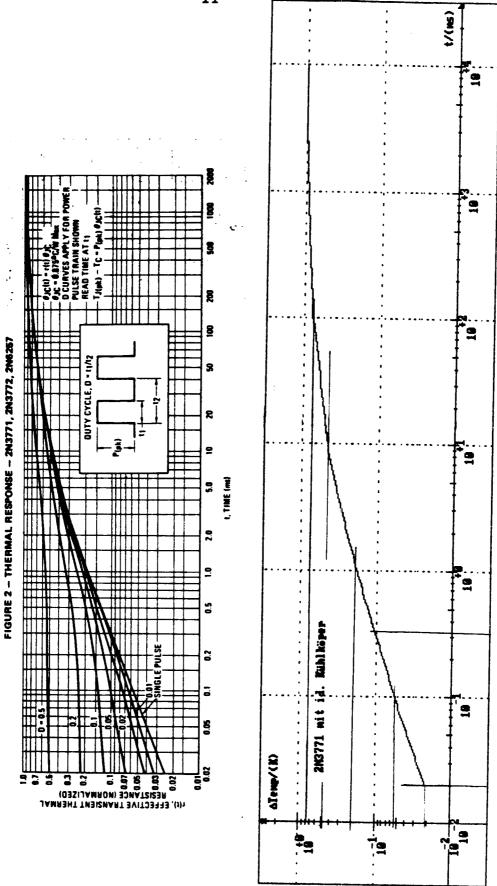

Bei Kenntnis des transienten Wärmewiderstands ist es möglich, die Elemente eines vereinfachten thermischen Ersatzbildes des Halbleiterbauteils zur Berechnung des dynamischen Verhaltens seiner Sperrschichttemperatur zu bestimmen. Da inzwischen viele Halbleiterhersteller [7] [8] [9] den normierten transienten Wärmewiderstand im Datenblatt angeben (Abb. 1), kann davon ausgegangen werden, daß in der Praxis häufiger als bisher das dynamische Verhalten der Sperrschichttemperatur berechnet wird. Um dieser Tatsache Rechnung zu tragen, wurde unter Auswertung einschlägiger Veröffentlichungen [1.1] [1.2] [1.3] [1.4] im Rahmen mehrerer Studienarbeiten [1] [2] [3] und einer Diplomarbeit [4] das Programm Sperrschicht-Temperatur geschrieben, das die von Hand nicht mehr zu bewältigenden Berechnungen ausführt.

Abb. 1: Normierter trans. Widerstand des Transistors 2N3771

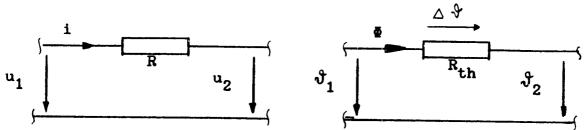

#### 1.1 Elemente eines thermischen Ersatzbildes

Zur Berechnung des Sperrschichttemperaturverlaufs soll ein Analogiemodell herangezogen werden, das auf Analogien zwischen thermischen und elektrischen Gesetzmäßigkeiten beruht. Es wird dadurch möglich, ein dem Elektroniker leicht verständliches Ersatzbild mit elektrischen Schaltzeichen zu entwickeln. Aus der Wärmelehre und der Elektrotechnik sind folgende Gesetzmäßigkeiten bekannt:

Wärmemengenänderung:

Anderung einer el. Ladung:

$$Q_{th} = \underset{\mathcal{V}_{1}}{\text{min}} \int_{1}^{\mathcal{V}_{2}} C(\mathbf{u}) d\mathbf{u}. \qquad (1) \quad (2)$$

Wärmemenge:

Elektrische Ladung:

$$Q_{th} = \int \Phi(t)dt + K_1.$$

$Q_{el} = \int i(t)dt + K_2.$  (3) (4)

Die Gl.(1) bis (4) liefern die nachstehend zusammengestellten Analogien [1.2DIN 41 862 Beiblatt].

| Thermische Kenngröß                         | Elektrische Kenngröße |                                          |

|---------------------------------------------|-----------------------|------------------------------------------|

| Wärmemenge Q <sub>th</sub>                  | in W                  | Ladung Q <sub>el</sub> = Q in As         |

| Wärmekapazität C <sub>th</sub> = m·c        | in Ws                 | Kapazität $C_{el} = C$ in $\frac{As}{V}$ |

| Wärmewiderstand (Thermischer Wid.) Rth      | in $\frac{K}{W}$      | Widerstand $R_{el} = R  in \frac{V}{A}$  |

| Temperaturunterschied $\triangle \vartheta$ |                       | Spannung u <sub>el</sub> = u in V        |

| Wärmestrom $\Phi = P$                       | in W                  | Strom i <sub>el</sub> = i in A           |

| Zeitkonstante Tth= RthCt                    | h <sup>in s</sup>     | Zeitkonstante T = R·C in s               |

Der thermische Widerstand wird in Analogie zum elektrischen Widerstand gemäß Abb. 2 definiert.

Abb. 2: Zur Definition des Wärmewiderstands

## 1.2 Vereinfachtes thermisches Ersatzbild eines Leistungstransistors

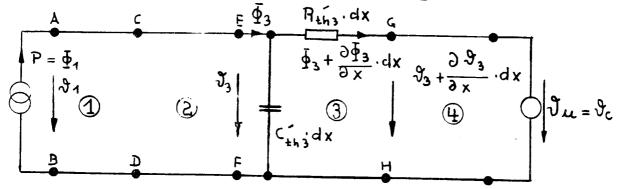

Abb. 3 zeigt den typischen Aufbau eines Leistungstransistors, den man unter stark idealisierten Bedingungen als Kettenschaltung mehrerer Stäbe mit unterschiedlichen thermischen Eigenschaften darstellen kann. Zusätzlich wird angenommen, daß der gesamte Wärmestrom von der Kollektorsperrschicht zum Gehäuse fließt, und die Wärmestromdichte über der jeweiligen Stabfläche konstant ist. Unter diesen Voraussetzungen kann das thermische Verhalten eines jeden Stabes als das eines eindimensionalen Wärmeleiters durch eine partielle Differentialgleichung vom parabolischen Typ beschrieben werden. Sie lautet:

$$\frac{\delta^2 \vartheta}{\delta x^2} - R'_{\text{thi}} \cdot C'_{\text{thi}} \cdot \frac{\delta \vartheta}{\delta t} = 0 \quad \text{bzw.} \quad -\frac{\delta \vartheta}{\delta x} = \Phi \cdot R'_{\text{thi}} \text{ und}$$

(5) (6)

$$-\frac{\delta\Phi}{\delta x} = \frac{\delta \mathcal{J}}{\delta t} \cdot \text{C'} \text{thi} \quad \text{mit R'}_{thi} = \text{Wärmewiderstandsbelag}$$

$$\text{und C'}_{thi} = \text{thermischer Kapazitätsbelag des}$$

$$\text{Stabes i.}$$

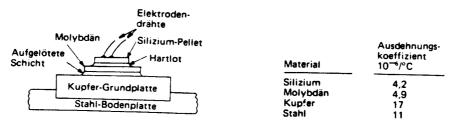

Typische Hartlot-Montage

Abb. 3: Leistungstransistor mit Hartlotmontage

Abb. 4: Thermisches Ersatzbild des Stabmodells

Abb. 5: Ersatzbild bei Approximation der homogenen R'thC'th-Leitungen durch einen Kettenleiter

Das aufgrund der Gl. (5) bis (7) in Abb. 4 gewonnene thermische Ersatzbild ist jedoch für die praktische Anwendung immer noch zu aufwendig. Es hat sich gezeigt, daß eine Approximation der homogenen Leitungsstücke in Abb. 4 durch eine endliche Zahl von konzentrierten thermischen Kapazitäten und Wärmewiderständen gemäß Abb. 5 zu brauchbaren Ergebnissen führt. Dies ist insbesondere deshalb möglich, weil die Temperaturänderung nur an der Stelle der sog. Ersatzsperrschicht A - B interessiert. Da es sich um ein lineares Netzwerk handelt, wird zur Berechnung der Temperaturänderung die Bezugstemperatur 3 gleich null gesetzt.

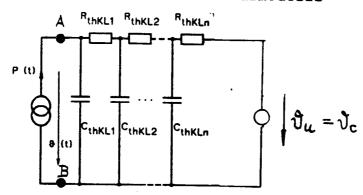

Die aus den physikalischen Gegebenheiten gewonnene Kettenleiterschaltung in Abb. 5 wird nun in eine für die Berechnung des transienten Wärmewiderstandes besser geeignete Partialbruchschaltung umgerechnet, die bezüglich der Punkte A - B der Kettenleiterschaltung äquivalent ist (Abb. 6).

Abb. 6: Bezüglich der Punkte A - B zur Kettenschaltung äquivalente Partialbruchschaltung

Mit Abb. 6 erhält man die Sprungantwort der Temperaturänderung  $\triangle \vartheta(t)$  an den Punkten A - B auf einen Verlustleistungssprung  $P(t) = P_o \cdot \sigma(t)$  für ein System ohne Vergangenheit:

$$\triangle \mathfrak{J}(t) = P_0 \cdot \sum_{i=1}^{n} R_{thPi} \cdot (1 - e^{-t/T_{thPi}}) \quad \text{mit} \quad T_{thPi} = R_{thPi} \cdot C_{thPi}.$$

(8)

Aus Gl. (8) ergibt sich die Näherung des transienten Wärmewiderstands

$$Z_{thn}(t) = \frac{\Delta \vartheta(t)}{P_o} = Z_{thn}(\infty) \cdot r_n(t) \quad mit$$

(9)

$$Z_{thn}(\infty) = \sum_{i=1}^{n} R_{thPi}.$$

(10)

Es besteht nun die Aufgabe, den vom Hersteller angegebenen Verlauf  $Z_{\rm th}(t) = Z_{\rm th}(\infty) \cdot r(t)$  durch den in Gl. (9) angebenen Verlauf  $Z_{\rm thn}(t)$  anzunähern.

## 1.3 Verfahren zur Berechnung der Elemente der Näherung des thermischen Ersatzbildes

Das in [1.4] beschriebene und in [1] angewandte numerische Verfahren zur Exponentialapproximation von transienten Wärmewiderständen liefert die Größen n,  $R_{\mbox{thPi}}$  und  $T_{\mbox{thpi}}$  der Näherung  $Z_{\mbox{thn}}(t)$  in einem zweiteiligen Approximationverfahren.

#### Teil 1

Mit den Gl. (9) und (10) wird definiert:

$$z_{n}(t) = Z_{thn}(\infty) - Z_{thn}(t) = \sum_{i=1}^{n} R_{thPi} \cdot e.$$

(11)

Normieren mit  $R_{thN}$  ( $^{\bullet}$ ) und Logarithmieren des Ausdrucks in Gl. (11) ergibt:

$$\ln(z_n^{\bullet}(t)) = z_n^{*}(t) = \ln \sum_{i=1}^{n} R_{thPi}^{\bullet} \cdot e^{-t/T_{thPi}}$$

(12)

Unter der Voraussetzung  $T_{th1} > T_{th2} > T_{th3} > \dots$  geht  $z_n^*(t)$  für  $t \to \infty$  in die Asymptote

$$a_1^*(t) = -\frac{t}{T_{thP1}} + \ln R_{thP1}^{\bullet} \quad \text{über.}$$

(13)

Mit dem vom Hersteller angegebenen transienten Wärmewiderstand erhält man:

$$z_{th}(t) = Z_{th}(\infty) - Z_{th}(\infty) \cdot r(t) \text{ bzw. } z_{th}^*(t) = \ln z_{th}^{\bullet}(t). \tag{14}$$

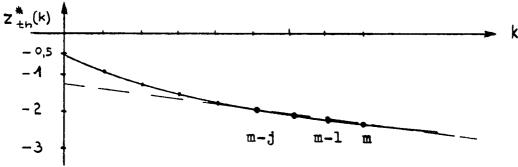

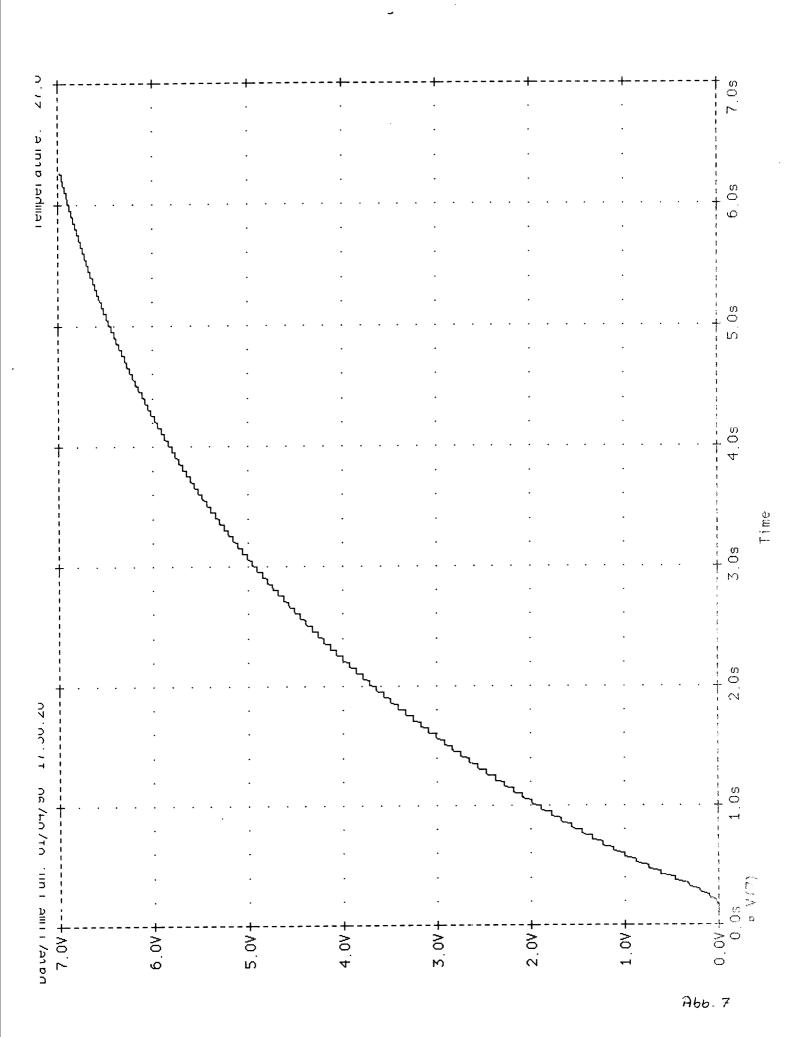

$z_{th}^*(t)$  möge als Wertefolge aus m Werten  $z_{th}^*(k)$  mit k = t/T gegeben sein. Ein typischer Verlauf ist in Abb. 7 dargstellt.

Abb. 7: Gegebener Werteverlauf von z\* (k)

Zu den letzten j Werten (Erfahrungswert j = 4) der Wertefolge aus m Werten (Erfahrungswert 8 bis 12 Werte pro Dekade) werden die Werte a und b der in Abb. 7 eingezeichneten Ausgleichsgeraden [1.5]

$y = a \cdot x + b$  berechnet.

Damit sind die Größen  $-1/(T_{\rm thP1}/T)$  = a und ln R $_{\rm thP1}^{\bullet}$  = b bekannt. Bei der Berechnung weiterer (R $_{\rm thPi}$ ,  $T_{\rm thPi}$ )-Paare verfährt man nach Subtraktion der jeweils bekannten Exponentialfunktion ebenso:

$$z_{\text{th}}^{\bullet}(k)$$

,  $\bar{z}_{\text{th1}}^{\bullet}(k) = z_{\text{th}}^{\bullet}(k) - R_{\text{thP1}}^{\bullet} \cdot e^{-k/(T_{\text{thP1}}/T)}$

$$\bar{z}_{\text{th2}}^{\bullet}(k) = z_{\text{th}}^{\bullet}(k) - R_{\text{thP1}}^{\bullet} \cdot e^{-k/(T_{\text{thP1}}/T)} - R_{\text{thP2}}^{\bullet} \cdot e^{-k/(T_{\text{thP2}}/T)}$$

Das Appoximationverfahren Teil 1 wird bei Erreichen einer Punktezahl kleiner j abgebrochen (bei der Subtraktion können Werte zu null werden). Ein Abbruch erfolgt auch, wenn

$\sum_{i=1}^{n} R_{thPi}^{\bullet} > Z_{th}^{\bullet}(\infty) \quad \text{geworden ist.} \quad \text{Für den thermischen Wider-}$

stand  $R_{thPn}^{\bullet}$  ergibt sich dann:

$$R_{thPn}^{\bullet} = Z_{th}^{\bullet}(\infty) - \sum_{i=1}^{n-1} R_{thPi}^{\bullet}.$$

(16)

Von der Ausgleichsgeraden ist jetzt b bekannt. Nach der Ausgleichsrechnung gilt für die Steigung der Ausgleichsgeraden y bei gegebenem b:

$$a = -\frac{1}{\frac{1}{T_{thPn}/T}} = \frac{\sum_{k=1}^{s} k \cdot \bar{z}_{th(n-1)}^{\bullet}(k) - \ln R_{thPn}^{\bullet} \cdot \sum_{k=1}^{s} k}{\sum_{k=1}^{s} k^{2}}, \text{ sofern die}$$

verbleibende Anzahl der Werte s  $\geq$  2 ist. Trifft dies nicht zu, wird  $T_{\text{thPn}} = T_{\text{thPmin}}$  gesetzt und wie folgt berechnet:

Der eingeschwungene Zustand des Partialbruchgliedes mit der größten Zeitkonstante  $T_{thP1}$  kann mit hinreichender Genauigkeit zum Zeitpunkt tmax =  $5 \cdot T_{thP1}$  als erreicht betrachtet werden. Der letzte eingegebene Wert des transienten Wärmewiderstands Zth(tmax) legt demnach die Zeit tmax fest. Bei einer Genauigkeit der Zeitmessung von  $p_T$ =  $10^{-b}$  ist damit die kleinste noch sinnvolle Zeitkonstante  $T_{thPmin} = T_{thP1} \cdot 10^{-b} = (tmax/5) \cdot p_T$ . Im vorliegenden Programm ist  $p_T$  =  $10^{-4}$  gesetzt.

#### Teil 2

Das Approximationsverfahren nach Teil 1 liefert die nullte Näherung mit einer Fehler-Wertefolge

$$F_0(k) = z_{th}^{\bullet}(k) - \sum_{i=1}^{n} R_{thPi}^{\bullet} \cdot e^{-k/(T_{thPi}/T)} \quad \text{mit } 1 \ge k \ge m, \quad (17)$$

aus der sich der mittlere quadratische Fehler der nullten Näherung

$$f_0 = \frac{\sqrt{\sum_{k=1}^{m} F_0(k)^2/m}}{\sum_{k=1}^{m} z_{th}^{\bullet}(k)/m}$$

ergibt. (18)

Zur Verbesserung der nullten Näherung addiert man in Gl. (17) zu beiden Seiten eine der n berechneten Exponentialfunktionen.

$$R_{\text{thPi}}^{\bullet} \cdot e^{-k/(T_{\text{thPi}}/T)} + F_{0}(k) = z_{\text{th}}^{\bullet}(k) - \sum_{i=1}^{n} R_{\text{thPi}}^{\bullet} \cdot e^{-k/(T_{\text{thPi}}/T)} +$$

$$R_{\text{thPi}}^{\bullet} \cdot e^{-k/(T_{\text{thPi}}/T)}$$

(19)

Die linke Seite in Gl. (19) zeigt, daß die erzielte Näherung noch Fehler aufweist. Deshalb wird eine neue Exponentialfunktion angesetzt, die mit Hilfe einer Ausgleichgeraden bestimmt wird. Die rechte Seite der Gl. (19) wird abgekürzt mit  $\alpha(k)$  bezeichnet. Somit ergibt sich:

$$(R_{\text{thPi}}^{\bullet} \cdot e^{-k/(T_{\text{thPi}}/T)})_{\text{neu}} = \alpha(k).$$

(20)

Logarithmieren der Gl. (20) führt auf

$$\{\ln R_{\text{thPi}}^{\bullet} - k/(T_{\text{thPi}}/T)\}_{\text{neu}} = \ln \alpha(k). \tag{21}$$

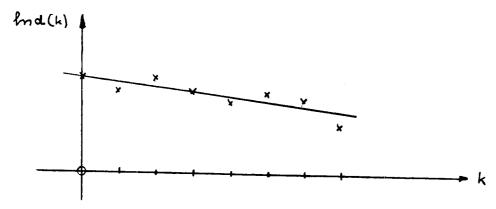

Die linke Seite in Gl. (20) kann nur positive Werte liefern. Es wird deshalb zuerst, beginnend bei k = 1, geprüft, bis zu welchen k =  $\beta$   $\alpha(k)$  > 0 ununterbrochen gilt. Die noch folgenden Werte ab k >  $\beta$  werden ausgeschieden. Zu den Werten  $\alpha(k)$  mit  $1 \ge k \ge \beta$  berechnet man die Ausgleichsgerade, aus der sich  $R_{thPineu}$  und  $T_{thPineu}$  bestimmen lassen (Abb. 8). Das Verfahren wird zwecks Berechnung der ersten (verbesserten) Näherung fortgesetzt, bis alle 'alten' Partialbruchglieder durch 'neue' ersetzt sind.

Abb. 8: Zur Berechnung von RthPineu und TthPineu

Die Abbruchkriterien entsprechen denen in Teil 1. Es kann also vorkommen, da $\beta$  sich die Zahl der neuen Partialbruchglieder verringert.

Bleibt die Zahl n der Partialbruchglieder erhalten, ergibt sich folglich nacheinander:

Ensprechend Gl. (17) und (18) werden nun  $\mathbf{f_1}(\mathbf{k})$  und  $\mathbf{f_1}$  mit den 'neuen' Partialbruchgliedern berechnet. Ist  $\mathbf{f_1} < \mathbf{f_0}$ , schließen sich weitere Approximationsverfahren an, bis  $\mathbf{f_h} > \mathbf{f_{h-1}}$  ist.

#### 1.4 Approximationsergebnisse für den Transistor 2N3771

Transistor 2N3771

MWe eingeben, ändern / TPE berechnen / TPEs vergleichen

TPE eingeben, ändern Therm. Überg. - Wid. Daten löschen

Bildschirmausgabe fortsetzen : Leertaste drücken

| Eingegebene | Meβwerte des Wärmewiderstands | Näherungswerte | Abweichung |

|-------------|-------------------------------|----------------|------------|

| T/ms        | R/ 1.170K/W                   | RA/ 1.170K/W   | in %       |

| 0.020       | 0.024                         | 0.021          | -10.5      |

| 0.040       | 0.035                         | 0.034          | -2.3       |

| 0.070       | 0.046                         | 0.046          | +0.6       |

| 0.100       | 0.056                         | 0.055          | -1.7       |

| 0.200       | 0.080                         | 0.078          | -2.5       |

| 0.400       | 0.113                         | 0.114          | +0.8       |

| 0.700       | 0.152                         | 0.153          | +0.8       |

| 1.000       | 0.183                         | 0.182          | -0.3       |

| 2.000       | 0.251                         | 0.250          | -0.5       |

| 4.000       | 0.343                         | 0.338          | -1.5       |

| 7.000       | 0.420                         | 0.420          | -0.1       |

| 10.000      | 0.469                         | 0.470          | +0.1       |

| 20.000      | 0.565                         | 0.555          | -1.9       |

| 40.000      | 0.642                         | 0.641          | -0.1       |

| 70.000      | 0.717                         | 0.717          | +0.0       |

| 100.000     | 0.776                         | 0.765          | -1.5       |

| 200.000     | 0.847                         | 0.843          | -0.5       |

| 400.000     | 0.895                         | 0.895          | +0.0       |

| 700.000     | 0.928                         | 0.926          | -0.2       |

| 1000.000    | 0.946 .                       | 0.946          | +0.0       |

| 2000.000    | 0.981                         | 0.981          | +0.0       |

|             |                               | - <del>-</del> |            |

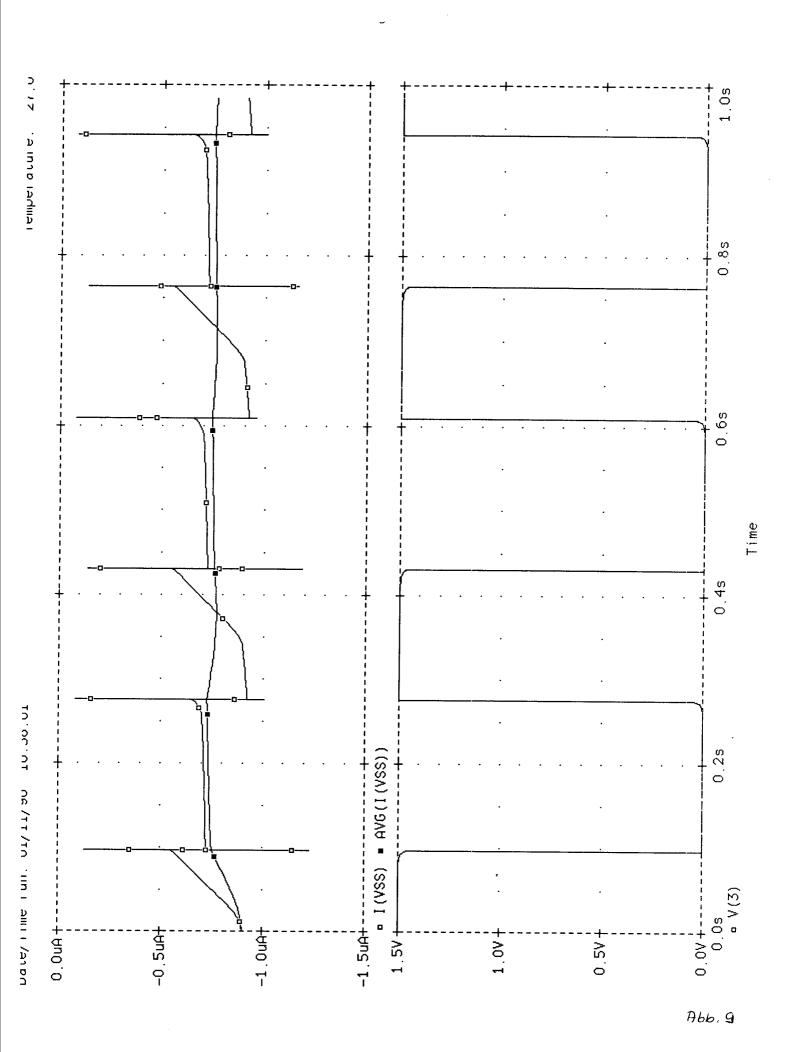

Abb. 9: Vergleichende Gegenüberstellung von gegebenem und appropproximiertem normierten transienten Wärmewiderstand des Transistors 2N3771

Abb. 10: Grafische Darstellungen des gegebenen und des approximierten transienten Wärmewiderstands des Transistors 2N3771

#### 1.5 Thermische Ersatzbilder von Kühlkörpern

Für Kühlkörper werden keine transienten Wärmewiderstände angegeben. Die Angabe ist auch insofern problematisch, als daβ die den Wärmewiderstand bestimmenden Strahlungs- und Konvektionskoeffizienten von der Temperatur abhängig sind. Zusätzlich beeinflußt die Montagestelle auf dem Kühlkörper den transienten Wärmewiderstand aufgrund der endlichen thermischen Leitfähigkeit der Kühlkörpermaterials (Al).

Wegen dieser fehlenden Angaben wurden im Rahmen einer Studienarbeit [5] unter Annahme eines linearen thermischen Verhaltens Messungen an häufig eingesetzten Kühlkörpern vorgenommen. Die Montagestelle war stets die geometrische Mitte. Die Messung erfolgte so dicht wie möglich (Sackloch) unterhalb der Wärmequelle (Transistor). Die gemessenen zeitabhängigen Sprungantworten der Kühlkörpertemtemperatur führten zu den in der Studienarbeit [6] dokumentierten thermischen Partialbruch-Ersatzschaltungen.

Als grobe Näherung kann die thermische Ersatzschaltung aus einem  $R_{\rm th}$ .  $C_{\rm th}$ -Glied verwendet werden. Der thermische Widerstand  $R_{\rm th}=Z_{\rm th}(\infty)$  und die Masse m sind in den Datenblättern der Kühlkörperhersteller enthalten. Die thermische Kapazität ergibt sich zu

$$C_{th} = m \cdot c$$

mit der spezifischen Wärme  $c = c_{Al} = 900 \xrightarrow{\text{Ws}} \text{für}$

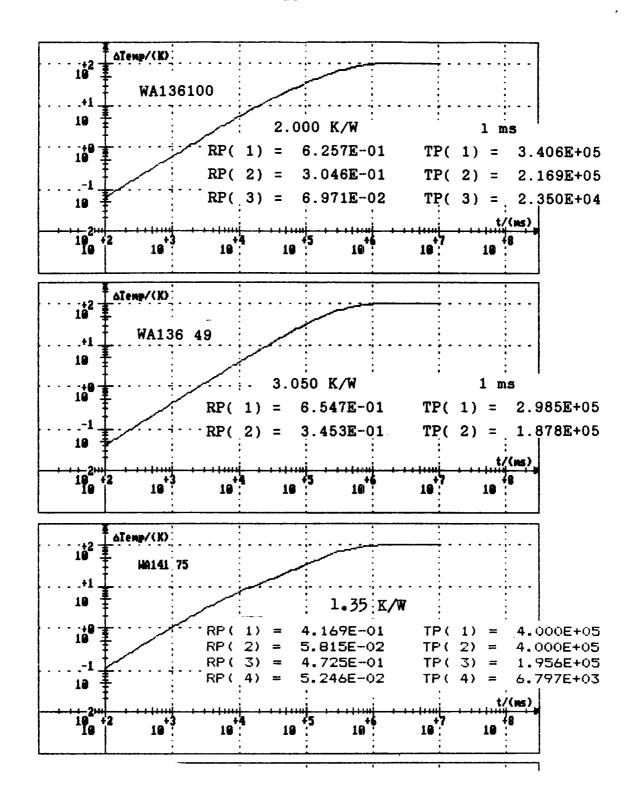

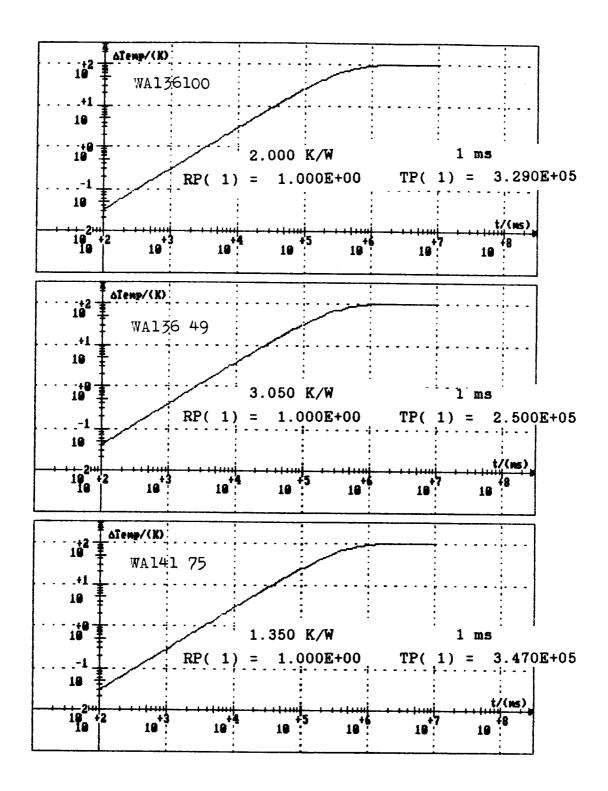

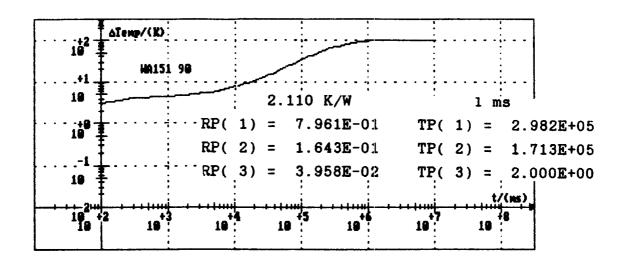

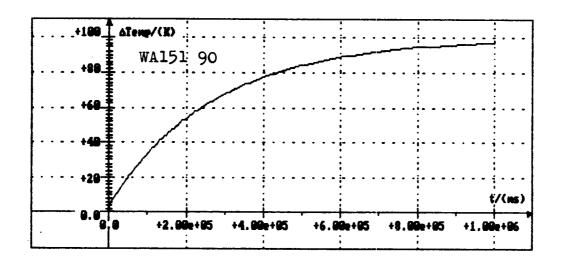

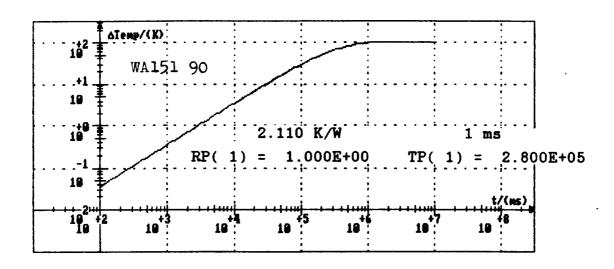

Kühlkörper aus Aluminium. Die Ergebnisse der zeitabhängigen Kühlkörpertemperaturverläufe, die man unter Verwendung der aus den Temperaturmessungen gewonnenen Ersatzbilder erhält, sind für mehrere Kühlkörper in den Abb. 11 und 12 dargestellt. Die Abb. 13 und 14 zeigen die Ergebnisse, wenn für dieselben Kühlkörper die einfache R<sub>th</sub>, C<sub>th</sub>-Näherung des thermischen Ersatzbildes benutzt wird.

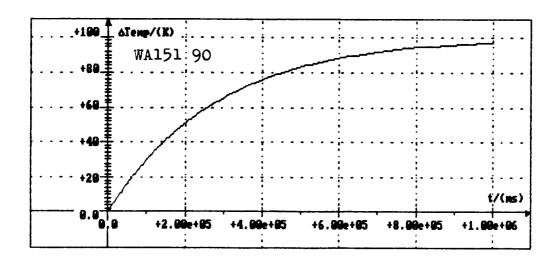

Abb. 11: Sprungantworten der Temperaturverläufe bei Kühlkörpern mit thermischen Ersatzbildern aufgrund gemessener transienter Wärmewiderstände

Abb. 13: Sprungantworten der Temperaturverläufe bei Kühlkörpern mit thermischen Ersatzbildern aufgrund einfacher  $R_{\rm th}$ ,  $C_{\rm th}$ -Glieder

Abb. 12: Sprungantworten der Temperaturverläufe bei einem Kühlkörper mit thermischem Ersatzbild aufgrund des gemessenen transienten Wärmewiderstands

Abb. 14: Sprungantworten der Temperaturverläufe bei einem Kühlkörper mit thermischem Ersatzbild aufgrund eines einfachen  $R_{\rm th}$ ,  $C_{\rm th}$ -Gliedes

### 1.6 Berechnung des zeitabhängigen (Ersatz)sperrschichttemperaturverlaufs bei Leistungshalbleitern mit Kühlkörpermontage

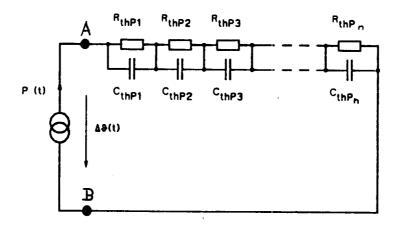

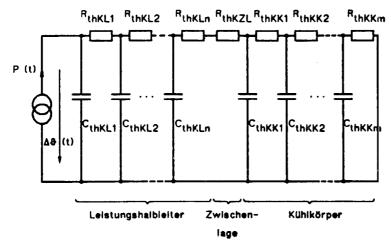

Bei Montage eines Leistungshalbleiters auf einem Kühlkörper unter Verwendung einer isolierenden Zwischenlage müssen die thermischen Ersatzbilder der einzelnen Bauelemente als Kettenschaltungen vorliegen. Die Gesamtkettenschaltung der Ersatzbilder aller Bauelemente ist zum Schluß wieder in eine Partialbruchschaltung zurückzurechnen, um eine einfache Berechnung des zeit- und frequenzabhängigen Sperrschichttemperaturverläufe zu ermöglichen.

Das Programm zur Umrechnung der thermischen Partialbruchschaltungen in thermische Ketten(bruch)schaltungen entstand auf der Grundlage des in [2.1] angegebenen Verfahrens ebenfalls im Rahmen einer Studienarbeit [2]. Auf die Umrechnungsprozedur soll hier nicht näher eingegangen werden. Da die thermische Kapazität der Zwischenlage als klein gegenüber der thermischen Kapazität des Kühlkörper angenommen werden kann, ist ihre thermische Kettenschaltung ein reeller thermischer Widerstand. Die gesamte thermische Ersatzschaltung Leistungshalbleiter-Zwischenlage-Kühlkörper zeigt Abb. 15. Das Programm führt folgende Berechnungen durch:

- 1. Umrechnung der Leistungshalbleiter-Partialbruchschaltung in die äquivalente Kettenschaltung.

- 2. Kettenschaltung der kurzgeschlossenen Zwischenlage-Kettenschaltung zu 1. und Umrechnung in die Ketten-Gesamtschaltung.

- 3. Berechnung der thermischen Kettenschaltung aus der Partialbruchschaltung des Kühlkörpers und Berechnung der Kettenschaltung Leistungshalbleiter-Zwischenlage-Kühlkörper.

- 4. Rückrechnung in die endgültige Partialbruch-Gesamtschaltung.

Als Beispiel einer thermischen Partialbruch-Gesamtschaltung ist in Abb. 16 das Ergebnis für den Transistor 2N3771, montiert mit Zwischenlage  $R_{\rm th}$  = Rzz = 0.36 K/W auf einem Kühlkörper WA136100, angegeben.

Abb. 15: Kettenleiter-Gesamtschaltung.

```

Gesamt-TPE

Grad =10

normiert auf: 1 K/W

1 ms

RP(1) = 0.342E-01

TP(1) = 0.257E-01

RP(2) = 0.964E-01

TP(2) = 0.419E+00

RP(3) = 0.108E-01

TP(3) = 0.901E+00

RP(4) = 0.345E+00

TP(4) = 0.416E+01

RP(5) = 0.179E+00

TP(5) = 0.251E+02

RP(6) = 0.330E+00

TP(6) = 0.934E+02

RP(7) = 0.447E+00

TP(7) = 0.317E+04

RP(8) = 0.169E+00

TP(8) = 0.246E+05

RP(9) = 0.549E+00

TP(9) = 0.221E+06

RP(10) = 0.137E+01

TP(10) = 0.350E+06

```

Abb. 16: Partialbruch-Gesamtschaltung 2N3771+Z1+WA136100

#### 2 Berechnung zeitabhängiger Sperrschichttemperaturverläufe

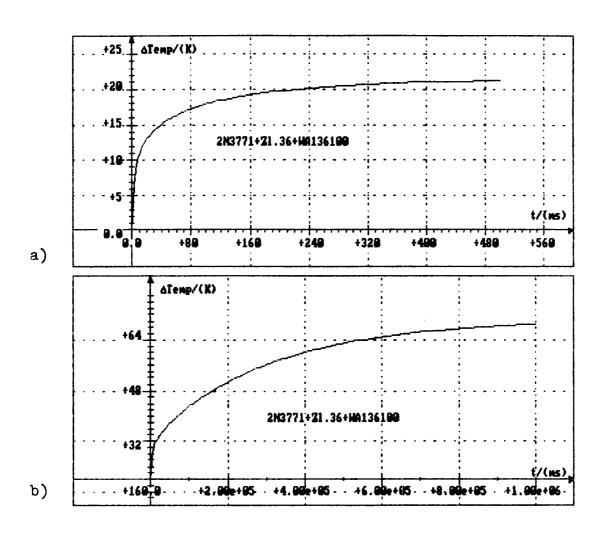

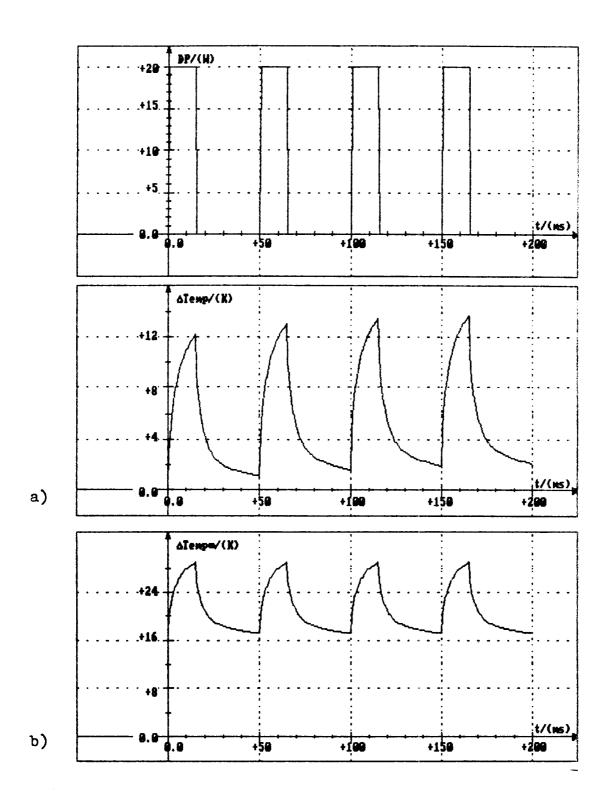

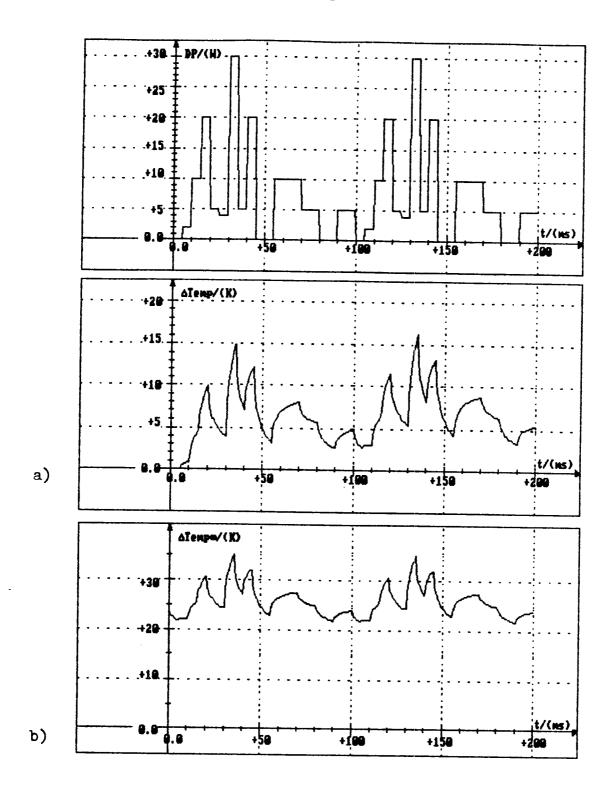

Die Berechnung der zeitabhängigen Sperrschichttemperaturverläufe ist, abgesehen vom Aufwand, einfach durchzuführen. Es handelt sich in allen Fällen (Sprung, Rechteck und Treppenfunktion) um die Lösung gewöhnlicher linearer Differentialgleichungen erster Ordnung mit konstanten Koeffizienten für ein System mit Vergangenheit. Von einer näheren Beschreibung soll hier abgesehen werden. Abb. 17 zeigt die Sprungantwort der Sperrschichttemperatur des Transistors 2N3771, montiert auf einem Kühlkörper WA136100 unter Verwendung einer Zwischenlage mit  $R_{\rm th}=Rzz=0.36$  K/W. Für dieselbe Konfiguration sind in den Abb. 18 und 19 die Antworten auf rechteck- bzw. treppenförmigen Verlauf der Verlustleistung dargestellt.

Abb. 17: Sprungantwort der Sperrschichttemperatur für 2N3771+Z1.36+WA136100 a) t  $\geq$  0 b) t<sub>1</sub>  $\geq$  t  $\geq$  t<sub>2</sub>

Abb. 18: Zeitabhängige Sperrschichttemperaturverläufe für 2N3771+Z1.36+WA136100 bei rechteckförmigem Verlustleistungsverlauf

a) Einschwingvorgang b) Eingeschwungener Zustand

Abb. 19: Zeitabhängige Sperrschichttemperaturverläufe für 2N3771+Z1.36+WA136100 bei treppenförmigem Verlustleistungsverlauf

a) Einschwingvorgang b) Eingeschwungener Zustand

# 3 Berechnung der Ortskurve des Frequenzgangs des thermischen Widerstands $Z_{th}(w)$

Um eine gleichmäßige Kreisfrequenzverteilung längs der Ortskurve zu erzielen, empfiehlt sich eine logarithmische Frequenzteilung. Dazu wird

- die Partialbruchwiderstandsfunktion mit dem kleinsten Realteil RTP<sub>a</sub> an der Stelle w = 0 ermittelt und

- 2. die Partialbruchwiderstandsfunktion mit der kleinsten Zeitkonstanten TTP<sub>b</sub> durch Berechnung der kleinsten Winkeländerung  $\Delta\theta/\Delta$ w an der Stelle w = 0 bestimmt.

Bei der höchsten Kreisfrequenz  $\mathbf{w}_{ob}$  soll gelten:

Re

$$\left|\frac{ZTP_{b}}{w=w_{ob}}\right|_{w=w_{ob}} = 0.1 \cdot RTP_{a}$$

, so daß  $\frac{RTP_{b}}{1 + w_{ob}^{2}TTP_{b}^{2}} = 0.1 \cdot RTP_{a}$  (22)

wird. Aus Gl. (22) folgt:

$$w_{ob} = \frac{1}{TTP_b} \sqrt{\frac{10 \cdot RTP_b}{RTP_a} - 1}$$

(23)

Die kleinste Kreisfrequenz, die größer als null ist, wird festgelegt auf  $w_0 = 0.1/TTP_c$ . Dabei ist  $TTP_c$  die größte vorkommende Zeitkonstante.

Die logarithmische Teilung der Kreisfrequenz-Zwischenwerte erhält man mit  $w_i = w_0 \cdot e$   $\frac{\ln (w_{ob}/w_0)}{200} \cdot (i-1)$  mit  $i=1 \dots 200.$  (24)

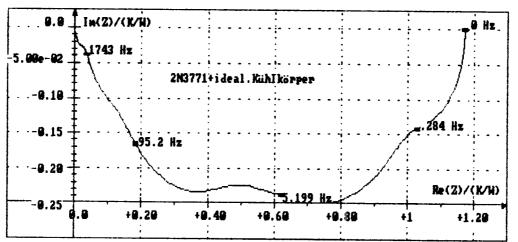

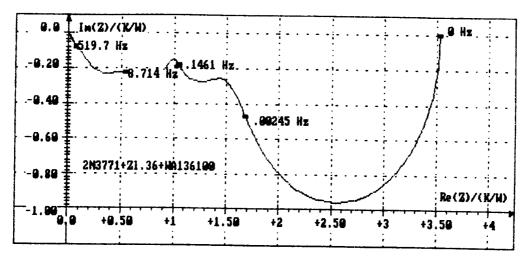

Mit Gl. (24) werden 200 Kreisfrequenzwerte berechnet, mit denen die Ortskurve gezeichnet wird. Beispiele für einen Transistor mit idealem bzw. realem Kühlkörper zeigen die Abb. 20 bzw.21.

Abb. 20: Ortskurve des Wärmewiderstands des Transistor 2N3771 mit idealem Kühlkörper

Abb. 21: Ortskurve des Wärmewiderstands der Anordnung 2N3771+Z1.36+WA136100

#### 4 Probleme bei der Programmanwendung

Grundsätzlich sollten die Werte der einzugebenden transienten Widerstände zuvor in doppelt logarithmischem Maßstab aufgetragen werden, um Meßfehler, insbesondere bei kleinen Zeiten, erkennen zu können. Bei Zeitkonstanten < 10<sup>-5</sup>s der thermischen Partialbruchersatzschaltung eines Leistungshalbleiters in Verbindung mit Zeitkonstanten > 10<sup>3</sup>s des Kühlkörpers kann es zur Überschreitung des darstellbaren Zahlenbereichs (GWBASIC: 10<sup>-37</sup> bis 10<sup>37</sup>) und damit zu falschen Ergebnissen kommen, da noch nicht alle 'overflows' abgefangen werden. Es wird empfohlen, die kleinste Zeitkonstante von Hand auf 10<sup>-5</sup>s zu korrigieren (Achtung: Die Meßwerte werden anschließend gelöscht). Weitere Hinweise sind der Studienarbeit [6] zu entnehmen.

#### 5 Literaturverzeichnis

[1] Entwicklung eines Programms zur Berechnung der Elemente des thermischen Ersatzbildes eines Halbleiterbauelements Gerold Horn, Studienarbeit 1986, Fachbereich Elektronik Fachhochschule Aalen

#### [1.1] DIN 41 784 Blatt 1

[1.2] DIN 41 862, DIN 41 862 Beiblatt 1

Halbleiterbauelemente und integrierte Mikroschaltungen

Mit der Temperatur zusammenhängende Begriffe,

Benennungen und Erklärungen

#### [1.3] DIN IEC 47(CO)886

Halbleiterbauelemente und integrierte Schaltungen Meßverfahren, Wärmewiderstandsmessung über die Emitter-Basis-Spannung in Vorwärtsrichtung

#### [1.4] W. Büttner

Ein numerisches Verfahren zur Exponentialapproximation von transienten Wärmewiderständen Archiv für Elektrotechnik 59 (1977) 351-359

#### [1.5] Fetzer/Fränkel

Mathematik Band 3 VDI-Verlag 1979

[2] Entwicklung von Programmen zur Berechnung des Temperaturverhaltens von Bauelementen als Funktion der Zeit und der Frequenz

Martin Kaiser, Studienarbeit 1986, Fachbereich Elektronik, Fachhochschule Aalen

#### [2.1] Jürgen Schwarz

Thermische Ersatzschaltbilder Elektronik Journal 7/85

- [3] Programm zur Berechnung des zeit- und frequenzabhängigen Sperrschichttemperaturverlaufs von Transistoren mit Kühlkörpermontage

Werner Schäfer, Studienarbeit 1987, Fachbereich Elektronik, Fachhochschule Aalen

- [4] Entwicklung eines menügesteuerten Programms zur Berechnung des zeit- und frequenzabhängigen Sperrschichtemperaturverhaltens von Leistungshalbleitern

Werner Schäfer, Diplomarbeit 1988, Fachbereich Elektronik, Fachhochschule Aalen

- [5] Meβeinrichtung zur Messung transienter Wärmewiderstände von Kühlkörpern

Lars Freier, Studienarbeit 1988, Fachbereich Elektronik, Fachhochschule Aalen

- [6] Zusammenstellung von Dimensionierungsunterlagen zur Berechnung des zeit- und frequenzabhängigen Sperrschichttemperaturverhaltens von Leistungshalbleitern mit Kühlkörpermontage unter Verwendung des Rechnerprogramms ST Hartmut Stadelmaier, Studienarbeit 1989, Fachbereich Elektronik, Fachhochschule Aalen

- [7] BIPOLAR POWER TRANSISTORS DATA MOTOROLA INC. Printed in Switzerland 1985

- [8] THYRISTOR DATA

MOTOROLA INC.

Printed in Switzerland 1985

- [9] THOMSON CSF

POWER TRANSISTORS

1986

## ENTWURF EINES UHREN-IC ALS VOLLKUNDEN-SCHALTKREIS

#### MIT ZEITZEICHEN-EMPFÄNGER

R.Lieder, G.Kampe, A.Volk

Fachhochschule für Technik Esslingen (FHTE) Labor CAD der Mikroelektronik

Es wird über eine Diplomarbeit im Wintersemester 1989/90 berichtet, in der die Methode des strukturierten Chip-Entwurfs für einen digitalen CMOS-Uhren-Schaltkreis angewandt wurde. Dabei kamen folgende CAD-Programme zum Einsatz: P/C-SILOS für die Logiksimulation, KICBOX für das Layout, SPICE für die Ermittlung typischer Schaltzeiten. Für den Modul zur Dekodierung des DCF77-Zeitzeichensenders wurden Unterlagen erstellt, welche die Fertigung als Prototyp-Chip am Institut für Mikroelektronik Stuttgart ermöglichen.

#### 1. EINLEITUNG

Zu Beginn der hier vorgestellten Diplomarbeit wurden bekannte Lösungen für Uhren-ICs studiert. Bild 1 zeigt einige typische Eigenschaften . Aufgrund dieser Erkenntnisse wurde dann ein Pflichtenheft für den eigenen Entwurf aufgestellt (Bild 2). Eine Besonderheit der geplanten Schaltung stellt die Einbeziehung eines DCF77-Dekoders dar. Über eine externe Langwellenantenne und Impulsformer (CMOS-Pegel) mit Vorverstärker besteht somit Möglichkeit. vom DCF77-Sender die der Physikalisch Technischen Bundesanstalt ausgestrahlten Zeitsignale zu dekodieren und damit die Uhr ständig automatisch und äußerst präzise einzustellen.

Im weiteren Verlauf der Arbeit wurde die Schaltungsidee in eine strukturierte CMOS-Schaltung (Vollkunden-Schaltkreis) umgesetzt. Dabei wurde der Verifikation der Schaltungsteile besondere Aufmerksamkeit geschenkt.

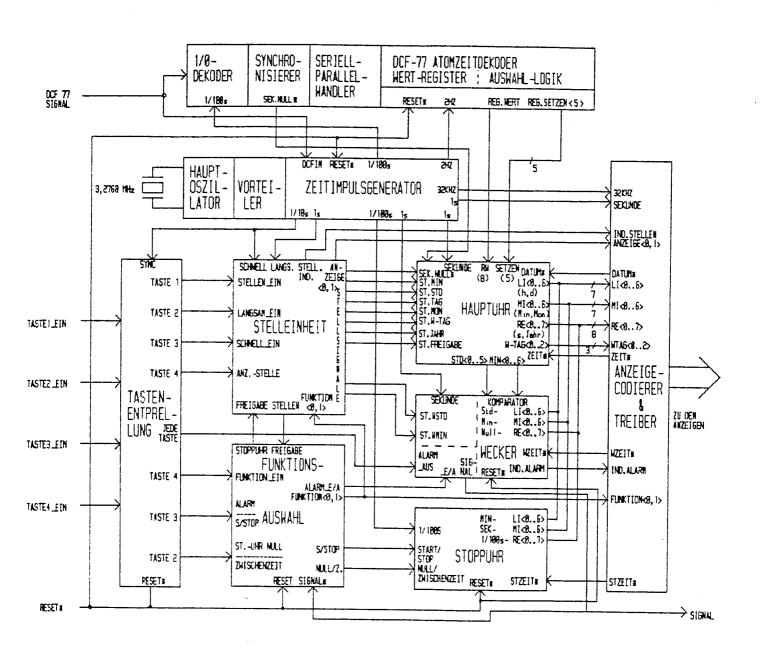

#### 2. BLOCKSCHALTBILD

Bild 3 zeigt das Blockschaltbild der gesamten Schaltung in der obersten Entwurfsebene. Als Taktquelle dient ein Schwingquarz mit einer Frequenz von 3,2768 MHz. Folgende Funktionsblöcke werden unterschieden:

## - HAUPTOSZILLATOR mit VORTEILER und ZEITIMPULSGENERATOR

Hier werden mehrere Taktsignale generiert:

- .. 3,2 kHz für den Anzeige-Multiplexer

- .. 100 Hz für den DCF77-Dekoder und die Stoppuhr

- .. 10 Hz für die Tasten-Entprellung und die Stelleinheit

- .. 1 Hz für die Stelleinheit und die Hauptuhr (Sekunden-Takt)

#### - TASTEN-ENTPRELLUNG

Hiermit werden die 4 Bedientasten entprellt bzw. bei Bedarf verriegelt.

#### - HAUPTUHR , WECKER , STOPPUHR

Dies sind die zentralen Module der Schaltung. Die Zeitinformation wird als Gruppe von 6 BCD-Codeworten über die 3 Busse LI, MI und RE an den Anzeige-Codierer übergeben:

- .. Stunde, Minute, Sekunde von der Hauptuhr

- .. Stunde , Minute, Dunkelcode vom Wecker

- .. Minute, Sekunde, Hundertstel-Sekunde von der Stoppuhr

## - FUNKTIONSAUSWAHL , ANZEIGE-CODIERER UND -TREIBER

Der Modul Funktionsauswahl wählt die oben angegebenen Zeitinformationen für den Anzeige-Codierer aus und setzt außerdem die funktionsspezifische Tastenbetätigung um. Der Anzeige-Codierer enthält einen 7-Segment-Decoder sowie einen Multiplexer für die externe LED-Anzeige.

#### - STELLEINHEIT

Mit diesem Modul lassen sich Wecker und Hauptuhr (z.B. bei Störung des DCF77-Empfangs) von Hand stellen, wobei die jeweils einzustellende Ziffer blinkt.

#### - DCF77-DEKODER

Dieser Modul stellt automatisch über einen eigenen Bus die Zeitregister der Hauptuhr, sooft eine gültige Zeitinformation empfangen wird.

#### 3. ENTWURFSWERKZEUGE

Beim rechnergestützten Entwurf einer komplexen Vollkunden-Schaltung ist der Einsatz von Hilfsprogrammen unentbehrlich, die eine Entwurfshierarchie vom groben Blockschaltbild (Bild 3) bis zur detaillierten Gestaltung der Geometrie von Transistoren und Leiterbahnen ermöglichen. Im vorliegenden Fall wurde das CAD-System KICBOX eingesetzt, um erforderliche CMOS-Standardzellen neu zu entwerfen bzw. aus einer Bibliothek (FH Furtwangen) einzufügen.

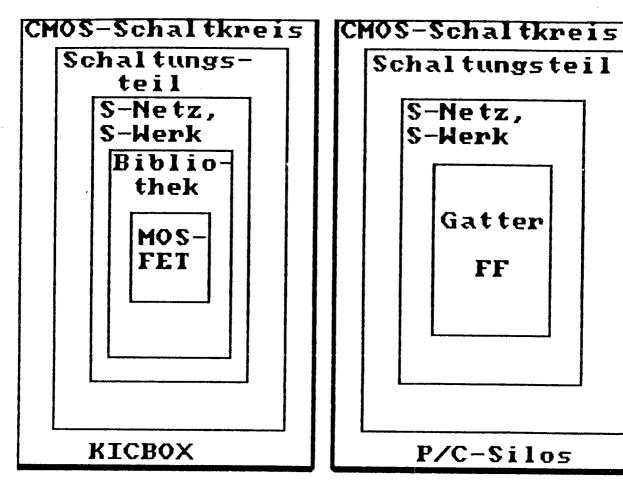

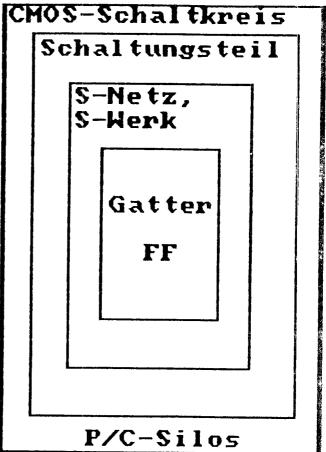

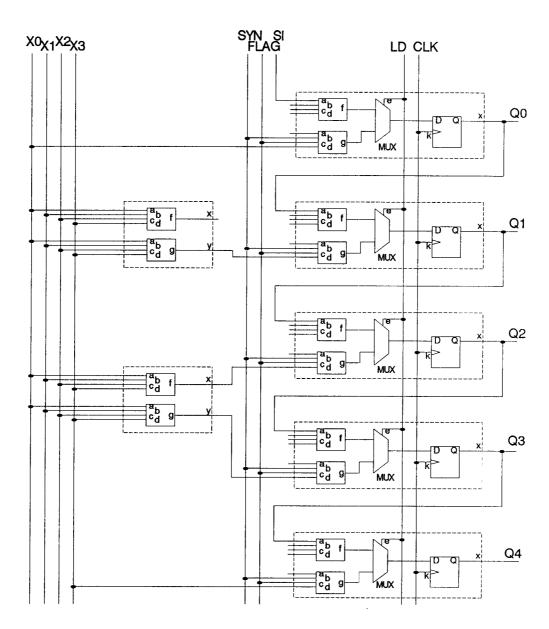

Bild 4 zeigt links die Hierarchiestufen beim Entwurf mit dem KICBOX-System vom MOS-Transitor über Schaltnetze, Schaltwerke bis zum gesamten CMOS-Schaltkreis.

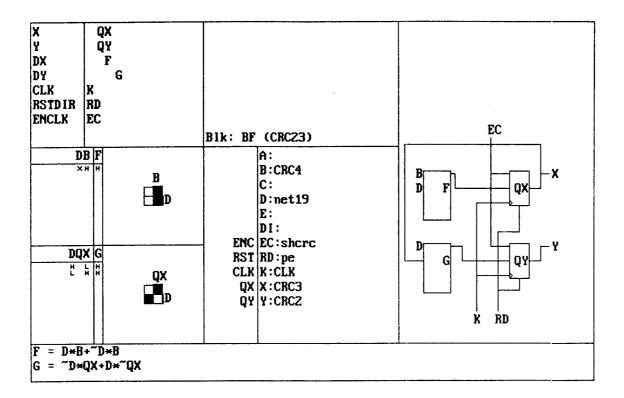

Zur Verifikation der Schaltungteile wurde auf unterster Ebene (Schaltglied aus Einzeltransistoren) das Simulationsprogramm SPICE verwendet, um das Zeitverhalten der neuen Standardzellen zu ermitteln.

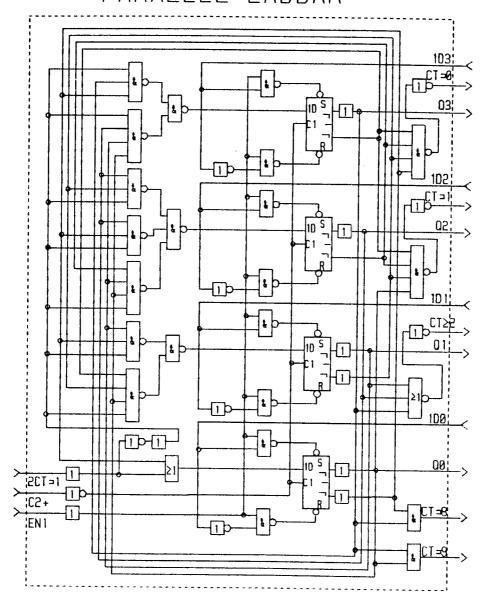

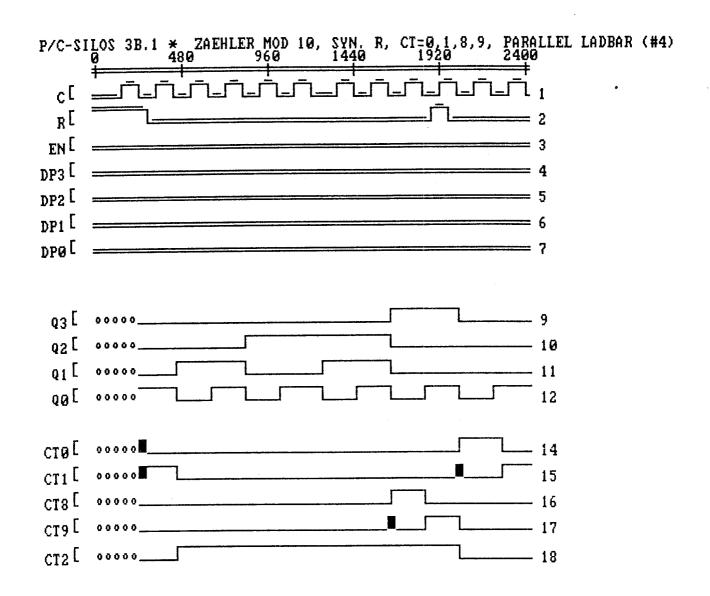

Für Überprüfung der aus Standardzellen zusammengesetzten Schaltungsteile (z.B. Zähler, siehe Bild 5) würde SPICE zuviel Speicherplatz und Rechenzeit benötigen. Daher wurde hierfür der Logiksimulator P/C-SILOS eingesetzt. Es handelt sich hierbei um einen Simulator mit 12 Signalzuständen (4 Logikwerte, 3 Impedanzwerte). Anstiegs- und Abfallzeiten sind für jedes Schaltglied individuell vorgebbar, z.B. abhängig vom Fan-out. Bild 4 zeigt rechts Hierarchiestufen beim Entwurf mit P/C-SILOS.

Das KICBOX-System ermöglicht die Schaltungs-Rückgewinnung aus dem Layout, z.B. um eine Simulation mit SPICE durchzuführen. Leider ist aber in KICBOX keine entsprechende Schnittstelle zu P/C-SILOS vorhanden, sodaß für die Logiksimulation die Schaltung nochmals von Hand einzugeben war.

Am Beispiel des Zählers aus Bild 5 wird in Bild 6 gezeigt, wie mit P/C-SILOS z.B. die Wirkung des RESET-Signals R untersucht werden kann. Von besonderem Interesse sind dabei die auftretenden Störimpulse.

#### 4. HIERARCHISCHES LAYOUT

Im Folgenden soll die Vorgehensweise beim strukturierten Entwurf des Uhren-ICs verdeutlicht werden. Der Zähler (Schaltungs-Makro) aus Bild 5 enthält als Standardzellen Kippglieder und logische Verknüpfungsglieder. Er ist selbst wieder Bestandteil in mehreren "übergeordneten" Modulen.

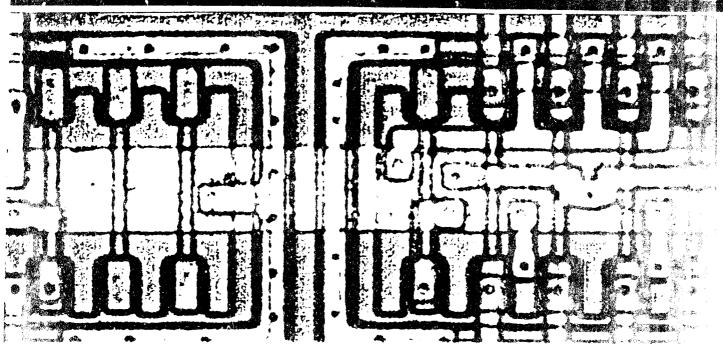

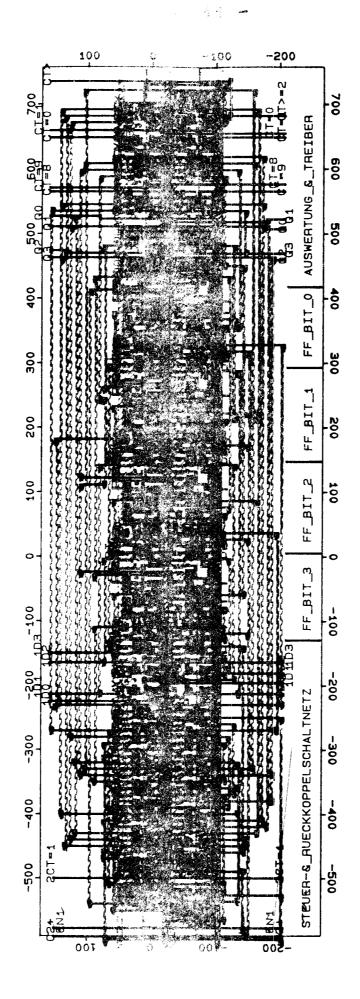

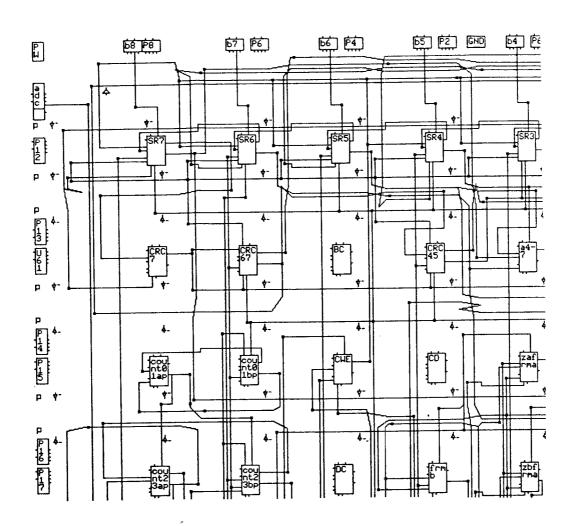

Bild 7 zeigt das Layout des Zählers, um einen Eindruck von der Flächenaufteilung zu vermitteln. Die im Zähler enthaltenen 4 Kippglieder haben Setz- und Rücksetzeingänge. Da die Standardzellen-Bibliothek bisher diesen Fliplop-Typ nicht enthielt, wurde eine vorhandene Standardzelle hierfür modifiziert. Das Ergebnis zeigt Bild 8.

Im Hinblick auf einen möglichst effektiven Entwurf des gesamten Uhren-IC wurde eine Reihe geeigneter Schaltungs-Makros mit KICBOX entworfen und mit P/C-SILOS auf ihre Funktion getestet. Dabei wurde versucht, die Vielfalt möglichst einzugrenzen (Entwurfs- und Testaufwand!), was jedoch einen erhöhten Flächenbedarf für die Makros bedeutet (nicht alle Teile eines Makros werden bei bei jedem Verwendungsfall benötigt). Bild 9 gibt einen Überblick über den Einsatz der einzelnen Makros in den Schaltungsmodulen.

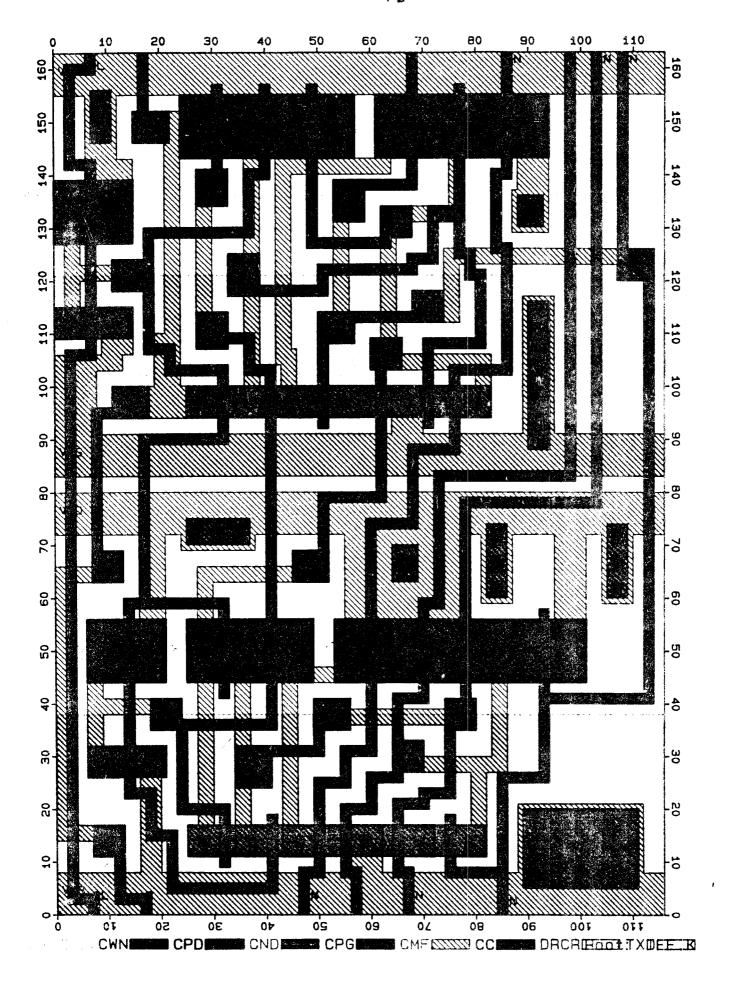

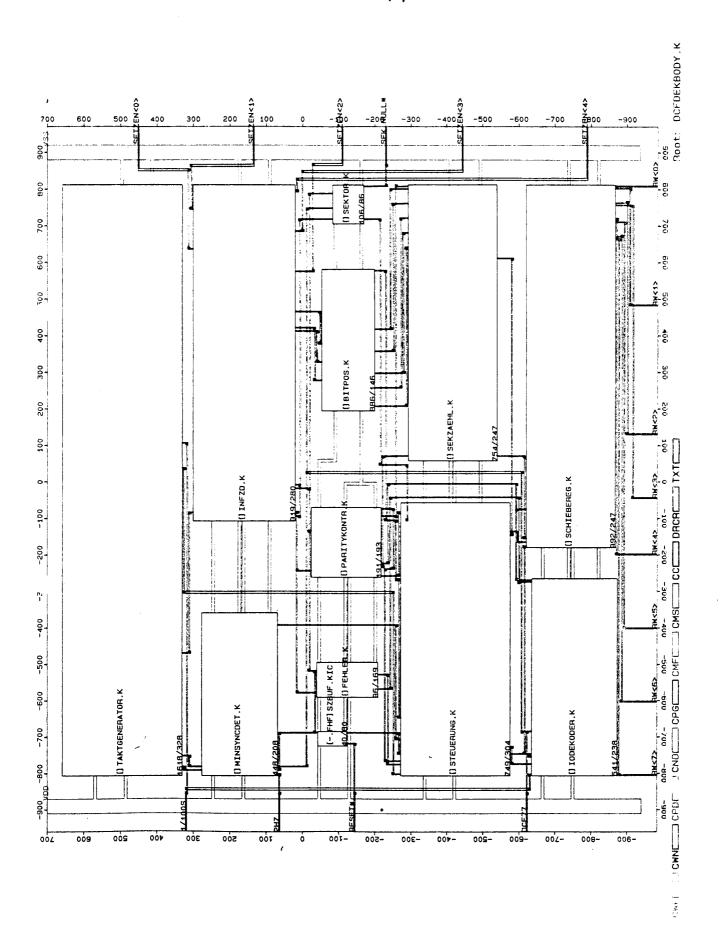

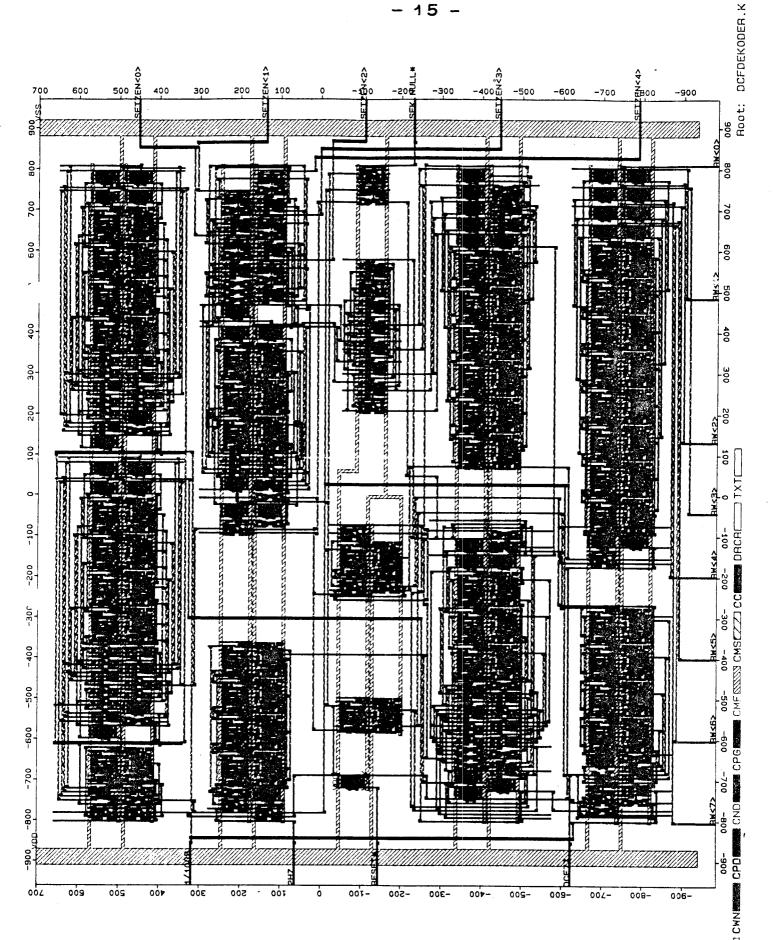

#### 5. DCF77-DEKODER

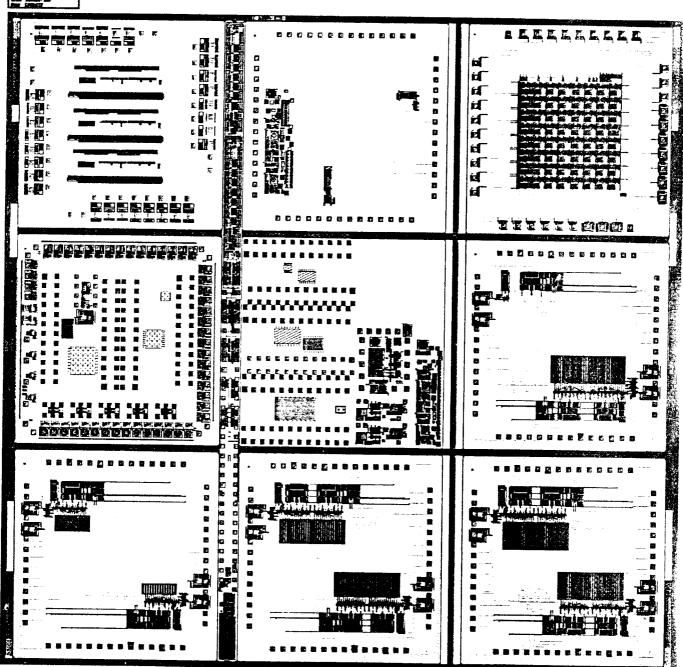

Da die Bearbeitungszeit im Rahmen einer Diplomarbeit auf ca. 5 Monate begrenzt war, wurde der DCF77-Dekoder ausgewählt und als einziger Modul komplett verdrahtet. Bild 10 zeigt den Floorplan und Bild 11 das Layout mit Transistoren und Verbindungsleitungen. Bei einem Redesign ist eine Verringerung des Flächenbedarfs denkbar, wobei dies jedoch auf Kosten der "Regelmäβigkeit" gehen dürfte. Es ist geplant, diesen Dekoder als separates

Chip im Rahmen der MPC-Projekte am Institut für Mikroelektronik Stuttgart fertigen zu lassen. Eine weiterführende Arbeit wird sich mit der Entflechtung (Plazieren und Verdrahten) der restlichen Module aus Bild 3 in einem zweiten Chip beschäftigen.

#### 6. ABSCHLUSSBEMERKUNG

Aufgrund der konsequent angewandten strukturierten Entwurfsmethode konnte in der vorliegenden Arbeit in kurzer Zeit der Entwurf eines komplexen Chips durchgeführt werden. Die Unzulänglichkeit der CAD-Werkzeuge (kein automatischer Router bei KICBOX, keine automatische Netzlisten-Umwandlung von KICBOX nach P/C-SILOS) mußte durch erhöhten Arbeitsaufwand ausgeglichen werden. Es ist zu hoffen, daß nach dem Neuerwerb der CAD-Werkzeuge von Mentor Graphics der Entwurf komplexer Chips im Labor CAD der Mikroelektronik an der FHTE künftig noch professioneller erfolgen kann.

## STROMVERSORGUNG UND TAKTFREQUENZ

Nieder-oder Hochfrequenzquarzoszillator Batteriebetrieb (1.5V) oder Netzspeisung für 5V

### ANZEIGEN UND ANZEIGETREIBER

LCD-Display (meist ohne Multiplexer)

LED-Anzeigen mit Multiplexansteuerung

Anzeigeformat vier oder sechs Stellen

### BEDIENEI EMENTE

Drei bis sechs Bedientasten

Funktionsauswahl durch Stufenschalter

## FINGEBAUTE FUNKTIONEN

Uhr mit Datum und Stoppuhr

Uhr mit Datum und Weckerfunktion

Zeitzeichen-Empfänger

## EINGEBAUTE FUNKTIONEN:

Uhrzeit mit vollem Kalenderdatum Wecker mit Nachweckautomatik Stoppuhr mit 1/100s Auflösung

## BEDIENELEMENTE:

4 Tasten, davon

eine Taste zum Einstellen der Uhr

eine Taste zur Funktionsauswahl

zwei Tasten für spezielle Funktionen

## ANZEIGEEINHEIT

6-stellige LED-Anzeige mit Sekundenpunkt, Wochentaganzeige und diversen Indikatoren. Anzeigetreiber im Multiplexbetrieb

<u>Bild 3:</u> Blockschaltbild (oberste Entwurfsebene) .

Bild 4: Hierarchiestufen der Entwurfswerkzeuge KICBOX (Layout) und P/C-SILOS (Logiksimulation) .

# ZAEHLER MOD 10, SYN. R, CT=0,1,8,9,≥2 PARALLEL LADBAR

<u>Bild 5:</u> Zähler als Bei**sp**iel für eine Schaltungs-Makro aus Standardzellen .

==== Signalquelle ohne Innenwiderstand

oooo Logikwert nicht definiert

\_\_\_\_\_ Störimpuls (Spike)

Bild 7: Layout des Zählers aus Bild 5.

Bild 8: Layout eines Flipflop aus Bild 7.

|                  | DCF-77-Dekoder | Zeitbasis | Hauptuhr | Stelleinheit | Funktionsauswahl | Tastenentprellung | Wecker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Anzeige-Codierung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------------|-----------|----------|--------------|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Zähler MOD 10    | 2              | 2         | 7        |              |                  |                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Zähler MOD 6     |                |           | 2        |              |                  |                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The state of the s |