# MULTIPROJEKTCHIP GRUPPE

**BADEN-WÜRTTEMBERG**

# MPC-Workshop Februar 2006 Esslingen

Cooperating Organization Solid-State Circuits Society Chapter IEEE Germany Section

ISSN 1862-7102

Herausgeber: Fachhochschule Ulm

### © 2006 Fachhochschule Ulm

Das Werk und seine Teile sind urheberrechtlich geschützt. Jede Verwertung in anderen als den gesetzlich zugelassenen Fällen bedarf deshalb der vorherigen schriftlichen Einwilligung des Herausgebers Prof. A. Führer, Fachhochschule Ulm, Prittwitzstraße 10, 89075 Ulm.

#### Adressen der

# MULTIPROJEKT-CHIP-GRUPPE (MPC-Gruppe) BADEN - WÜRTTEMBERG

http://www.mpc.belwue.de

Hochschule Aalen

Prof. Dr. Bartel, Postfach 1728, 73428 Aalen

Tel.: 07361/576-107, Fax: -324, Email: manfred.bartel@htw-aalen.de

Hochschule Albstadt-Sigmaringen

Prof. Dr. Rieger, Johannesstr. 3, 72458 Albstadt-Ebingen Tel.: 07431/579-124, Fax: -149, Email: rieger@hs-albsig.de

Hochschule Esslingen

Prof. Dr. Kampe, Flandernstr. 101, 73732 Esslingen

Tel.: 0711/397-4221, Fax: -4212, Email: gerald.kampe@fht-esslingen.de

Hochschule Furtwangen

Prof. Dr. Rülling, Postfach 28, 78113 Furtwangen

Tel.: 07723/920-503, Fax: -610, Email: rue@hs-furtwangen.de

Hochschule Heilbronn

Prof. Dr. Clauss, Max-Planck-Str. 39, 74081 Heilbronn

Tel.: 07131/504400, Fax: /252470, Email: clauss@hs-heilbronn.de

Hochschule Karlsruhe

Prof. Dr. Koblitz, Postfach 2440, 76012 Karlsruhe

Tel.: 0721/925-2238, Fax: -2259, Email: rudolf.koblitz@hs-karlsruhe.de

Hochschule Konstanz

Prof. Dr. Voland, Brauneggerstraße 55, 78462 Konstanz

Tel.: 07531/206-644, Fax: -559, Email: voland@fh-konstanz.de

Hochschule Mannheim

Prof. Dr. Albert, Speyerer Str. 4, 68136 Mannheim

Tel.: 0621/2926-351, Fax: -454, Email: g.albert@fh-mannheim.de

Hochschule Offenburg

Prof. Dr. Jansen, Badstr. 24, 77652 Offenburg

Tel.: 0781/205-267, Fax: -242, Email: d.jansen@fh-offenburg.de

Hochschule Pforzheim

Prof. Dr. Kesel, Tiefenbronner Str. 65, 75175 Pforzheim

Tel.: 07321/28-6567, Fax: -6060, Email: frank.kesel@fh-pforzheim.de

Hochschule Ravensburg-Weingarten

Prof. Dr. Ludescher, Postfach 1261, 88241 Weingarten

Tel.: 0751/501-9685, Fax: -9876, Email: ludescher@hs-weingarten.de

Hochschule Reutlingen

Prof. Dr. Kreutzer, Alteburgstraße 150, 72762 Reutlingen

Tel.: 07121/341-108, Fax: -100, Email: hans.kreutzer@reutlingen-university.de

Hochschule Ulm

Prof. Führer, Postfach 3860, 89028 Ulm

Tel.: 0731/50-28338, Fax: -28363, Email: fuehrer@fh-ulm.de

### Inhaltsverzeichnis

|     |                                                                                                                                   | Seite |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.  | Schaltungsentwurf für GATE FOREST - Chips J. Burghartz, T. Deuble, IMS Chips Stuttgart                                            | 5     |

| 2.  | Simulation und Layout eines schnellen CMOS-Serializers<br>C. Brandler, HP. Bürkle, HS Aalen                                       | 11    |

| 3.  | Designstudie für einen 10 Bit-Analog-Digital-Umsetzer M. Diebold, G. Forster, HS Ulm A. Erni, K. Hofmann, AIM Infrarot-Module Ulm | 19    |

| 4.  | Modellierung und Synthetisierung des Peripheriebausteins SAB8279<br>C. Voelkle, HS Ulm                                            | 29    |

| 5.  | A Small Imprint RISC for Ubiquitous Systems for SOC Designs D. Jansen, HS Offenburg                                               | 35    |

| 6.  | Low Power Features in Design and Technology for Mobile Application Chips K. M. Just, Infineon München                             | 43    |

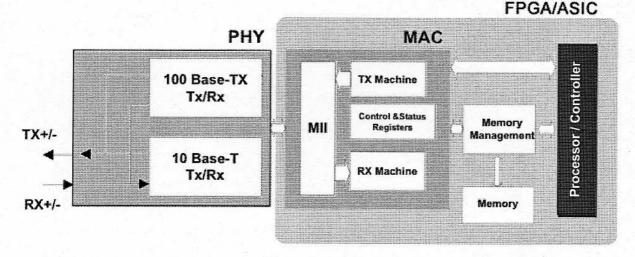

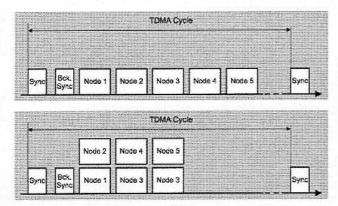

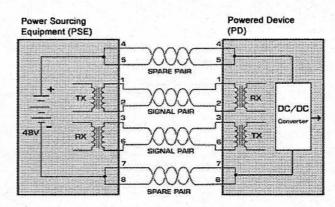

| 7.  | Investigations into Ethernet and Realtime-Ethernet Interfaces PC. Wu, IMS Chips Stuttgart                                         | 47    |

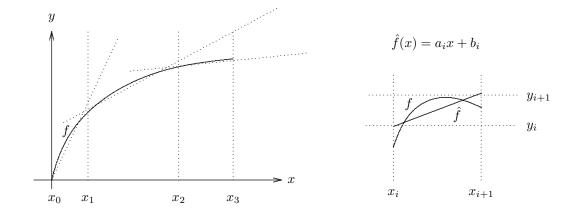

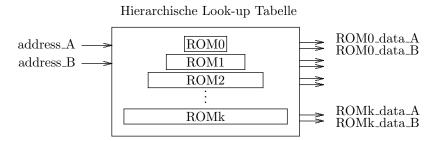

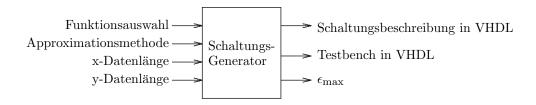

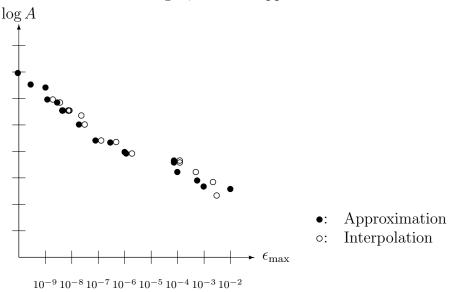

| 8.  | Funktionsberechnung mit hierarchischen Look-up Tabellen W. Rülling, HS Furtwangen                                                 | 53    |

| 9.  | Circuit Design Methodology - Oder: Die Physik hat uns wieder<br>C. Wandel, IBM Böblingen                                          | 67    |

| Ge  | fertigte Bausteine                                                                                                                |       |

| 10. | Versatile Search Processor ASIC  A. Epstein, HS Mannheim                                                                          | 80    |

| 11. | LED-Flasher D. Bau, D. Jansen, HS Offenburg                                                                                       | 81    |

#### Schaltungsentwurf für GATE FOREST - Chips

Prof. Dr.-Ing. Joachim Burghartz, Dipl.-Ing.(FH) Thomas Deuble Institut für Mikroelektronik Stuttgart, Allmandring 30a, 70569 Stuttgart Telefon 0 711 / 21 855 -200, Fax -222, E-Mail burghartz@ims-chips.de

Das Institut für Mikroelektronik Stuttgart arbeitet seit langem eng mit der Multiprojekt-Chip-Gruppe Baden-Württemberg zusammen. Eine ganze Reihe MPC-Chips wurden bereits am IMS gefertigt. Dieser Artikel zeigt die aktuellen Möglichkeiten und Neuerungen beim Schaltungsentwurf mit dem IMS GATE FOREST auf.

Mit der gänzlich am IMS etablierten 0,8um CMOS-Technologie GFN ("GATE FOREST N") steht für Forschung und industrielle Entwicklung ein stabiler und zuverlässiger Herstellprozess zur Verfügung. Damit lassen sich in kurzer Zeit Chips mit bis zu 100.000 digitalen Gattern in Kombination mit umfangreichen analogen Funktionen herstellen. Der Prozess ist nach mehreren internationalen Normen und Qualitätsstandards zertifiziert und unterliegt strengen Qualitätskontrollen. Das bedeutet, dass jeder vom IMS ausgelieferte Chip Industriequalität aufweist. Dies wissen industrielle und wissenschaftliche Anwender seit Jahren zu schätzen. IMS-Chips finden sich in zahlreichen Produkten und Anwendungen, von der einfachen Infrarot-Fernbedienung bis hin zum Einsatz in Radar-Satelliten zur Erderkundung.

Großen Wert legt das IMS auf eine intensive und persönliche Betreuung von Entwicklungspartnern und Kunden. Satzungsgemäß unterstützt das IMS als wirtschaftsnahes Institut des Landes Baden-Württemberg besonders die kleinen und mittelständischen Unternehmen bei der Bewältigung Herausforderungen. mikroelektronischen Spezielle und nur für einzelne Unternehmen produzierte ASICs ("anwendungsspezifische integrierte Schaltungen") ermöglichen innovative Problemlösungen auf kleinstem Raum und schützen wertvolles Know-how. Ein stets aktuelles Thema ist der Nachbau von Standard-ICs, die beispielsweise in langlebigen Produkten eingebaut sind. Der internationale Halbleitermarkt entwickelt sich sehr dynamisch und die großen Chiphersteller nehmen viele ihrer Standardprodukte bereits nach wenigen Jahren als "obsolete" wieder vom Markt, was in der Folge zu Versorgungsproblemen für die industriellen Anwender führt. Das IMS kann hier regelmäßig helfen und liefert vollkompatible Ersatzbausteine, die im Kundenauftrag kurzfristig und auch in kleinen Stückzahlen produziert werden können.

#### 1. Das GATE FOREST - Prinzip

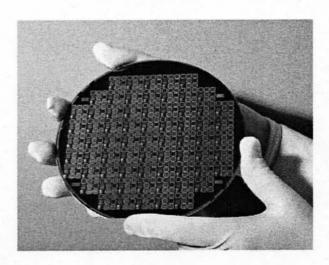

Die GATE FOREST – Chips lassen sich rasch und kostengünstig fertigen, weil sie auf vorgefertigten Master-Scheiben basieren. Das bedeutet, dass diese Silizium-Wafer in einem ersten zeitaufwändigen Teilprozess mit einem "Meer" von einzelnen Transistoren versehen werden, was man auch als "Sea-of-Gates" bezeichnet. Diese vorprozessierten Scheiben werden

dann nach Kundenwunsch in einem zweiten Teilprozess "personalisiert", das heißt die vorhandenen Transistoren werden über Leiterbahnen elektrisch so miteinander verbunden, dass die geforderte Schaltungsfunktion entsteht.

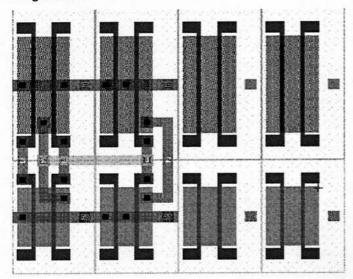

Ausschnitt aus einem GFN-Layout: rechte Bildhälfte zeigt vier Transistoren ohne Personalisierung; links sind Transistoren über Leiterbahnen verbunden.

Derzeit stehen acht unterschiedliche Master-Typen zur Verfügung, die sich in Chipfläche, Zahl der realisierbaren analogen und digitalen Funktionen und in der Anzahl der Anschlusspads unterscheiden. Der kleinste Master, GFN001 ist ein rein digitaler Chip mit etwa 300 Gattern und maximal 26 I/O-Pads. Der größte ist der GFN120, mit ca. 100.000 digitalen Gattern und 46 Analogfeldern und über 400 I/O-Pads. Die Analogfelder sind mit optimierten Transistoren, Widerständen und Kapazitäten versehen, um Komparatoren, Operationsverstärker, A/D- und D/A-Wandler sowie Oszillatoren und andere Analogschaltungen realisieren zu können. Eine umfangreiche digitale Zellbibliothek bietet dem Entwickler Zugriff auf Logikgatter und komplexe Funktionen bis hin zum "PIC-kompatiblen" 8-Bit-Mikrocontroller-Kern.

Die technischen Daten der GFN-Chips entsprechen CMOSinternational üblichen Standards bei Prozessen. Die typische Betriebsspannung ist 3...5V, die Leistungsaufnahme liegt bei 4 uW/Gatter/MHz. Eingangssignale können bis zu einer Frequenz von 300MHz verarbeitet werden, Ausgangssignale bis zu 145 MHz. Die GFN-Chips des IMS decken alle üblichen Temperaturbereiche ab, einschließlich des erweiterten Einsatzbereichs bei -55° C...+125°C. Das heißt. IMS-Chips können für alle Einsatzbereiche qualifiziert werden. Durch die Zusammenarbeit mit internationalen Zulieferern können die Chips in einer breiten Palette von IC-Gehäusen montiert werden, vom einfachen Dual-Inline-Gehäuse über diverse SMD-Gehäuse bis hin zu ultrakompakten Ball-Grid-ArrayGehäusen, die nur unwesentlich größer sind, als der Chip selbst. Dass die Gehäuse den aktuellen Anforderungen nach Schadstoffarmut (RoHS-Konformität) entsprechen, versteht sich von selbst. Für Kleinserien und Muster können alle Chips in der hauseigenen Chipmontage in verschiedene Keramikgehäuse oder auch direkt auf Leiterplatten montiert werden.

#### 2. Ablauf einer Chipentwicklung

Die Schaltungsentwicklung für GATE FOREST-Chips kann vom Kunden weitgehend selbst durchgeführt werden; das IMS stellt dann entsprechende Zell-Bibliotheken für marktübliche Entwicklungsprogramme zur Verfügung. Es besteht auch die Möglichkeit, lediglich die Anforderungen an den Chip zu definieren und die gesamte Entwicklungsarbeit dem erfahrenen IMS-Team zu überlassen. Darüber hinaus gibt es auch die Option eines Einstiegs auf "halber Strecke", etwa, wenn der Kunde seine Schaltung auf der Basis eines feldprogrammierbaren Bausteins bereits erfolgreich selbst entwickelt hat und nun eine Umsetzung dieser Schaltung in einen ASIC wünscht. Die Entwicklung läuft immer strukturiert ab, jeder Arbeitsschritt wird dokumentiert und gegenüber dem Kunden transparent gemacht. Gemeinsame Freigabeprozeduren zwischen IMS und Kunden an allen entscheidenden Stellen im Entwurfsablauf stellen sicher, dass die Schaltung exakt den Kundenanforderungen entspricht. Grundsätzlich wird für jede Chipentwicklung am IMS ein interner Produktleiter benannt, der das gesamte Chip-Projekt für einen Kunden vom ersten Gespräch bis zur Serienfertigung begleitet.

#### 2.1. Von der Idee zur Spezifikation

Gemeinsam mit dem Kunden erstellt das IMS-Team eine Spezifikation, die die Schaltung des Chips sowie alle Randbedingungen (Chipgehäuse, Testmethode, Prüfstandards usw.) definiert. Eine unverbindliche und ausführliche Beratung des Kunden ermöglicht im Vorfeld die Klärung der Realisierbarkeit einer Schaltungsidee. Auf Wunsch wird die Machbarkeit in einer entsprechenden Studie dokumentiert. Sobald die Spezifikation festgelegt wurde, beginnt die eigentliche Entwurfsphase.

#### 2.2. Der Schaltungsentwurf

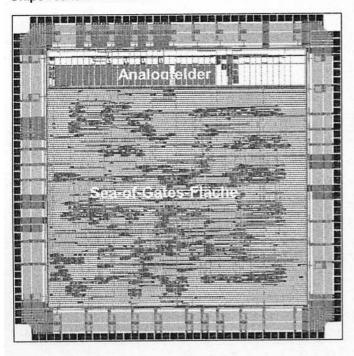

Digitale Schaltungsteile werden vorzugsweise in der Hardwarebeschreibungssprache VHDL beschrieben, simuliert und synthetisiert. Alternativ zu VHDL kann auch mit der Sprache Verilog gearbeitet werden. Die Synthese bezeichnet die automatische Umsetzung einer Schaltungsbeschreibung in eine ausgewählte Zieltechnologie, zum Beispiel in die des IMS GATE FOREST. Für analoge Komponenten kann auf die

umfangreiche Modulbibliothek des IMS zurückgegriffen werden, GATE FOREST Chips haben spezielle Flächen für Analogschaltungen, um eine hochgenaue Verarbeitung analoger Signale neben digitalen Schaltungen zu ermöglichen. Auch die analogen Komponenten werden vollständig simuliert, bevor sie gemeinsam mit dem eventuellen Digitalteil im Layout des Chips realisiert werden.

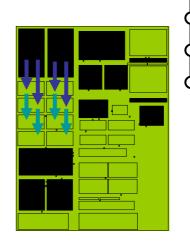

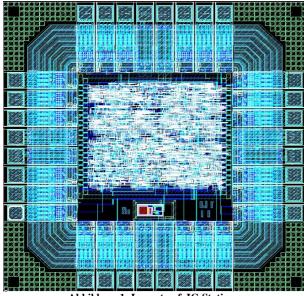

Typisches Layout eines GFN-Chips mit Analogfeldern im oberen Bereich und darunter der Sea-of-Gates-Fläche für Digitalschaltungen.

Parallel zur Erstellung des Chiplayouts werden umfangreiche Tests vorbereitet, die später den produzierten Chip auf Herz und Nieren prüfen, die Einhaltung der Spezifikation nachweisen und fehlerfreie Chip-Produkte garantieren. Für den Chip-Test werden so genannte Testmuster erzeugt, die den Chip in allen denkbaren Betriebszuständen aktivieren und die korrekte Funktion überprüfen. Diese Testmuster werden einerseits mit Hilfe der Synthesesoftware automatisch generiert, andererseits aber auch vom Schaltungsentwickler in Absprache mit dem Kunden als "Testbench" in VHDL beschrieben, um die spezifizierten Betriebszustände des Chips direkt testen zu können. Hierzu wird eine Testspezifikation erstellt, in der alle notwendigen "Test Cases" vereinbart werden.

Am Ende der Entwurfsphase erhält der Kunde den IMS-Designreport, in dem alle Entwurfsschritte nachvollziehbar und verständlich dokumentiert werden. Mit der Annahme des Designreports ist die Freigabe des Chip-Entwurfs durch den Kunden verbunden und stellt gleichzeitig den Startpunkt für die Herstellung des Chips dar.

#### 2.3. Die Chipproduktion

Das freigegebene Chiplayout ist die Basis für die automatische Erstellung der Fertigungsdaten. Mit den Fertigungsdaten wird dann einer der derzeit modernsten Elektronenstrahl-Schreiber, ein Leica SB350, im Reinraum des IMS angesteuert. Der Elektronenstrahl-Schreiber kann zur Anfertigung von Belichtungsmasken für die Waferfertigung genutzt werden.

Mit den Masken werden in weiteren Prozessschritten die Metall-Ebenen auf den Wafern hergestellt. Für Prototypen oder Kleinserien kann der Elektronenstrahl-Schreiber aber auch zur "Direktbelichtung" eines einzelnen Wafers verwendet werden. In diesem Fall werden die Strukturen der Metallebenen des Wafers direkt mit dem Elektronenstrahlschreiber belichtet. Man spart sich dann den zeit- und kostenaufwändigeren Weg über die Maskenherstellung.

Grundsätzlich ist die Maskenbelichtung jedoch bei der Herstellung mehrerer Wafer mit gleichen Chips ökonomisch sinnvoller, da die Fertigungszeiten bei Maskenbelichtung wesentlich kürzer sind, sobald die wieder verwendbaren Masken einmal hergestellt wurden. Die GATE FOREST Chips werden vollständig am IMS produziert. Durch die Zusammenarbeit mit dem Freiburger Chiphersteller MICRONAS kann das IMS eine zum IMS-Prozess kompatible Second Source anbieten, die die rasche Fertigung großer Produktionsvolumen erlaubt und die ohnehin hohe Verfügbarkeit der IMS-Chips auch bei eventuellen Produktionsstörungen sicherstellt.

### 2.4. Test, Gehäuseaufbau, Qualifizierung und Auslieferung

Sobald die Wafer mit den GATE FOREST Chips aus der Produktion kommen, werden sie von der IMS-Testabteilung mit den im Schaltungsentwurf erstellten Testmustern geprüft. Diese Wafer mit geprüften Chips kommen dann in die Chipmontage. Für die Bemusterung oder Klein- und Sonderserien werden die Chips im IMS unter Reinraumbedingungen in die gewünschten Keramikgehäuse verpackt. Serienprodukte mit Kunststoffgehäusen lässt das IMS bei qualifizierten Zulieferern in Europa und Asien verpacken.

Sind die verpackten Chips aus der Montage zurückgekehrt, werden sie erneut, in einem Bauelemente-Test, geprüft, um eventuelle Fehler bei der Chipmontage zuverlässig ausschließen zu können. Sobald erste Muster zur Verfügung stehen, bekommt der Kunde "seinen" ASIC erstmals in die Hand und kann ihn in der vorgesehenen Anwendung testen.

Parallel dazu führt die IMS-interne Qualitätssicherung laufend Untersuchungen über Lebensdauer und Zuverlässigkeit der produzierten Chips durch. Bei diesen "Torturen" werden die Bausteine unter extremen Be-

dingungen an die Grenzen in der Anwendung gebracht, um nachzuweisen, dass sie die strengen Qualitätsanforderungen des IMS erfüllen. Neben elektrischen Tests werden zyklische Temperaturwechsel, Feuchtigkeitstests und mechanische Untersuchungen durchgeführt. Diese und andere etablierte Qualitätsmaßnahmen spiegeln sich auch in den einschlägigen Standards wieder, nach denen die Entwicklung und Herstellung von IMS-Chips zertifziert ist: ISO9001 und DIN EN 100 114, letztere qualifiziert das IMS als "echten" Chiphersteller in Industriequalität.

#### 3. Innovative Ideen umsetzen

IMS GATE FOREST Chips sind eine ideale Plattform, um rasch und kostengünstig eigene Schaltungsideen zu realisieren. Ganz gleich, ob es um einige wenige Chips zu Forschungszwecken geht oder, ob eine konkrete Produktidee dahinter steht und der Chip das Potenzial zu einem Serienprodukt besitzt.

In vielen Unternehmen existieren viele innovative Ideen für neue Produkte. Oft scheitert die Realisierung an Hemmnissen wie hohen Entwicklungskosten für eigene Mikrochips oder einfach am fehlenden Knowhow, speziell bei der Anwendung neuer Nano- und Mikrotechnologien. Das IMS sieht es als seine Aufgabe an, Unternehmen bei der Umsetzung neuer Ideen zu unterstützen. Entwicklungsmitarbeiter von kleinen und mittleren Unternehmen können am IMS den so genannten "Walk-in-Service" nutzen und am IMS begleitet vom IMS-Team eigene Schaltungsentwürfe realisieren.

#### 3.1. IC-Lab Entwicklungsumgebung

Aus dem Gebiet der beruflichen Weiterbildung stammt das neue IC-Lab-Paket des IMS. Damit steht ein flexibles Starter-Kit zur Entwicklung integrierter Schaltungen mit modernsten Methoden kostengünstig zur Verfügung. Mit dem IC-Lab können komplexe Schaltungen beschrieben, simuliert und auf einem mehrfach programmierbaren FPGA-Baustein erprobt werden. Ist die Schaltungsidee dann soweit gereift, dass sie auf einem eigenen Mikrochip realisiert werden kann, steht die IMS GATE FOREST Chiptechnologie zur Verfügung und die FPGA-Schaltung kann in kurzer Zeit in ein ASIC-Design überführt werden.

#### 3.2. On-chip Sensorarrays

Die GATE FOREST-Strategie mit ihren einheitlich vorgefertigten Master-Wafern und der rasch und günstig durchführbaren Personalisierung hin zu kundenspezischen Chips ist eine etablierte und erfolgreiche Sparte im Angebot des IMS für Industrie und Forschung. Im Zuge der Weiterentwicklung des GATE FOREST zu einem 0,5µm-Prozeß entsteht eine

"Structured ASIC"-Plattform, welche bei gleicher Chipgröße neben wesentlich erhöhter Gatterkapazität auch dedizierte Bereiche für Sensorarrays bietet. Auf diesen Sensorarrays lassen sich zum Beispiel Detektoren für Licht und Magnetfelder direkt im Chip neben Schaltungslogik und analoger Signalaufbereitung integrieren – kompakte Mikrosysteme für industrielle Anwendungen.

Die Abbildung zeigt integrierte pn-Photodioden in CMOS-Technologie auf dem neuen 0,5µm GATE FOREST – Master.

#### 4. Integrierte Mikrosysteme

#### 4.1. Nanoschalter

Durch die enge Zusammenarbeit mit einigen jungen Unternehmen aus der Nano- und Mikromechanik rücken kleinste in Silizium gefertigte mechanische Komponenten verstärkt in den Fokus industrieller Anwendungen beim IMS. So ist das Institut beispielsweise an der Entwicklung mikromechanischer Schaltelemente beteiligt, die ihren Zustand stromlos speichern, jedoch durch Anlegen einer Steuerspannung "umprogrammiert" werden können. Diese im Grunde rein mechanischen Schalter sind so klein, dass sie als Arrays auf Chips integriert werden können und wie nichtflüchtige Datenspeicher einsetzbar sind. Untersuchungen zeigen, dass diese mikromechanischen Speicher erheblich robuster gegenüber externen Einflüssen sind, als zum Beispiel Speicherelemente auf der Basis von Flash-Technologien.

In Verbindung mit der bei GATE FOREST Chips realisierbaren Robustheit gegen Strahlung und elektro-

magnetischen Feldern eröffnen sich völlig neue Anwendungen für solche robusten Mikrosysteme. Dies gilt insbesondere bei Anwendungen unter extremen Bedingungen wie etwa in der Raumfahrt.

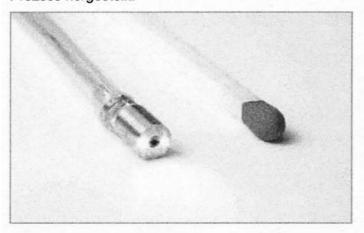

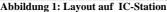

#### 4.2. Welt-kleinste Endoskopkamera

Nicht nur im High-End-Bereich sind solche Mikrosysteme interessant. Gerade auch bei Anwendungen, die bisher mit sehr teuren Spezialgeräten realisiert wurden, lassen sich Mikrosysteme schon sehr bald als preiswerte Alternative realisieren. So hat das IMS-Team im Rahmen eines Verbundforschungsprojektes die derzeit kleinste Endoskopkamera vorgestellt, die künftig als "bildgebendes Einweg-Endoskop" Medizinern völlig neue Diagnosemöglichkeiten geben könnte. Auf einem Chip mit nur 1.8 mm Durchmesser wurde ein Videosensor mit 40.000 Pixeln verwirklicht. Der Chip wurde komplett am IMS entwickelt und in einer externen Fertigungsstätte in einem 0,25µm-CMOS-Prozess hergestellt.

Die IVP1-Endoskopkamera im Vergleich mit einem Streichholz. Der Endoskopkopf enthält einen IMS HDRC-Farbsensor und zwei Lichtquellen.

Für praktische Versuche wurde der Mini-Bildsensor auf einer 2x3 mm² kleinen Platine direkt montiert und auf der Rückseite der Anschluss der Versorgungsund Datenleitungen realisiert. Weitere Forschungen im Bereich Aufbau- und Verbindungstechnik laufen am IMS, um kostengünstige und zuverlässige Methoden der Verbindung solcher Winzlinge mit der Außenwelt weiterzuentwickeln.

#### 4.3. Drahtlose Mikrosysteme

Neben drahtgebundenen Mikrosystemen drängen sich immer mehr die drahtlosen Systeme in den Vordergrund. Ein bekanntes Beispiel sind die schlagzeilenträchtigen RFID-Tags, die als drahtlos auslesbare Identifikationsmöglichkeit schon sehr bald viele Logistikaufgaben in Handel und Industrie dominieren werden. Auch komplexere drahtlose Mikrosysteme werden realisierbar: zum Beispiel drahtlos ansprechbare

Sensoren, die in Autoreifen laufend den Druck messen und bei gefährlichem Druckabfall eine Alarmmeldung erzeugen. Ebenso sind Sensoren denkbar, die in Bauteilen von Gebäuden fest eingebaut sind und laufend Druck, Temperatur und Kräfte messen, die aus der Distanz drahtlos erfassbar sind.

#### Zusammenfassung

Das Institut für Mikroelektronik Stuttgart versteht sich als Partner für kleine und mittelständische Anwender bei der Umsetzung von Schaltungskonzepten von der Idee bis zum Chip in Industriequalität. Über 300 Kunden mit teils langjährigem Kontakt zum IMS wissen das zu schätzen. Die qualifizierten hauseigenen CMOS-Prozesse bieten eine breite Basis für ASICs und integrierte Mikrosysteme in den Bereichen Digitaltechnik, Mixed-Signal und hochwertigen Sensoranwendungen. Durch die enge Kooperation mit anderen Foundries wie Micronas stehen sowohl Second Source-Fertigungslinien als auch Sonderprozesse für Bildsensoren und Smartpoweranwendungen zur Verfügung.

Ausführliche Informationen sind im Internet zu finden.

#### www.ims-chips.de

#### Über die Autoren

Prof. Dr.-Ing. Joachim Burghartz leitet seit Oktober 2005 das Institut für Mikroelektronik Stuttgart (IMS CHIPS). Davor war er sieben Jahre lang an der TU Delft tätig, wobei er von 2001 bis 2005 Wissenschaftlicher Direktor des Forschungsinstituts DIMES war. Dem ging eine elfjährige Tätigkeit bei IBM am T. J. Watson Research Center in New York in verschiedenen Funktionen voraus. Er promovierte 1987 zum Dr.-Ing. an der Universität Stuttgart und erhielt den Dipl.Ing. Grad 1982 von der RWTH Aachen.

Dipl.-Ing.(FH) Thomas Deuble studierte an der FH Ravensburg-Weingarten und ist seit 1997 Produktmanager ASICs im Geschäftsfeld Systeme am IMS und betreut Kundenprojekte sowie Förderprojekte im Bereich Chipentwicklung.

#### Simulation und Layout eines schnellen CMOS-Serializers

Christian Bradler, Prof. Dr.-Ing. H.-P. Bürkle

Hochschule Aalen, Beethovenstr. 1, 73430 Aalen

Tel. 07361 / 576 - 240, Fax 07361 / 576 - 324

christian.bradler@gmx.de, heinz-peter.buerkle@htw-aalen.de

Im Rahmen eines Projekts zur Entwicklung von LVDS-Zellen wurde ein schneller CMOS-Serializer bis zum Chip-Layout entwickelt. Dazu wurde zunächst eine eigene Bibliothek von Standardzellen erstellt und dann im Serializer verwendet. Langsame stromsparende Zellen und schnelle Zellen ermöglichen eine gute Balance zwischen Geschwindigkeit und Leistungsverbrauch. Inhalt der hier vorgestellten Arbeit ist die systematische Darstellung der Layoutentwicklung und eine Systemsimulation mit innerhalb des Projekts bereits erstellten Zellen.

#### 1. Einleitung

Die vorliegende Arbeit über einen schnellen Serializer entstand im EDA-Zentrum der Hochschule Aalen im Zusammenhang eines Testchipprojektes, das sich mit dem Entwurf von LVDS-Zellen für die Technologie von IHP Microelectronics [1] befasst. (IHP: Innovation for High Performance, Frankfurt/Oder). LVDS steht für Low Voltage Differential Signaling und ist ein digitaler Schnittstellenstandard, der lediglich auf der physikalischen Schicht spezifiziert ist [2]. Niedrige Spannungshübe (maximal 400mV) sorgen für geringen Leistungsverbrauch und hohe Bitraten, der Gegentaktbetrieb (Differential Mode) bewirkt eine minimale Störaussendung und geringen Einfluss von (Gleichtakt)-Störungen auf das LVDS-Signal.

Anwendung findet LVDS heute zunehmend für schnelle serielle Übertragung auf der Leiterplatte, da parallele Bussysteme aufgrund endlichen der Ausbreitungsgeschwindigkeit der Signale 20cm/ns) schon heute im Bereich mehrerer GBit/s oft an ihre Grenzen stoßen (Laufzeitversatz aufgrund der unterschiedlichen Leitungslängen, Reflexionen und Überkoppeln zwischen eng benachbarten Leitungen). Aktuelle Einsatzgebiete für LVDS sind PCI-Express, DVI, RapidIO, FireWire, SCSI und S-ATA. Darüber hinaus denkt man auch daran LVDS Kommunikation zwischen Subsystemen On-Chip zu verwenden. Daher spielt LVDS auch für die System-On-Chip (SoC) Integration eine große Rolle.

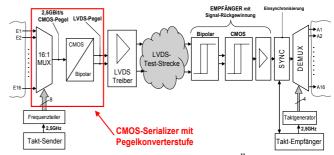

#### 1.1. Gesamtprojekt

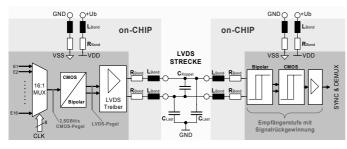

Abbildung 1 zeigt das Gesamtprojekt. Neben LVDS-Leitungstreiber (der aus einer Weiterentwicklung von [3] entstand) und Empfängereingangsstufe [4] sind der Parallel-Seriell-Wandler ("Serializer") und der Seriell-Parallel-Wandler ("Deserializer") besonders wichtig. Daneben werden noch Schaltungen zur Erzeugung der Takte benötigt (Phasenregelschleife PLL mit Frequenzteiler). Im Empfänger muss zudem eine Abtastung des Signals zum Zeitpunkt mit maximaler Augenöffnung (Retiming) und eine Synchronisation zum Sender vorgenommen werden, damit die einzelnen Signale nach dem Deserializer wieder auf den richten Leitungen erscheinen.

Abbildung 1 Gesamtsystem zur LVDS-Übertragung

Der aktuelle Stand der Entwicklung des Gesamtprojekts umfasst Leitungstreiber, Empfänger, Deserializer und erste Blöcke zur Erzeugung der notwendigen Takte. Als Ziel für die Bitrate werden 2.5GBit/s angestrebt.

#### 1.2. Technologie

Als konkrete Technologie liegt ein Prozess von IHP Microelectronics vor [1]. Es handelt sich hierbei um einen  $0.25\mu m$  SiGe:C-HBT-BiCMOS Mixed-Signal Prozess. Zur Erfüllung höchster Anforderungen bezüglich Geschwindigkeit und Rauschen können auch Silizium-Germanium-Hetero-Bipolartransistoren verwendet werden. Aufgrund der Minimierung der Chipffläche und der elektrischen Leistungsaufnahme wird man jedoch bestrebt sein, die CMOS Technologie so weit als irgend möglich einzusetzen. Daher finden im hier behandelten Serializer, anders

als in Leitungstreiber und Empfängereingangsstufe, keine SiGe-HBTs Verwendung.

#### 2. Entwurf des Serializers

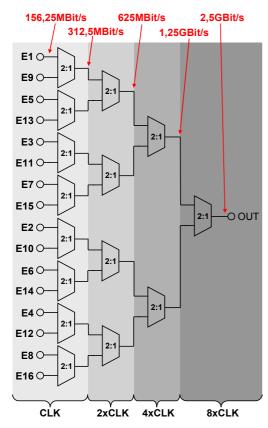

Zielvorgabe für den Schaltungsentwurf ist ein 16:1 Serializer, der eine Bitrate von mindestens 2.5GBit/s am Ausgang aufweist.

#### 2.1. Schaltungskonzept

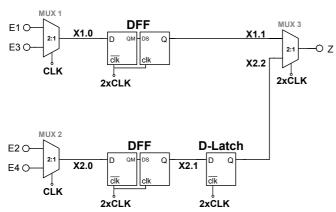

Die Schaltungsidee basiert auf einer geradlinigen hierarchischen Struktur elementaren aus Multiplexern mit vier Taktbereichen (Abbildung 2). Hierfür lässt sich ein besonders einfacher eines Taktgenerator mittels Frequenzteilers realisieren. Der Serializer enthält damit sowohl langsame als auch schnell getaktete Schaltungsteile. Damit die Schaltung stromsparend ausgelegt werden kann, ist es ratsam einen langsamen MUX am Eingang und einen schnellen MUX am Ausgang einzusetzen. Da bei den 2:1 Multiplexern sowohl der jeweilige originale Takt als auch der invertierte Takt genutzt werden, reicht als Maximaltakt der 8-fache Basistakt aus, sofern man am Ausgang der letzten Stufe das Signal nicht abtasten muss.

Abbildung 2 Serializer Schaltungskonzept

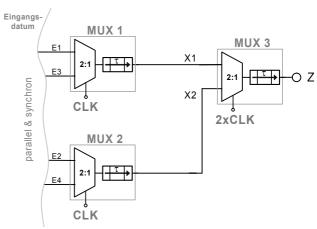

### 2.2. Synchronisation der Multiplexerstufen

Aufgrund von Laufzeiten müssen die Multiplexerstufen synchronisiert werden. Andernfalls kommt es zu Laufzeitkonflikten, wie nachfolgend dargestellt: Abbildung 3 zeigt ein Modell, das die Laufzeiten der Multiplexerstufen berücksichtigt. Der nachgeschaltete MUX3 erwartet das Signal X1 zu einem Zeitpunkt, bei dem noch kein neues Datum aufgrund der realen Verzögerungszeit des davor geschalteten MUX1 anliegen kann. Daraus ergeben sich die in Abbildung 4 dargestellten Laufzeitkonflikte.

Abbildung 3 Laufzeitmodell einer Teilschaltung

Abbildung 4 Impulsdiagramm mit Darstellung der Laufzeitkonflikte

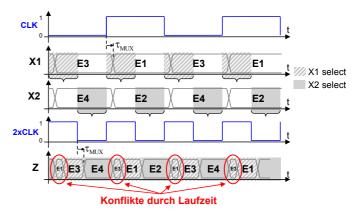

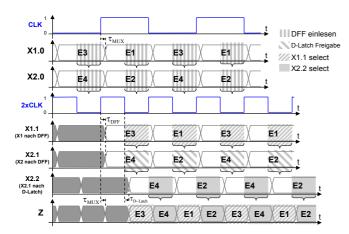

Um dieses Problem zu lösen, müssen die Eingangssignale am MUX3 rechtzeitig bereitgestellt werden. Abhilfe kann durch folgende Schaltungsmaßnahme geschaffen werden (Abbildung 5). Nach jeder Multiplexerstufe werden taktzustandsgesteuerte Doppelspeicherflipflops (DFF) eingesetzt, die mit der doppelten Taktfrequenz des davor geschalteten Multiplexers angesteuert werden. Die Signale X1.0 und X2.0 werden darauf eindeutig in einem gültigen Zustand abgetastet. Im unten dargestellten Signalpfad sorgt ein D-Latch dafür, dass das Signal um eine halbe Taktperiode des schnellen Taktes (bzw. um ein

Viertel der Basistaktperiode) verzögert wird. Somit steht am Eingang des nachfolgenden MUX3 abwechselnd auf den beiden Zweigen jeweils ein stabiles Signal zur Verfügung, das an den Ausgang Z weitergereicht werden kann. Das Impulsdiagramm hierzu zeigt Abbildung 6.

Abbildung 5 Schaltungsmodell zur Lösung der Laufzeitkonflikte

Abbildung 6 Impulsdiagramm der synchronisierten Multiplexerschaltung

#### 3. Entwurf von Standardzellen

Die benötigten Zellen zum Aufbau des Multiplexers wurden als Standardzellen entworfen. Die im Design-Kit vorhandene Standardzellen-Bibliothek kann keiner Extraktion parasitärer Komponenten unterzogen werden, da die Layouts zum Schutz von Intellectual Property lediglich als so genannte "Abstracted View" zur Verfügung stehen. Um eine möglichst exakte Simulation auch der parasitären Effekte nach dem Layout zu erhalten, wurden die für den Multiplexer relevanten Zellen neu entworfen. Dies hat zudem den Vorteil, dass die Zellen bezüglich Geschwindigkeit und Stromverbrauch für diese spezielle Applikation optimiert werden konnten.

### 3.1. Schaltplan und Layout der Standardzellen

Die folgenden Schaltungen sind für den Aufbau eines 16:1-MUX notwendig: 2:1-Multiplexer-Zellen, D-Latch Speicherzellen und Doppelspeicher-Flip-Flop-Zellen (DFF). Da die Geschwindigkeitsanforderungen je nach Multiplexerstufe (Anordnung am Eingang oder Ausgang) recht unterschiedlich sind, wurden sowohl langsame und somit stromsparende Standardzellen, sowie schnelle Varianten entworfen.

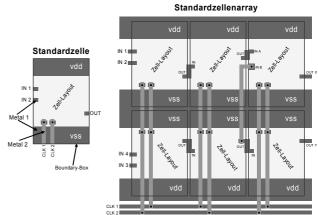

Den prinzipiellen Layoutaufbau der entworfenen Standardzellen und deren Anordnung in einem Array zeigt Abbildung 7. Die Zellen werden an der Horizontalen gespiegelt. Dadurch können die Stromversorgungspfade besonders platzsparend ausgeführt werden. Die Taktsignale werden über Takt-leitungspfade herangeführt.

Abbildung 7 Schematische Darstellung der Standardzellen und Standardzellenarray

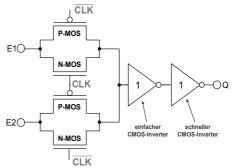

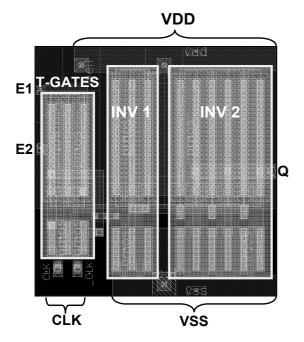

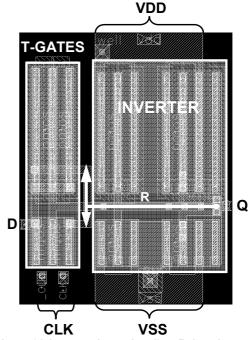

Es erfolgt nun eine kurze Beschreibung der entwickelten Standardzellen: Der elementare Multiplexer (hier in Abbildung 8 als schnelle Variante) besteht aus jeweils einem Transmission-Gate an jedem Eingang, die im Gegentakt durchgeschaltet werden. Anschließend übergibt ein einfacher CMOS-Inverter einem nachgeschalteten schnellen Inverter das gemultiplexte Signal.

Abbildung 8 Schaltplan schnellen Multiplexerzelle

Die Umsetzung dieser Schaltung in ein Layout zeigt Abbildung 9. Dieses Layout wurde einer Extraktion parasitärer Komponenten unterzogen und neu simuliert. Den transienten Spannungsverläufen wurden die charakteristischen Laufzeiten sowie die Anstiegs- und Abfallzeiten entnommen und vergleichend für Schematic- und Analog-Extracted-Simulation in die Tabelle (Abbildung 10) eingetragen. Man erkennt einen geringfügigen Einfluss des Layouts.

Abbildung 9 Layout der schnellen Multiplexerzelle

| Messwert                                                           | Schematic-Simulation             |                     | Analog-E<br>Simul           |                     |

|--------------------------------------------------------------------|----------------------------------|---------------------|-----------------------------|---------------------|

| Eingang A<br>(Signallaufzeit)                                      | $T_{01} = 189 ps$                | $T_{10} = 184 ps$   | $T_{01} = 202ps$            | $T_{10} = 198 ps$   |

| Eingang B (Signallaufzeit)                                         | $T_{01} = 189 ps$                | $T_{10} = 184 ps$   | $T_{01} = 204 ps$           | $T_{10} = 198 ps$   |

| Clock-To-<br>Output-Delay $(T_{co})$                               | $T_{co01} = 201ps$               | $T_{co10} = 196 ps$ | $T_{co01} = 219 ps$         | $T_{co10} = 214 ps$ |

| Anstiegszeit (T <sub>rise</sub> )                                  | $T_{rise} = 62ps$                |                     | T <sub>rise</sub> =         | 71ps                |

| Abfallzeit<br>( T <sub>fall</sub> )                                | $T_{\text{fall}} = 52 \text{ps}$ |                     | $T_{\rm fall} = 60 { m ps}$ |                     |

| Zusammenfassung: $	au_{MUX} = 220 ps$ (Maximale Zeit $T_{COmax}$ ) |                                  |                     |                             |                     |

Abbildung 10 Charakteristische Zeiten für Signale an der schnellen Multiplexerzelle

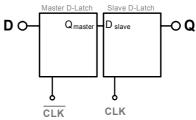

Die anderen Zellen werden hier nun weniger ausführlich beschrieben. Abbildung 11 und Abbildung 12 zeigen Schaltplan und Layout der schnellen D-Latch-Speicherzelle.

Abbildung 11 Schaltplan schnelles D-Latch

Das D-Latch besteht aus einem Transmission-Gate am Eingang, sowie einem Transmission-Gate im Rückkopplungspfad. Zwei Inverter, die in Serie geschaltet sind, sorgen für einen steilen Pegel am Ausgang sowie für die erforderliche Laufzeit vom Eingang zum Ausgang.

Abbildung 12 Layout des schnellen D-Latch

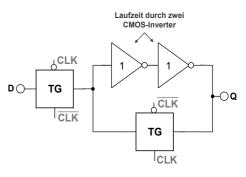

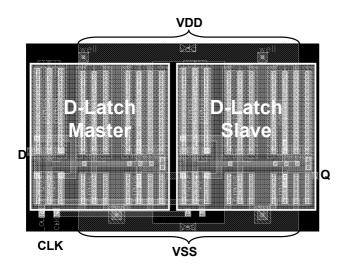

Das Doppelspeicher-Flipflop wird als Master-Slave-Flipflop aus zwei hintereinander geschalteten D-Latch-Zellen, die zueinander mit invertierten Takten betrieben werden (Abbildung 13, Abbildung 14), realisiert.

Abbildung 13 Schaltplan des schnellen DFF

Abbildung 14 Layout des schnellen DFF

### 3.2. Evaluation der entwickelten Standardzellen

Die Standardzellen wurden zunächst auf Schaltplanebene simuliert und optimiert. Nach der Layouterstellung wurden die parasitären Elemente extrahiert und in eine Post-Layout Simulation eingebunden. Diese Simulationswerte flossen dann in das Laufzeitmodell ein. Daraus lassen sich die folgenden Aussagen für die einzelnen Komponenten hinsichtlich ihrer Geschwindigkeit treffen:

| Zeit                          | Zeit<br>(analog-<br>extracted) | maximale<br>Basisfrequenz | schnellster<br>Takt (8xCLK) | maximale<br>Übertragungsrate |

|-------------------------------|--------------------------------|---------------------------|-----------------------------|------------------------------|

| $\tau_{MUX}$                  | 220 ps                         | 284 MHz                   | 2,272 GHz                   | 4,544 GBit/s                 |

| τ <sub>Latch</sub>            | 205 ps                         | 305 MHz                   | 2,44 GHz                    | 4,88 GBit/s                  |

| $\tau_{DFF}$                  | 190 ps                         | 329 MHz                   | 2,632 GHz                   | 5,264 GBit/s                 |

| t <sub>Setup</sub><br>D-Latch | 162 ps                         | 355 MHz                   | 2,84 GHz                    | 5,68 GBit/s                  |

| t <sub>Setup</sub><br>DFF     | 150 ps                         | 338 MHz                   | 2,704 GHz                   | 5,408GBit/s                  |

Abbildung 15 Zusammenstellung der kritischen Zeiten für Multiplexer (MUX), D-Latch und DFF und der dadurch jeweils limitierten Übertragungsrate.

Abbildung 15 zeigt, dass die am stärksten begrenzende Zeit die Laufzeit der Multiplexerzelle ist. Diese erlaubt eine maximale Übertragungsrate von ca. 4.5GBit/s. Da lediglich 2.5GBit/s anvisiert wurden, erfolgten an dieser Stelle keine weiteren Optimierungen mehr.

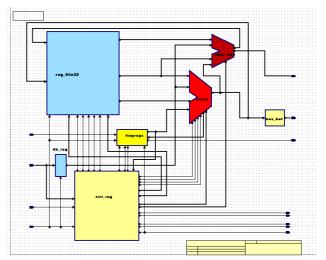

### 4. Layoutentwicklung des gesamten Serializers

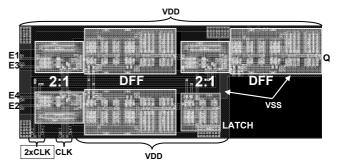

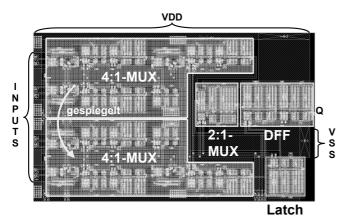

Insgesamt sieben Basiszellen bilden den 4:1-Multiplexer (in Abbildung 16 dargestellt). Er besteht aus drei elementaren 2:1 Multiplexerzellen mit den jeweils nachgeschalteten Doppelspeicher-Flip-Flops und einem D-Latch am Ausgang.

Abbildung 16 Layout des 4:1 Multiplexers

Die Anordnung dieser Zellen im Layout sollte so erfolgen, dass die Standardzellen-Designregeln eingehalten werden können.

Um den Stromversorgungspfad VSS gemeinsam nutzen zu können, werden die unteren Basiszellen an der Horizontalen gespiegelt, so dass der VSS-Anschluss nach oben herausgeführt wird. Zwischen dem VSS-Stromversorgungspfad wird ein Taktleitungspfad geführt, der die Multiplexer- und DFF-Zellen mit dem benötigten Takt versorgt. Der Ausgang des D-Latches wird über die Metall2 Verdrahtungsebene an den oberen E2-Eingang des letzten 2:1-MUX herangeführt.

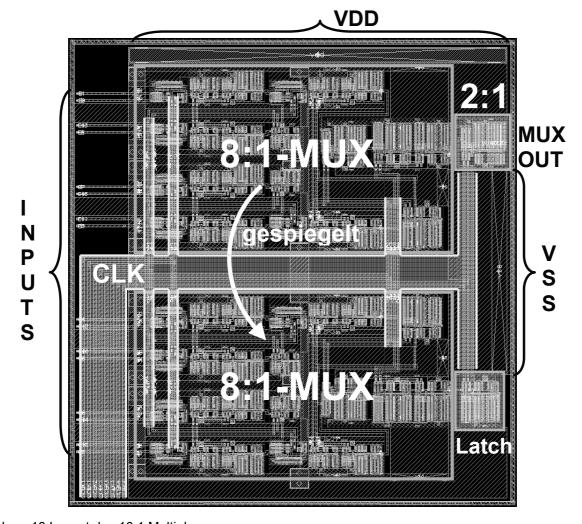

Für die 8:1-Multiplexerzelle (Abbildung 17) werden zwei komplexe 4:1-Multiplexerzellen miteinander verschaltet. Das Ausgangsignal der beiden 4:1-MUX-Zellen wird abermals an einen 2:1-MUX geführt. Die zweite 4:1-Multiplexerzelle in der unteren Bildhälfte ist zur anderen Zelle horizontal gespiegelt. Die Taktleitungen CLK1 und CLK2 können daher vertikal über das Zelllayout hinweg durch den Metal2 Layer verdrahtet werden. Ab hier wird erstmals in diesem Entwurf die schnelle 2:1-MUX-Zelle mit nachfolgendem schnellen DFF eingesetzt, da das DFF schon mit dem achtfachen Basistakt (CLK4) getaktet wird. Für das D-Latch wird ebenfalls die schnelle Variante verwendet. Es ist ein deutlicher Flächenbedarfsunterschied zwischen langsamen schnellen Zelltypen zu sehen. Die schnellen Varianten beanspruchen fast das Doppelte an Chipfläche, als die einfachen Standardzellen.

Abbildung 17 Layout des 8:1 Multiplexers

Der Aufbau der 16:1 MUX-Zelle erfolgt analog zu der 8:1-MUX-Zelle. Das Ausgangssignal kann direkt, d.h. ohne eine Einsynchronisierung mit dem nachfolgenden (hier nicht betrachteten) CMOS/Bipolar-Pegelkonverter verbunden werden. Der schnelle 2:1-

Multiplexer ist also dafür ausgelegt, eine nachfolgende Konverterstufe treiben zu können. Auch hier wurde die zweite 8:1-Multiplexerzelle an der Horizontalen nach unten gespiegelt. Zwischen den beiden 8:1 MUX-Zellen wird nun ein wenig mehr Platz für einen Taktleitungspfad gelassen, der die Taktleitungen der kompletten Schaltung zusammenfasst.

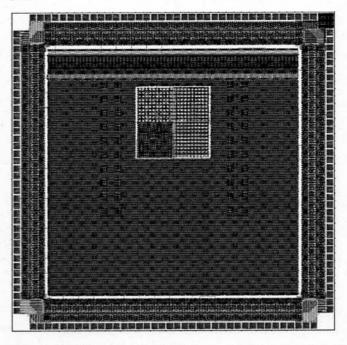

Eine übersichtliche Darstellung des kompletten Multiplexerlayouts ist in Abbildung 18 gezeichnet. Um das komplette Layout herum wurde ein Graben aus Metall1 Substratkontaktierungen gezogen, um Störeinkopplungen von innen nach außen und umgekehrt zu vermeiden. Die Substratkontaktierungen werden auf die negative Betriebsspannung (VSS) gelegt. Die Kontaktierung der positiven Betriebsspannung (VDD) erfolgt von oben über den Metall2 Layer. Sämtliche Signalleitungen müssen ebenfalls durch den Metall2 Layer von außen angeschlossen werden, um über die Metall1 Substratkontaktierungen zu gelangen.

Abbildung 18 Layout des 16:1 Multiplexers

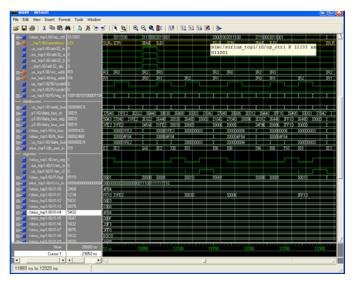

#### 5. Teilsystem-Simulation

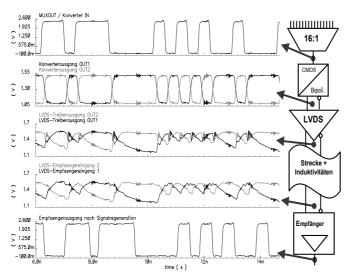

Der 1:16 Serializer wurde in einer Teilsystemsimulation zusammen mit anderen Komponenten durch eine Postlayout-Simulation einschließlich extrahierter parasitärer Elemente verfiziert. Der im Rahmen dieser Arbeit entwickelte Serializer befindet sich am Eingang. Danach folgt ein Pegelkonverter von CMOS auf LVDS, anschließend der LVDS-Leitungstreiber, die Übertragungsstrecke, Empfänger-Eingangsstufe mit LVDS-Abschluss und Flankenregeneration sowie eine Pegelkonvertierung nach CMOS. Die Simulation erfolgte einschließlich der parasitären Bondinduktivitäten für die Eingänge der Spannungsversorgung sowie die Ein- und Signalleitungen. Ausgänge der Die LVDS-Übertragungsleitung auf der Platine wurde durch eine Kapazität nach Masse für jede der beiden Gegentakt-LVDS-Leitungen sowie eine Koppelkapazität zwischen den beiden Leitungen erfasst.

Abbildung 19 Teilsystemsimulation der LVDS-Übertragungstrecke

Abbildung 20 Simulationsergebnis (Postlayout)

Als Zahlenwerte für die hier beispielhaft dargestellte Simulation wurde für die Leitungskapazität jeweils 7pF, als Koppelkapazität zwischen den Leitungen 0.7pF und als Bondinduktivität 0.5nH angenommen. Anhand der Postlayout-Simulation in Abbildung 20 sieht man überlagerte Störungen, die sich auch auf die Ausgangspegel des CMOS/Bipolar-Pegelkonverters auswirken. Da aber die Auswertung der LVDS-Signale immer differentiell erfolgt, spielen diese relativ kleinen Gleichtaktstörungen keine Rolle.

Der Leitungstreiber ist offensichtlich hier an seiner Belastungsgrenze. Im Augendiagramm am Ausgang der LVDS-Treiberstufe ergäbe sich lediglich eine geringe Augenöffnung. Trotzdem kann der Empfänger aufgrund seiner empfindlichen bistabilen Eingangsstufe die Impulsform wieder regenerieren. Das Eingangs- und Ausgangsignal stimmt somit - bis auf eine Verzögerungszeit - logisch überein.

#### 6. Ergebnis und Ausblick

Als Ergebnis lässt sich festhalten, dass gemäß der durchgeführten Post-Layout-Simulationen mit der entwickelten Schaltung eine Datenrate von bis zu 4.5GBit/s möglich ist. Die Datenrate übersteigt dabei bei weitem die angestrebten 2.5GBit/s. Andere Schaltungsteile kommen nur wenig über diese Datenrate hinaus, so dass der Serializer nicht die eigentliche Begrenzung des Designs darstellt. Da der Prozess inzwischen abgekündigt wurde, muss vor einer Fertigung des Schaltkreises auf den Nachfolgeprozess umgestellt werden, der jedoch im Wesentlichen dem für das Design verwendeten Prozess entspricht.

#### 7. Literatur

- [1] http://www.ihp-ffo.de

- [2] ANSI/TIA/EIA-644-A

- [3] I. Kurz, H.-P. Bürkle: Entwurf eines LVDS-Leitungstreibers für On-Chip-Kommunikation, Multiprojekt-Chip-Gruppe Baden-Württemberg: MPC-Workshop. - Ulm: Fachhochsch. 2004, Juli, Albstadt-Sigmaringen

- [4] I. Kurz: Entwicklung eines integrierten LVDS-Empfängers mit Phasenregelkreis für eine Datenrate von 2.5GBit/s, Diplomarbeit an der Hochschule Aalen, 2005

#### Designstudie für einen 10 Bit-Analog-Digital-Umsetzer

Michael Diebold\*, Arnold Erni\*, Karl Hofmann\*, Gerhard Forster\*

\*AIM INFRAROT-MODULE GmbH, Söflinger Straße 100, 89077 Ulm \*Fachhochschule Ulm, Prittwitzstraße 10, 89075 Ulm

MichaelDiebold@gmx.de, Forster@fh-ulm.de

In Zusammenarbeit mit der Firma AIM INFRAROT-MODULE GmbH wurden an der Hochschule Ulm zwei unterschiedliche Konzepte für einen AD-Umsetzer zur Anwendung in infrarot-optischen Sensoren untersucht. Ziel ist es, Sensorik und Datenverarbeitung einschließlich des AD-Umsetzers später auf einem Chip zu integrieren, um geringe Baugröße, geringen Energieverbrauch und hohe Zuverlässigkeit zu erreichen. Die Spezifikation für den AD-Umsetzer sieht eine Auflösung von 10 Bit bei einer Abtastrate von 20 MS/s vor. Die Realisierung ist in Form eines IP-Cores auf Basis der 0,35 µm CMOS-Technologie von AMS vorgesehen. Die Simulation mit Cadence zeigt, dass eine der beiden Schaltungstopologien die Spezifikation mit vertretbarem Aufwand an Chipfläche und Verlustleistung erfüllt.

#### 1. Einleitung

Aus der Literatur ist eine Vielzahl von AD-Umsetzern bekannt [1, 2, 3]. Sie lassen sich grob in drei verschiedene Kategorien aufteilen:

- Parallelverfahren

- Wägeverfahren

- Zählverfahren

Der Vorteil des Parallelverfahrens liegt in der Erreichbarkeit hoher Abtastraten. Nachteilig ist, dass ein erheblicher Platzbedarf benötigt wird und nur eine geringe Auflösung erreicht werden kann. Mit dem Zählverfahren hingegen erreicht man eine hohe Auflösung bei einem geringen Platzbedarf, dafür aber nur kleine Abtastraten. Somit entschied man sich für den Mittelweg, das Wägeverfahren. Aus dieser Kategorie wurden zum Vergleich zwei verschiedene AD-Umsetzer entwickelt, ein zyklischer AD-Umsetzer nach dem RSD-Verfahren (Redundant Signed Digit) und ein AD-Umsetzer nach dem Prinzip der sukzessiven Approximation, auf den im vorliegenden Bericht detaillierter eingegangen wird.

#### 2. RSD-Verfahren

Das RSD-Verfahren wurde in den 90iger Jahren entwickelt [4]. Somit ist es ein sehr neues Verfahren, das auf einem speziellen Algorithmus beruht.

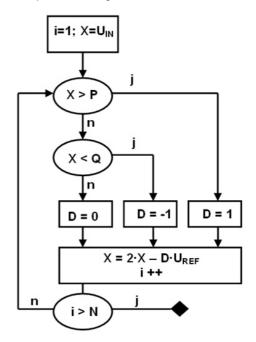

Abb.1 Signalflussplan des RSD Verfahrens

In Abb.1 ist der Signalflussplan des RSD-Verfahrens dargestellt. Zuerst wird die Variable X mit der Eingangsspannung versehen. Danach durchläuft die Variable X zwei Schwellen. Abhängig davon wird das Bit D gesetzt. Nach Beendigung des Vergleichs und Neuberechnung von X wird entschieden, ob ein weiterer Zyklus durchlaufen wird. Bei einer 10 Bit-Auflösung benötigt man somit 10 Schleifendurchläufe. In Abb.2 ist das Blockdiagramm des RSD Verfahrens dargestellt. Das Abspeichern der Eingangsspannung erfolgt durch eine Sample and Hold-Schaltung. Der darauf folgende Vergleich mit zwei Schwellen wird mit zwei Komparatoren realisiert. Das Ergebnis der Komparatoren ist gleichzeitig die Ausgangsbitfolge für einen Addierer. Danach wird der Algorithmus aktiv.

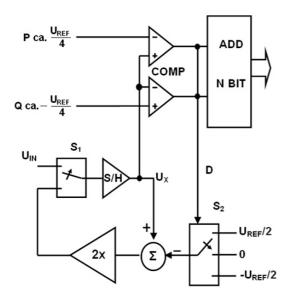

Abb.2 Blockdiagramm des RSD Verfahrens

Dieser Algorithmus,  $X = 2 \cdot X \cdot D \cdot U_{REF}$ , wird durch den Schalter S<sub>2</sub>, einer Summation und einer Verstärkung um den Faktor 2 realisiert. Der neu berechnete Wert wird wiederum in der Sample and Hold-Schaltung gespeichert, woraus eine neue Abtastung erfolgt. Dies wird solange durchgeführt, bis eine Auflösung von 10 Bit erreicht ist.

Der Vorteil dieses Verfahrens ist, dass der AD-Umsetzer einen geringen Platzbedarf benötigt (unabhängig von der Auflösung) und die Komparatoren unkritisch hinsichtlich ihrer Offset- Anforderung sind. Der Nachteil liegt bei der Multiplikation mit dem Faktor 2, da diese die Linearität (INL und DNL) bestimmt. Um die Auflösung von 10 Bit zu erzielen, muss der Verstärker innerhalb kurzer Zeit auf einen Spannungswert einschwingen, der weniger als 1 ‰ Gesamtfehler aufweist.

Mit einem einzelnen zyklischen AD-Umsetzer wurde eine Abtastrate von 500 kS/s bei einer Auflösung von 10 Bit erreicht. Durch ein Pipeline-Verfahren mit mehreren solcher AD-Umsetzer lässt sich die Abtastrate vergrößern. Bei diesem Verfahren wird die Schleife des zyklischen AD-Umsetzers an der S/H-Schaltung aufgetrennt und auf den nächsten AD-Umsetzer geführt, so dass jeder AD-Umsetzer ein Bit abhandelt. Somit werden 10 AD-Umsetzer, bei einer 10 Bit-Auflösung, in Reihe geschaltet. Dadurch wird eine Abtastrate von 5 MS/s erreicht, was der Spezifikation allerdings noch nicht entspricht.

In der Simulation zeigte sich, dass bei der vorgegebenen Technologie die geforderte Spezifikation mit dem RSD-Verfahren nur mit hohem Aufwand an Fläche und Verlustleistung zu erreichen ist.

#### 3. SAR-Verfahren

Das Verfahren nach der sukzessiven Approximation (SAR-Verfahren) ist altbekannt für seine Einsatzmöglichkeit bei mittleren Anforderungen an Abtastrate und Auflösung. Wegen seiner Empfindlichkeit, vor allem gegenüber Offsetspannungen, kann dieses Verfahren nur dann in einer CMOS-Technologie realisiert werden, wenn aufwändige Methoden der Selbstkalibration eingesetzt werden.

#### 3.1. Gesamtsystem

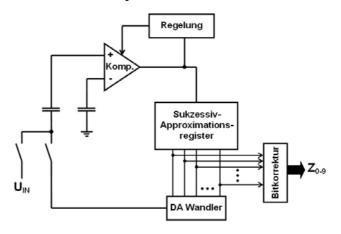

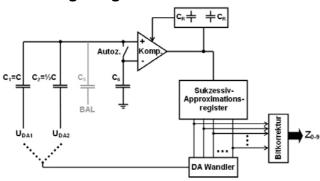

Abb.3 Blockdiagramm des SAR Verfahrens

Der Grobablauf des Verfahrens soll an Abb.3 erklärt werden. Die Eingangsspannung  $U_{IN}$ , (z. B.  $U_{IN} = 0.7$ V) wird über eine Sample and Hold-Schaltung abgespeichert. Diese wird hier mit einem Schalter und Kondensator dargestellt. Gleichzeitig wird ein Abgleich durchgeführt, der die beiden Eingänge des Komparators kurzschließt und gemeinsam auf eine Referenzspannung von z.B. 1 V legt. Somit wird die Differenzspannung von 0,3 Volt auf dem linken Kondensator abgespeichert. Der rechte Kondensator wird auf 1 Volt aufgeladen. Nun erfolgt die Abtastung des abgespeicherten Signals. Nachdem die Abtastung erfolgt ist, sollte der DA-Wandler die Eingangsspannung von 0,7 V nachgebildet haben. Das parallele Wort am Eingang des DA-Wandlers repräsentiert daher das Ergebnis der AD-Umsetzung. Auf Regelung und Bitkorrektur wird später eingegangen.

### 3.2. Parallelisierung des SAR- Verfahrens

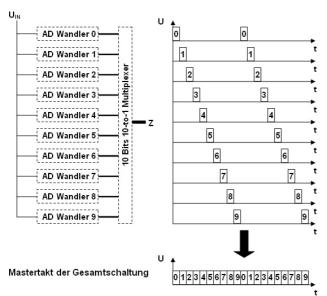

Abb.4 Parallelisierung des SAR Verfahrens

Auch in diesem Verfahren lässt sich durch Parallelisierung die Abtastrate erhöhen. Ein einzelner AD-Umsetzer nach der sukzessiven Approximation speichert mit der Sample and Hold-Schaltung die Eingangsspannung ab und benötigt danach bei einer 10 Bit Auflösung 10 Schritte, um das Signal zu wandeln. Dadurch entsteht eine gewisse Umsetzzeit von der Aufnahme des Eingangssignals bis zur Ausgabe der Bitfolge. Um diese Umsetzzeit zu nutzen, werden wie in Abb.4 beispielsweise zehn AD-Umsetzer parallel geschaltet. Der AD-Wandler 0 speichert im ersten Takt das Eingangssignal ab. Im zweiten Takt beginnt dieser mit der eigentlichen Abtastung. Gleichzeitig speichert im zweiten Takt der AD Wandler 1 das Eingangssignal ab. So werden alle 10 AD-Umsetzer nach und nach angesteuert. Durch diese Parallelisierung wird eine zehnfach höhere Abtastrate erreicht. Werden über die entsprechende Auflösung hinausgehend weitere Umsetzer integriert, so entstehen weitere Taktphasen, die zur Autokalibration genutzt werden können. Im vorliegenden Beispiel werden 16 AD-Umsetzer parallelisiert und nur eine Auflösung von 10 Bit angestrebt. Somit bleiben sechs Phasen für die Regelung zur Verfügung. Die einzelnen Teilschaltungen des AD-Umsetzers und Funktionen werden nachfolgend beschrieben.

#### 3.3. Sample and Hold

Abb.5 Sample and Hold-Schaltung

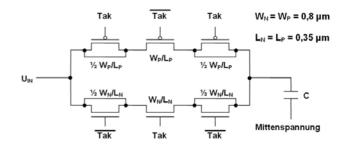

Eine ideale Sample and Hold-Schaltung (S/H-Schaltung) besteht aus einem Schalter und einem Kondensator. Der hier verwendete Schalter wurde mit einem Transmission Gate (TGate) und vier Dummy Transistoren realisiert. Dabei sind zwei Kenngrößen des TGates zu beachten, zum einen die Ladungsinjektion und zum anderen der Durchschaltewiderstand. Da die Ladungsinjektion von der Größe der Transistoren abhängt, wurde das TGate mit der Minimalgröße von AMS implementiert. Durch zusätzliche Dummy-Transistoren, die kurzgeschlossen sind und wie Kapazitäten wirken, wird bei gegenphasiger Ansteuerung zusätzlich die Ladungsinjektion minimiert. Bei einer Kapazität von 240 fF verursacht die Ladungsinjektion eine maximale Fehlerspannung von 204 µV.

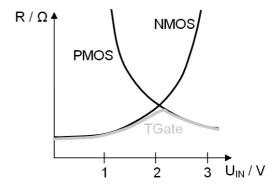

Abb.6 Eingangsimpedanz eines TGates

Die Eingangsimpedanz resultiert aus der Parallelschaltung der beiden Widerstandsverläufe von NMOS- und PMOS Transistor. Somit wird ein relativ konstanter Widerstandsverlauf erreicht.

#### 3.4. Komparator

Abb.7 Komparator

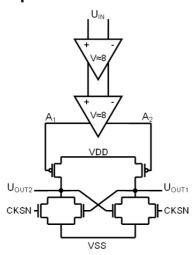

Der Komparator besteht aus zwei Vorverstärkern und einem Latch (Abb.7). Das Latch wird über das Taktsignal CKSN angesteuert. Ist das Taktsignal high, so geht das Latch in den differentiellen Betrieb und vergleicht die beiden Eingangssignale. Ist das Taktsignal hingegen low, so ist das Latch im Flip-Flop-Betrieb und speichert das Ergebnis des vorigen Vergleichs in Form einer Null oder Eins (VSS oder VDD) ab.

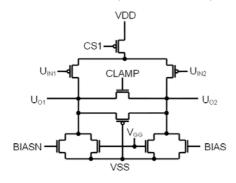

Abb.8 Vorverstärker

Zur Erhöhung der Komparator- Empfindlichkeit muss das Eingangssignal  $U_{IN}$  mindestens um den Faktor 50 verstärkt auf das Latch gegeben werden. Diese Verstärkung erfolgt in zwei Stufen, um möglichst hohe Bandbreite bei gegebener Verlustleistung zu erzielen. Jede Stufe besteht aus einem PMOS- Differenzverstärker mit aktiver Last und zwei Clamp-Transistoren. Die erste Stufe (Abb.8) enthält zusätzlich zwei weitere Transistoren zum Offsetabgleich, angesteuert über die Signale BIAS und BIASN. Der passive Clamp, der mit VSS angesteuert wird, begrenzt den Ausgangsspannungshub auf 1 Volt. Somit muss der Verstärker nicht bis zur Versorgungsspannung aussteuern, wodurch sich seine Erholzeit verkürzt.

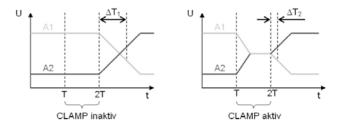

Abb.9 Funktion des aktiven Clamps

Der aktive Clamp-Transistor, der mit dem Taktsignal CLAMP geschaltet wird, erzwingt einen Kurzschluss an den Ausgängen, wodurch die Erholzeit noch weiter verkürzt werden kann. In Abb.9 wird die Funktion des aktiven Clamp ersichtlich. Bei minimalen Differenzspannungen am Eingang des Vorverstärkers und inaktivem Clamp benötigt es lange ( $\Delta T_1$ ), bis das Ergebnis durch das Latch detektiert werden kann, wenn das Ausgangssignal der Vorverstärker seine Polarität ändern muss. Durch den aktiven Clamp wird der Vorgang beschleunigt ( $\Delta T_2 < \Delta T_1$ ), da die beiden Ausgangsspannungen zuerst durch den Kurzschluss auf Mittenspannung gebracht werden. Somit kann auch das Latch auf minimale Spannungsänderungen reagieren, da dieses kurz nachdem CLAMP aktiv war, in den Flip-Flop-Betrieb geschaltet wird.

Die Offsetspannung des Komparators wird über die BIAS-Transistoren ausgeregelt, die die Symmetrie der aktiven Last beeinflussen. Auf die Ansteuerung wird in Abschnitt 3.6 eingegangen.

Die Vorverstärker haben zusammen eine Gesamtverstärkung  $V_{ges} = 35$  dB und eine Grenzfrequenz f.  $_{3dB} = 60$  MHz. Daraus lässt sich eine Anstiegszeit  $t_{10/90} = 5.8$  ns abschätzen. Bei einer Abtastrate von 20 MS/s stehen 25 ns zur Verfügung, so dass die Anstiegszeit ausreichend kurz sein sollte. Die Einschwingzeit des Komparators ist allerdings von der Höhe der Eingangsspannung abhängig, da das Latch bei großer Eingangsspannung einen geringen, bei kleiner Eingangsspannung dagegen einen größeren relativen Hub benötigt, um richtig zu entscheiden.

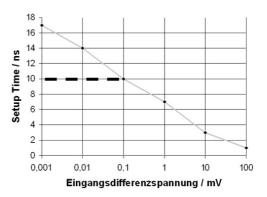

Abb.10 Setup-Time des Komparators

Dazu wurde die Setup-Time simuliert. Diese sagt aus, wie lange die Differenzspannung am Eingang des Komparators anliegen muss, bis das Latch richtig entscheidet. Je kleiner die Differenzspannung, umso größer ist die Setup-Time, da es länger dauert, bis alle parasitären Kapazitäten umgeladen sind. Durch die Integration des aktiven Clamp wird die Setup-Time bei kleinen Eingangsdifferenzspannungen auf 10 ns begrenzt. Die Verzögerungszeit des Komparators, d.h. die Zeit zwischen Freigabe des Clamp und eingeschwungenem Ausgangsignal, beträgt in der Simulation  $\tau = 3$  ns bei  $U_{IN} = 1$  µV.

#### 3.5. Digital-Analog-Wandler

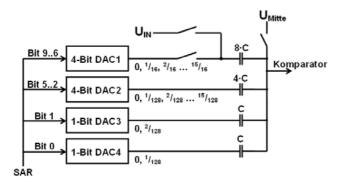

Abb. 11 Digital-Analog-Wandler

Im vorliegenden Konzept wird nicht ein einzelner DA-Wandler eingesetzt, der 1024 Teilspannungen der Referenzspannung  $U_{REF}$  zu erzeugen hätte, sondern es wird nur eine Untermenge von Spannungen erzeugt und stattdessen am Komparatoreingang mit mehreren dual abgestuften Kondensatoren gearbeitet (Abb. 1). Mit den gewählten Abstufungen C, C, 4C, 8C wird als kleinste Teilung nur noch 1/128 UREF benötigt wegen  $\frac{1}{8} \cdot \frac{1}{128} = \frac{1}{1024}$ . Dies vereinfacht ganz entscheidend die Realisierung des Referenzspannungsteilers. Es werden 4 einfache DA-Wandler benötigt, zwei 4-Bit-Wandler und zwei 1-Bit-Wandler, um in Kombination mit den unterschiedlichen Kondensatoren alle Referenzspannungen zu realisieren. Die DA-Wandler bestehen aus einfachen Transmission Gates, die die Teilspannungen einer Widerstandsleiter durchschalten. Benötigt werden lediglich die Spannungswerte  $^{1}/_{16} \dots ^{15}/_{16} \cdot U_{REF}$  und  $^{1}/_{128} \dots ^{15}/_{128} \cdot U_{REF}$ . Dennoch ist die Dimensionierung des Teilers kritisch, da dieser beim Schalten der Transmission Gates durch die Ladeströme der Kondensatoren belastet wird und somit eine endliche Einschwingzeit aufweist. Da aus Gründen der Chipfläche der gleiche Widerstandsteiler nicht für einen, sondern für alle 16 AD-Umsetzer genutzt werden soll, verschärft sich das Problem der endlichen Einschwingzeit. Die genannten Probleme wurden wie folgt gelöst:

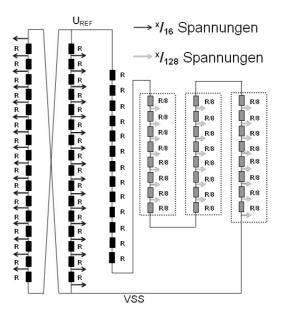

Abb.12 Widerstandsleiter

Es werden drei Reihenschaltungen benutzt, zwei Reihenschaltungen für die  $^{\times}/_{16}$  Spannungen, die kreuzgekoppelt sind, und eine Widerstandskette, die die  $^{\times}/_{128}$  Spannungen erzeugt (Abb.12). Durch die drei Reihenschaltungen sind die jeweiligen Widerstandsketten unabhängig voneinander. Dadurch wirkt sich eine starke Belastung an einer Stelle nicht auf die andere Widerstandskette aus. Die einzelnen Widerstände wiederum bestehen aus Reihen- und Parallelschaltung von Einheitswiderständen. Damit wird optimales Matching im Layout ermöglicht. Ein Einheitswiderstand wurde auf  $R = 104\,\Omega$  ( $2.52\,\Omega$ ) dimensioniert. Somit beträgt der Gesamtwiderstand:

$$\frac{1}{R_{ges}} = 2 \cdot \frac{1}{16 \cdot 104 \ \Omega} + \frac{1}{13 \cdot 104 \ \Omega + 3 \cdot (8 \cdot 13 \ \Omega)}$$

$$R_{\text{ges}} = 555 \ \Omega$$

Mit  $U_{REF} = 2$  V resultiert ein Gesamtstrom von 3,6 mA, was noch akzeptabel ist. Der hochohmigste Anzapfpunkt liegt bei  $U_{REF} = 1$  V.

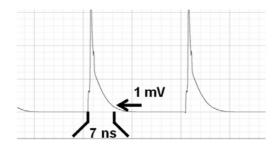

Abb.13 Referenzspannung <sup>8</sup>/<sub>16</sub> · U<sub>REF</sub> = 1 V

Abb.13 zeigt das Einschwingverhalten dieses Knotens bei gleichzeitigem Zuschalten aller 16 AD-Umsetzer.

Die Einschwingzeit auf weniger als 1 mV Abweichung beträgt 7 ns. Es zeigt sich, dass mit diesem Widerstandsteiler ein guter Kompromiss zwischen Einschwingzeit und Verlustleistung gefunden wurde. Im Vergleich dazu hätte sich mit einer Widerstandsleiter, die nur eine Reihenschaltung bei gleichem Gesamtwiderstand enthält, eine Einschwingzeit von über 10 ns ergeben.

#### 3.6. Regelung

Abb.14 Regelung

Da die Linearität (INL und DNL) beim SAR-Verfahren durch den DA-Wandler und den Komparator bestimmt wird, musste eine Abgleichschaltung integriert werden, die die Offset- bzw. Kapazitätsfehler kompensiert. Das Prinzip der Regelung ist in Abb.14 mit zwei Kondensatoren  $C_1$  und  $C_2$  symbolisch dargestellt.

Im ersten Schritt der Regelung wird ein Autozero durchgeführt. Dabei wird der Eingang des Komparators mit 1 Volt kurzgeschlossen. Gleichzeitig wird vom DA-Wandler eine Spannung an den Kondensator  $C_1$  angelegt. Diese Spannung beträgt  $^9/_{16}$ · $U_{REF}$ . Folglich wird der Kondensator  $C_1$ , bei einer Referenzspannung  $U_{REF} = 2$  V, auf die Differenzspannung von  $^1/_2$ · $U_{REF}$  -  $^9/_{16}$ · $U_{REF}$  aufgeladen. Die beiden anderen Kondensatoren  $C_2$  und  $C_6$  werden jeweils auf 1 Volt aufgeladen.

Im nächsten Schritt wird der Autozero inaktiv und die beiden DA-Spannungen bleiben bestehen. Dadurch sollte an beiden Eingängen des Komparators 1 Volt anliegen. Bei einem idealen Komparator werden dann über mehrere Zyklen im Mittel gleich viele Nullen wie Einsen als Ergebnis ausgegeben. Der zeitliche Mittelwert wird auf einer Kapazität abgespeichert. Die Sollspannung ist somit die Mittenspannung. Wenn nun ein Offsetfehler im Komparator vorliegt, werden mehr Nullen als Einsen ausgegeben bzw. mehr Einsen als Nullen. In diesem Fall weist die Kondensatorspannung eine Abweichung von der Mittenspannung auf. Diese Spannung steuert nun die beiden BIAS-Transistoren an und beeinflusst dadurch die aktive Last im Vorverstärker (Abb.8). Somit wird der Offsetfehler kompensiert.

Im dritten Schritt werden nun die beiden DA-Spannungen verändert.  $U_{DA1}$  beträgt nun  $^8/_{16}$ · $U_{REF}$  und  $U_{DA2} = ^2/_{16}$ · $U_{REF}$ . Durch die Veränderung der beiden Spannungen  $U_{DA1}$  und  $U_{DA2}$  findet ein Ladungsausgleich zwischen beiden Kondensatoren  $C_1$  und  $C_2$  statt.

$$\frac{8}{16} \cdot \textit{U}_{\textit{REF}} + \frac{1}{2} \cdot \frac{2}{16} \cdot \textit{U}_{\textit{REF}} = \frac{9}{16} \cdot \textit{U}_{\textit{REF}}$$

Durch das Kapazitätsverhältnis und durch die beiden Spannungen sollte nun wieder an den Eingängen des Komparators jeweils 1 V anliegen. Liegt nun ein Kapazitätsfehler vor oder eine geringe Abweichung in den Spannungen U<sub>DA1</sub> und U<sub>DA2</sub>, wird dies auf einen weiteren Kondensator in der Regelung abgespeichert. Die Spannung dieses Kondensators regelt nun das Signal BAL. Dieses Signal steuert nun einen weiteren Kondensator  $C_5$  an. Ist  $C_1 > 2 \cdot C_2$  wird das Potential von BAL vergrößert. Somit wird die fehlende Ladung am Kapazitätsverhältnis, das die 1 V am Komparatoreingang ergeben sollte, durch den Kondensator C<sub>5</sub> eingebracht. Ist hingegen  $C_1 < 2 \cdot C_2$ , so wird das Potential von BAL kleiner und Ladung wird vom Kapazitätsverhältnis abgezogen. Dadurch wird ein möglicher Kapazitätsfehler kompensiert. Gleichzeitig werden auch die beiden UDA Spannungen überprüft, da sie die Vergleichspannungen für den Komparator vorgeben. Somit wird auch ein Widerstandsleiterabgleich durchgeführt.

Die Einschwingzeit der Regelspannungen ist von der Größe der Kondensatoren  $C_R$  abhängig. Mit der vorgenommenen Dimensionierung benötigt der AD-Umsetzer ca. 50000 Taktzyklen, bis die Regelspannungen die Mittenspannung erreicht haben.

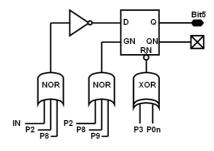

#### 3.7. Sukzessiv- Approximationsregister

Abb.15 Das Sukzessiv-Approximationsregister

Das SAR besteht aus 11 D-Flip-Flops (D-FF), die je nach Takt angesteuert werden. In Abb.15 ist die Ansteuerung von Bit 5 dargestellt. In Phase 2 (P2) wird das D-FF aktiviert. Dabei speichert es eine Eins ab und gibt diese am Ausgang Q aus. Während Phase 2 wird dieses Bit für den Kapazitätsabgleich benötigt. Während der Phase 3 (P3) wird diese Eins wieder ge-

löscht. In Phase 8 (P8) wird wieder eine Eins im D-FF abgespeichert. Dadurch wird nun eine Spannung für den Vergleich an den Eingangskondensatoren angelegt. Während Phase 9 (P9) wird das Ausgangssignal des Komparators (IN) abgespeichert, das das Ergebnis des Vergleichs der vorigen angelegten Spannung ist. Lag die Spannung des vorigen Vergleichs oberhalb der Vergleichsspannung, so wird eine Null abgespeichert; lag sie darunter, wird eine Eins abgespeichert. Dieses Ergebnis bleibt solange im D-FF gespeichert, bis in Phase 15 die Bitfolge ausgegeben wird. Danach werden während der Phase 0 (P0n) alle D-Flip-Flops wieder gelöscht.

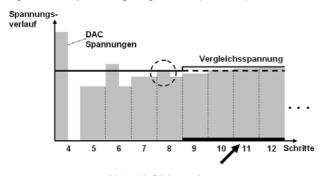

#### 3.8. Bitkorrektur

Das Ergebnis des Sukzessiv-Approximationsregisters wird nicht sofort ausgegeben, sondern durchläuft vorher eine Bitkorrektur, mit der die Auswirkung der folgenden Maßnahme berücksichtigt wird. Um die Settling Time bei höherwertigen Bits zu verkürzen, wird bis zur Phase 8 die Vergleichsspannung um eine geringe Offsetspannung abgesenkt (*Abb.16*).

Abb.16 Bitkorrektur

Dabei kann in Schritt 8 ein Fehler entstehen wie in dieser Abbildung dargestellt (mit Kreis markiert). Die DA-Spannung wäre normalerweise unterhalb der Vergleichsspannung, es würde eine Eins abgespeichert und die Spannung würde bestehen bleiben. Wegen der Offsetspannung liegt aber die DA- Spannung oberhalb der Vergleichsspannung. Nach Schritt 8 wird die Offsetspannung wieder abgeschaltet und somit vergrößert sich die Vergleichsspannung. Nun können die DA-Spannungen die Vergleichsspannung nicht mehr erreichen, sondern nur noch die Vergleichsspannung mit Offset (gestrichelte Linie). Deshalb wird im Schritt 9 zusätzlich geprüft, ob zuvor ein Fehler gemacht wurde oder nicht. Sobald ein Fehler entstanden ist, wird eine zusätzliche Spannung in den darauf folgenden Schritten angelegt (mit Pfeil markiert). Dadurch werden die folgenden Spannungen um die Offsetspannung angehoben. Somit können die DA-Spannungen die Vergleichsspannungen wieder erreichen. Durch die Anhebung der DA-Spannung ab Schritt 9 entsteht ein Fehler bei der Ausgangsbitfolge. Um diesen auszugleichen, wird einfach eine Bitfolge,

die der Offsetspannung entspricht, auf die Ergebnisbitfolge addiert. Dadurch wird der Fehler, der durch den künstlichen Offset entstehen kann, kompensiert.

#### 3.9. Phasensequenz

Der gesamte Ablauf der Umsetzung vollzieht sich in 16 Taktphasen. Die Aktion innerhalb der einzelnen Phasen ist in der folgenden Tabelle dargestellt.

| Phasen | Aktion                                                |

|--------|-------------------------------------------------------|

| P0     | Autozero                                              |

| P1     | Offsetabgleich                                        |

| P2     | Kapazitäts- bzw.<br>Widerstandsabgleich               |

| P3     | Autozero Anlegen der Eingangsspannung U <sub>IN</sub> |

| P4-P14 | eigentliche Abtastung des<br>Eingangssignals          |

| P15    | Bitkorrektur, wenn BitD04 = 1 Ausgabe des Bitfolge    |

#### 3.10. Simulationsergebnisse

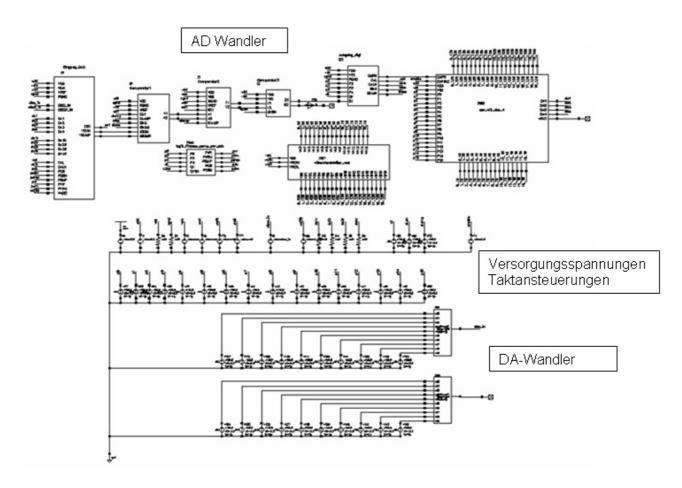

Schaltungseingabe und Simulation erfolgten mit Cadence- Werkzeugen. Nach der vollständigen Dimensionierung und Verifikation aller Teilschaltungen wurde eine Testbench für den gesamten AD-Umsetzer erstellt (Abb.18). Für die Erzeugung des Eingangssignals wurde ein DA-Wandler eingesetzt, der eine rampenförmige Spannung zwischen 0 und 2 V in LSB-Schritten quantisiert. Die entsprechenden Ausgangssignale des AD-Umsetzers werden in Analogspannungen umgerechnet und mit den um die Umsetzzeit verzögerten Eingangsspannungen verglichen. Somit kann bequem die Abweichung dargestellt werden (Abb.17).

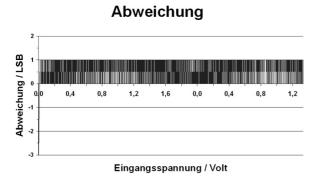

#### Abb.17 Abweichung

Die Abweichung liegt zwischen 0 und 1 LSB. Diese Simulation wurde mit einem AD-Umsetzer durchgeführt, der mit einer Taktrate von 312,5 kS/s betrieben wurde. Dies entspricht bei 16 AD-Umsetzern einer Abtastrate von 5 MS/s. Derselbe Versuch, durchgeführt mit einer Abtastrate von 1,25 MS/s bzw. 20 MS/s, ergab die gleiche Abweichung. In dieser Analyse werden 1600 Zyklen durchlaufen, was eine Simulationszeit von etwa 2 Wochen erfordert.

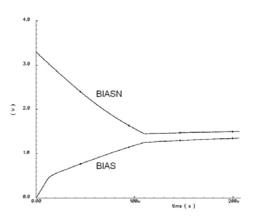

Abb.19 Regelspannungen BIAS und BIASN

In dieser Simulation wurden die Regelspannungen mit Startspannungen versehen. Somit waren diese im eingeschwungenen Zustand, und das Ergebnis konnte sofort ausgewertet werden. In einer weiteren Analyse wurden die Regelspannungen ohne Startspannungen simuliert. In Abb.19 sind die beiden Regelspannungen BIAS und BIASN dargestellt. Die Regelspannungen CAL und CALN verhalten sich in ihrem Einschwingverhalten gleich.

Abb.18 Testbench des AD Wandlers

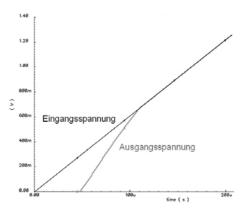

Abb.20 Ein- bzw. Ausgangsspannung

An der Ein- bzw. Ausgangsspannung des AD-Umsetzers (*Abb.20*) kann man erkennen, wie sich die Ausgangsspannung der Eingangsspannung annähert. Der Einschwingvorgang der Regelung dauert etwa 120 µs.

#### 4. Layoutabschätzung

Zum Abschluss wurde im Hinblick auf die Realisierung eine Layoutabschätzung durchgeführt. In der folgenden Tabelle sind die einzelnen Komponenten des AD-Umsetzers aufgeführt. Dabei wurde die Fläche ermittelt, die die Transistoren auf dem IP-Core einnehmen. Für die Verdrahtung der einzelnen Transistoren wurden bestimmte Faktoren angenommen: Für analoge Schaltungen der Faktor 10, für digitale Teilschaltungen der Faktor 1,4 und für den DA-Wandler der Faktor 5, da dieser aus digitalen und analogen Teilschaltungen besteht.

|                      | Transis-<br>torfläche<br>(µm²) | Faktor für<br>die Ver-<br>drahtung | End-<br>fläche<br>(µm²) |

|----------------------|--------------------------------|------------------------------------|-------------------------|

| Komparator           | 305                            | 10                                 | 3050                    |

| Regelung             | 5233                           | 10                                 | 52330                   |

| Sample and<br>Hold   | 1,12                           | 10                                 | 11                      |

| SAR                  | 4684                           | 1,4                                | 6558                    |

| DA Wandler           | 13676                          | 5                                  | 68380                   |

| Takt-<br>generierung | 2228                           | 1,4                                | 3119                    |

| Bitkorrektur         | 2723                           | 1.4                                | 3812                    |

Gesamtfläche eines AD-Umsetzers

137260

Somit kommt man auf eine Fläche eines einzelnen AD-Umsetzers von 0,137 mm². Da der komplette AD-Umsetzer aus 16 einzelnen AD-Umsetzern (2,196 mm²) besteht und einer Widerstandsleiter (0,067 mm²), kommt man auf eine gesamte Corefläche von 2,263 mm².

#### 5. Zusammenfassung und Ausblick

Zwei unterschiedliche Ausgestaltungen für einen 10 Bit-Analog-Digital-Umsetzer nach dem Wägeverfahren wurden untersucht. Mit dem RSD-Verfahren wurde mit vertretbarem Aufwand eine Abtastrate von 5 MS/s erreicht. Durch weitere Parallelisierung wäre eine Abtastrate von 10 MS/s denkbar, allerdings nur mit überhöhtem Aufwand an Chipfläche und Verlustleistung. Die Auflösung von 10 Bit wurde auch mit dem SAR-Verfahren erreicht. Erforderlich dazu sind allerdings Maßnahmen zur Autokalibration, um Fehler durch Offsetspannungen sowie Widerstands- und Kapazitätstoleranzen zu kompensieren. Mit der vorliegenden Schaltung wurde die Abtastrate von 20 MS/s erreicht. Auch bei 50 MS/s ist die Schaltung noch lauffähig, zeigt dann aber einen Auflösungsfehler von 4 LSB. Entscheidend für die Auflösung ist die Genauigkeit des Widerstandsteilers. Hierzu sind noch weitere Untersuchungen erforderlich, ebenso zu Temperaturabhängigkeit, Versorgungsabhängigkeit und Rauschen. Da die Simulationen sehr zeitaufwändig sind, soll nunmehr ein Testchip realisiert werden.

#### 6. Literaturverzeichnis

- [1] Behzad Razavi: Principles of Data Conversions. IEEE Computer Society Press 1994

- [2] Rudy J. van de Plassche: CMOS Integrated Analog-to-Digital and Digital-to-Analog Converters. Kluwer Academic Publishers 2003

- [3] Mikko E. Waltari; Kari A.I. Halonen: Circuit Techniques for Low-Voltage and High-Speed A/D Converters. Springer Verlag 2002

- [4] Reinhard Kindt; Richard Ižák; Jan Strömer: Erfahrungen bei der Nutzung einer AHDL beim Entwurf eines zyklischen AD-Wandlers.

- http://www.imms.de/db/publikationen/2000\_itg\_ahdl.pdf 2000

- [5] R. Jacob Baker; Harry W. Li; David E. Boyce: CMOS Circuit Design, Layout, and Simulation. Wiley 2005

## Modellierung und Synthetisierung des Peripheriebausteins SAB8279

Christof Voelkle

Fachhochschule Ulm, Prittwitzstr. 10, 89075 Ulm cvoelkle@web.de

Auf einer älteren Maschinensteuerung der Firma Handtmann wird unter anderem der Tastatur- und Anzeigecontroller SAB8279 eingesetzt. Dieser Baustein wird schon seit einigen Jahren nicht mehr produziert, und die noch vorhandenen Lagerbestände schwinden langsam aber sicher. Ziel dieser Arbeit ist der Entwurf einer VHDL Beschreibung der von der Steuerung benötigten Funktionen, die Synthetisierung der Beschreibung auf einem FPGA und die Entwicklung einer Platine auf der dieses, und Modelle anderer Bausteine evaluiert werden können.

#### 1. Einleitung

#### 1.1. Motivation

Die erwähnte Maschinensteuerung wird seit 1989 produziert und ist als klassisches Microcontrollerkonzept aufgebaut. Als Prozessor kommt ein 8085 der Firma Intel zum Einsatz. Da dieser Prozessor keinen Speicher und keine Peripherie besitzt, müssen diese Funktionen von externen Bausteinen übernommen werden. Zu diesen Bausteinen gehören:

- RAM

- ROM

- Multifunktionsbaustein SAB8256

- Tastatur- und Anzeigecontroller SAB8279

Die beiden letzten Bausteine werden schon seit einigen Jahren nicht mehr produziert und sind nur noch als Restbestände zu beziehen. Da noch sehr viele Maschinen mit dieser Steuerung in Betrieb sind, muss aber die Versorgung mit Ersatzteilen gesichert sein.

Eine Möglichkeit wäre nun die Steuerung mit aktueller Hardware auszustatten und die Software auf diese Hardware zu portieren. Dagegen spricht allerdings ein gravierender Punkt. Die Software ist auf einem mittlerweile etwas betagten Entwicklungssystem der Firma Hewlett Packard in Pascal und Assembler verfasst worden, was den Portierungs- und Testaufwand sehr hoch ausfallen lassen würde.

Abb. 1: HP64000 Entwicklungssystem

Eine andere Möglichkeit wäre die Nutzung einer aktuellen Steuerung unter Verwendung einer angepassten aktuellen Software. Die Anpassung der aktuellen Software, um die Funktionen der älteren Maschinen zu steuern ist allerdings ebenfalls mit einem hohen Aufwand verbunden.

Aus diesen Gründen wurde beschlossen die betroffenen Bausteine in VHDL zu beschreiben und auf einem FPGA nachzubilden. Dadurch ist sichergestellt, dass die original Software weiterhin ohne Anpassung verwendet werden kann, und die Steuerung verhält sich nach außen, wie eine Originalsteuerung.

#### 1.2. Ziele

Schlussendlich soll der komplette Digitalteil der Steuerung durch eine neue Platine ersetzt werden, auf der möglichst alle Funktionen der alten Platine auf einem FPGA realisiert sind. Dadurch sinkt das Risiko, dass Bauteile abgekündigt werden, auf ein Minimum. Sollte dennoch einmal das FPGA abgekündigt

werden, lässt sich dies durch eine Layoutänderung beheben, da die eigentliche Funktion Hardwareunabhängig als VHDL Beschreibung existiert.

#### 2. Der Baustein SAB8279

#### 2.1. Funktionen

In einer klassischen Microcontrollerschaltung übernimmt der Baustein SAB8279 zwei elementare Funktionen. Zum einen wird von ihm die Abtastung und Auswertung der Tastatur bzw. der Tasten und Schalter übernommen, zum anderen wird von ihm die zyklische Ausgabe der Anzeigedaten übernommen. Diese beiden Funktionen, das Einlesen von Tasten bzw. Schaltern und das Ausgeben von Informationen z.B. auf 7-Segmentanzeigen, waren von damaligen Prozessoren nur mit hohem zeitlichem Aufwand zu realisieren, was den Einsatz dieser Bausteine rechtfertigt.

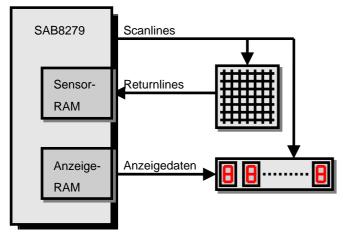

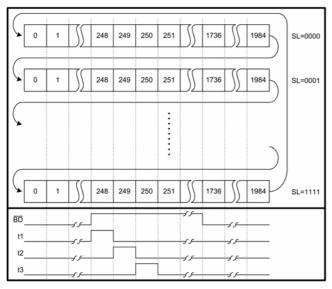

Das Funktionsprinzip ist in Abb. 2 angedeutet. Die einzulesenden Tasten sind in einer Matrix angeordnet. Über die Scanlines, die zyklisch durchgezählt werden, wird immer eine Spalte adressiert und über die Returnlines in das interne RAM zurückgelesen. Die Anzeige funktioniert nach dem Selben Prinzip. Mithilfe der Scanlines werden die 7-Segment-Anzeigen nacheinander adressiert und die jeweiligen Daten aus dem Anzeige-RAM darauf ausgegeben.

Abb. 2: Funktionsprinzip des Bausteins SAB8279

Der SAB8279 besitzt intern einige Konfigurationsregister. Mithilfe dieser Register können die grundlegenden Funktionen des Bausteins auf die eigenen Anforderungen angepasst werden. Beispielsweise gibt es verschiedene Möglichkeiten der Auswertung einer angeschlossenen Tastatur. Zum einen können die Tastendrücke wie bei einer gewöhnliche PC Tastatur ausgewertet werden, das heißt, bei jedem Tastendruck wird der Tastencode in einem FIFO Speicher abgelegt, der vom Prozessor gelesen werden kann. Bei dieser Möglichkeit kann allerdings nichts über die Dauer und nichts über die Anzahl der momentan gedrückten Tasten ausgesagt werden. Bei der anderen Betriebsart dagegen ist das interne RAM als 8x8 Bit Feld organisiert, bei dem jedes Bit dem Zustand einer Taste entspricht. Bei dieser Art ist somit immer bekannt welche Taste(n) gerade gedrückt ist(sind).

Bei jedem Start der Steuerung werden diese Modi immer gleich initialisiert und ändern sich während des Betriebs nicht. Aus diesem Grund ist es nicht nötig die nicht verwendeten Modi in VHDL zu beschreiben. Solange sich das Modell des Bausteins gegenüber dem Prozessor wie das Original verhält ist für den Prozessor auch kein Unterschied feststellbar

### 2.2. Ermittlung der benötigten Funktionen

Um herauszufinden welche Funktionen des 8279 tatsächlich verwendet werden. und somit implementiert werden müssen, ist es nötig den Zustand der internen Konfigurationsregister zu kennen. Die einfachste Lösung wäre den Sourcecode der Steuerungssoftware nach der Initialisierung durchzusehen. Dieser ist allerdings in Papierform leider nicht mehr vollständig vorhanden und die Inbetriebnahme des alten Entwicklungssystems hätte einigen Aufwand bedeutet. Eine andere Möglichkeit ist die Aufzeichnung der Initialisierungssequenz mithilfe eines Logicanalyzers. Zum Einsatz kam hier das Modell TLA5203 der Firma Tektronix. Mithilfe der Initialisierungssequenz und dem Datenblatt des Bausteins ließen sich nun die benutzten Funktionen leicht bestimmen.

Drei wichtige Dinge werden zu Beginn Festgelegt: Die Eingabebetriebsart, die Ausgabebetriebsart und der Eingangstaktteiler. Die Eingabebetriebsart wird auf "Kodierte-Sensor-Matrix" eingestellt. Wie weiter oben beschrieben ist das RAM in dieser Betriebsart als 8x8 Bit Feld ausgelegt, bei dem jedes Bit den Zustand eines Schalters bzw. Tasters repräsentiert. Die andere Betriebsart, bei der das RAM als FIFO-Speicher organisiert wird, muss also nicht realisiert werden. Die Ausgabebetriebsart wird auf "sechzehn 8-bit-Zeichen-Anzeige" initialisiert. Das bedeutet, es können 16 Stellen mit jeweils 8 Bit angesteuert werden. Dies entspricht den verwendeten 7-Segment-Anzeigen mit zusätzlichem Dezimalpunkt. Schlussendlich wird der Taktvorteiler auf initialisiert. Dieser Wert kann somit ebenfalls fest

programmiert werden und muss nicht konfigurierbar sein.

#### 3. Realisierung in VHDL

#### 3.1. Aufteilung in Module

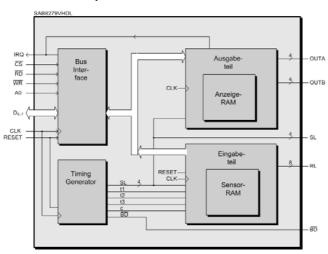

Das Gesamte Projekt ist in 4 Module aufgeteilt:

- Busanbindung inkl. aller benötigten Register

- Timinggenerator

- Eingabeteil

- Ausgabeteil

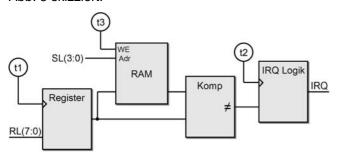

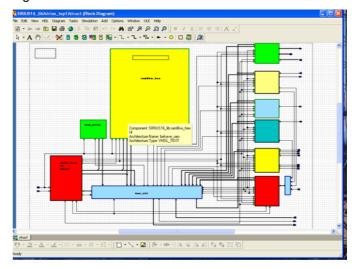

Busanbindungsteil wird der gesamte Datenaustausch mit dem Prozessor abgewickelt. Weiterhin werden dort die entsprechenden Kommandos verarbeitet, gegebenenfalls gespeichert und den anderen beiden Modulen zur Verfügung gestellt. Der Timinggenerator generiert aus dem 5MHz Taktsignal alle benötigten Signale wie z.B. die Scanlines oder das Dunkeltastsignal, und stellt sie den anderen Modulen zur Verfügung. Im Eingabeteil werden die Zustände der angeschlossenen Taster bzw. Schalter abgefragt und gespeichert. Weiterhin wird hier auch überprüft ob sich Veränderungen ergeben haben, und gegebenenfalls wird ein Interrupt Request ausgelöst. Der Ausgabeteil übernimmt die Aktualisierung der 7-Segment Anzeigen und löscht Anzeige-RAM wenn das entsprechende Kommando vom Prozessor gesendet wird. Diese 4 Module werden in einem übergeordneten Modul zusammengefasst und bilden zusammen den Baustein SAB8279VHDL. Abb. 3 zeigt den modularen Aufbau des Projektes.

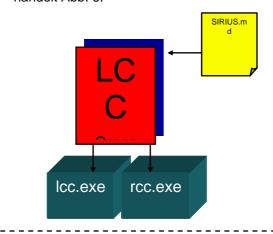

Abb. 3: Modularer Aufbau des VHDL-Projektes

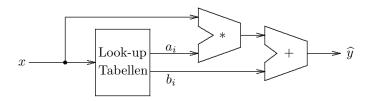

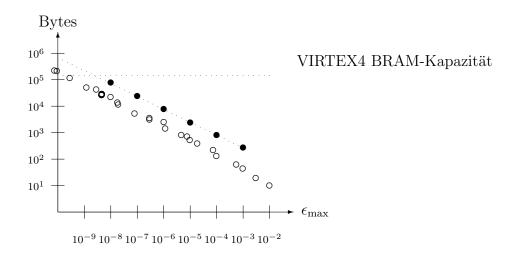

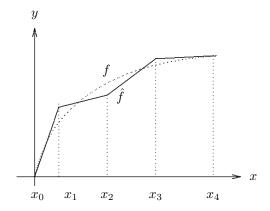

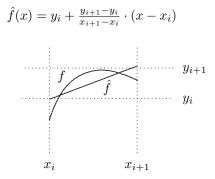

Alle Module die ein Reset Signal benötigen werden mit einem synchronen Reset ausgestattet. In vielen VHDL Projekten die eigentlich streng synchron gehalten werden, wird ein asynchroner Reset eingesetzt. Dies kann allerdings teils schwerwiegenden Problemen führen: Zum einen können bereits sehr kurze Spikes einen Reset auslösen, oder noch schlimmer: Einen "halben" Dabei werden Teile der Reset Register zurückgesetzt, andere bleiben aber gesetzt da der Resetpuls zu kurz war. Bei einem synchronen Reset kann dieses Verhalten nicht auftreten.