Herausgeber: Hochschule Ulm Ausgabe: 46 ISSN 1868-9221 Workshop: Furtwangen Juli 2011

- 1 A Ring-Oscillator-Based Temperature Sensor with Scalable Resolution A. Brönner, D. Fuchs, U. Brunsmann, HS Aschaffenburg

- 7 Ein CMOS-Leistungsverstärker für niedrige Versorgungsspannungen L. Schumm, G. Forster, HS Ulm

- 17 Universeller Sensorsignalkonverter für TDC-basierte digitale Sensorik D. Fuchs, A. Brönner, U. Brunsmann, HS Aschaffenburg

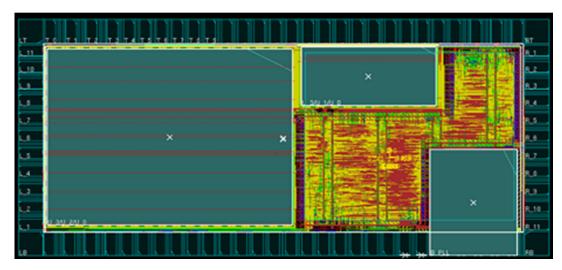

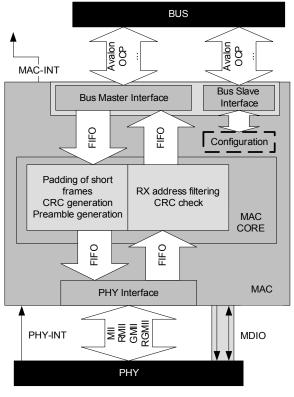

- Entwicklung eines 16/32-bit Prozessorkerns für einen PDA mit JTAG-Schnittstelle und Implementierung in einer 0,18 μm-CMOS Technologie

B. Dusch, S. Stickel, A. Kreker, D. Jansen, HS Offenburg

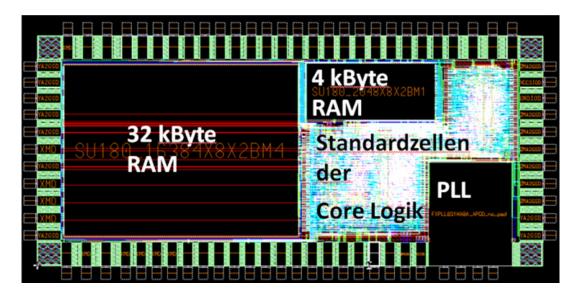

- 35 Design and Test of a Gigabit Ethernet MAC for High-Speed HIL-Support A. Rohleder, S. Jaeckel, A. Sikora, Duale Hochschule Lörrach

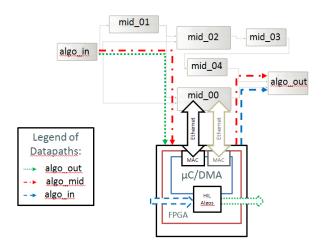

- 41 Entwurf eines dynamisch rekonfigurierbaren Rechensystems auf Basis eines Virtex-5 FPGAs A. Netzeband, F. Kesel, T. Greiner, HS Pforzheim

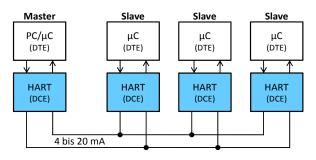

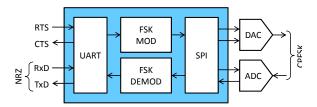

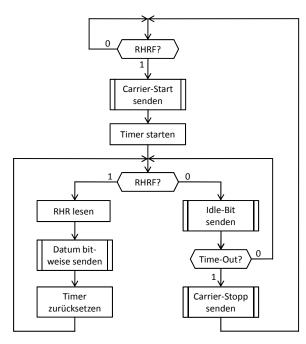

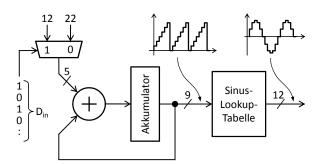

- 51 HART-Transmodulator mit DDS auf einem FPGA A. Schaaf, I. Schoppa, HTWG Konstanz

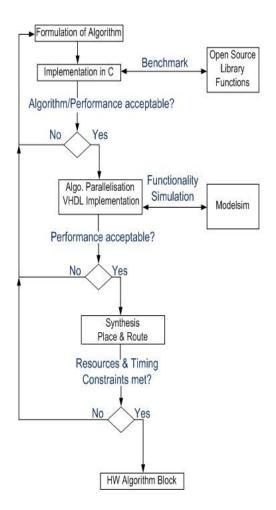

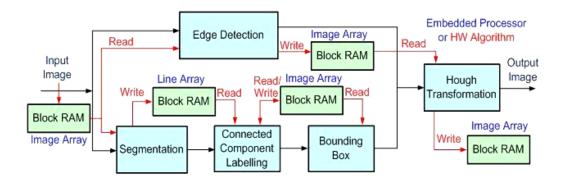

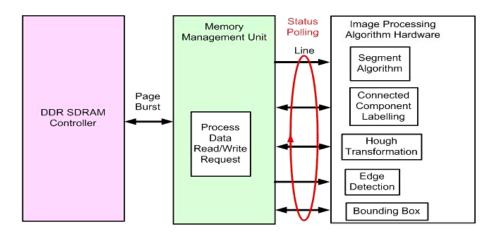

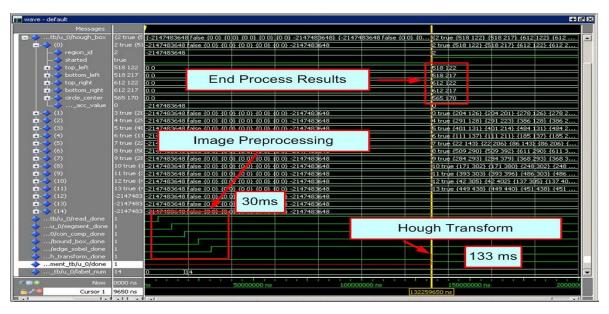

- 57 FPGA Based Image Processing Platform: Concept, Design and Implementation of Algorithms as Pipelined Dedicated Hardware Blocks

S. Singh, H.-P. Bürkle, HS Aalen

- **Applikationsspezifischer Softcore-Prozessor für sicherheitskritische Embedded-Systeme** K. S. Brach, H. Hennig, C. Kielmann, K. Wistuba, I. Schoppa, HTWG Konstanz

- 75 Realization of a Volterra-Based Postdistortion Algorithm for Radar Receivers G. J. Vallant, W. Schlecker, Cassidian Electronics Ulm, F. K. Jondral, Karlsruhe Institute of Technology (KIT)

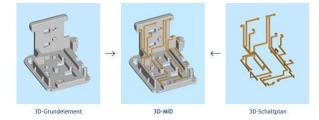

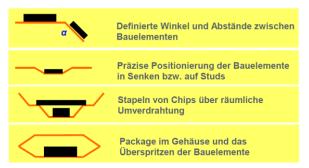

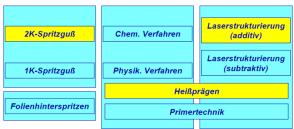

- 83 Dreidimensionale Schaltungsträger auf Basis der LPKF-LDS-Technologie W. John, LPKF Laser und Electronics AG, Garbsen

### Inhaltsverzeichnis

| A Ring-Oscillator-Based Temperature Sensor with Scalable Resolution A. Brönner, D. Fuchs, U. Brunsmann, HS Aschaffenburg                                                                        | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Ein CMOS-Leistungsverstärker für niedrige Versorgungsspannungen  L. Schumm, G. Forster, HS Ulm                                                                                                  | 7  |

| Universeller Sensorsignalkonverter für TDC-basierte digitale Sensorik  D. Fuchs, A. Brönner, U. Brunsmann, HS Aschaffenburg                                                                     | 17 |

| Entwicklung eines 16/32-bit Prozessorkerns für einen PDA mit JTAG-Schnittstelle und Implementierung in einer 0,18 µm-CMOS Technologie  B. Dusch, S. Stickel, A. Kreker, D. Jansen, HS Offenburg | 25 |

| Design and Test of a Gigabit Ethernet MAC for High-Speed HIL-Support  A. Rohleder, S. Jaeckel, A. Sikora, Duale Hochschule Lörrach                                                              | 35 |

| Entwurf eines dynamisch rekonfigurierbaren Rechensystems auf Basis eines Virtex-5 FPGAs  A. Netzeband, F. Kesel, T. Greiner, HS Pforzheim                                                       | 41 |

| HART-Transmodulator mit DDS auf einem FPGA A. Schaaf, I. Schoppa, HTWG Konstanz                                                                                                                 | 51 |

| FPGA Based Image Processing Platform: Concept, Design and Implementation of Algorithms as Pipelined Dedicated Hardware Blocks S. Singh, HP. Bürkle, HS Aalen                                    | 57 |

| Applikationsspezifischer Softcore-Prozessor für sicherheitskritische Embedded-Systeme K. S. Brach, H. Hennig, C. Kielmann, K. Wistuba, I. Schoppa, HTWG Konstanz                                | 67 |

| Realization of a Volterra-Based Postdistortion Algorithm for Radar Receivers G. J. Vallant, W. Schlecker, Cassidian Electronics Ulm F. K. Jondral, Karlsruhe Institute of Technology (KIT)      | 75 |

| Dreidimensionale Schaltungsträger auf Basis der LPKF-LDS-Technologie W. John, LPKF Laser und Electronics AG, Garbsen                                                                            | 83 |

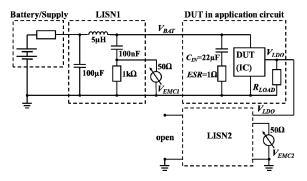

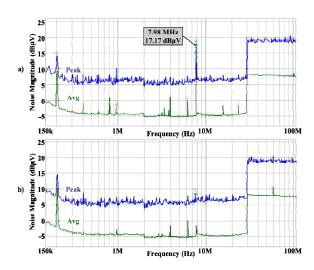

| EMC Optimization of Linear Regulators with a Charge Pump - Design, Simulation and Measurements                                                                                                  | 91 |

| J. Wittmann, B. Wicht, Robert Bosch Zentrum für Leistungselektronik, HS Reutlingen                                                                                                              |    |

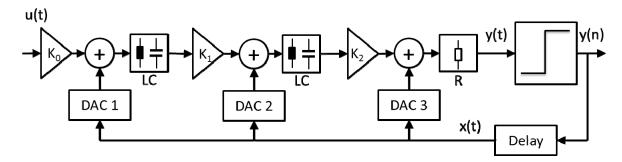

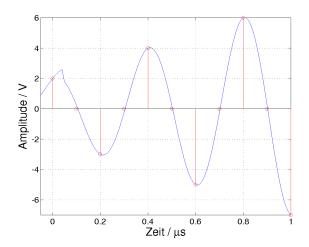

| Entwurf und Aufbau eines zeitkontinuierlichen Bandpass-Delta-Sigma-Modulators vierter Ordnung  S. Wälde, C. Schick, HTWG Konstanz                                                               | 97 |

| Tagungsband zum Workshop der Multiprojekt-Chip-Gruppe Baden-Württemberg Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie.                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die Inhalte der einzelnen Beiträge dieses Tagungsbandes liegen in der Verantwortung der jeweiligen Autoren.  Herausgeber: Gerhard Forster, Hochschule Ulm, Prittwitzstraße 10, D-89075 Ulm  Alle Rechte vorbehalten |

| Diesen Workshopband und alle bisherigen Bände finden Sie im Internet unter: http://www.mpc.belwue.de                                                                                                                |

# A Ring-Oscillator-Based Temperature Sensor with Scalable Resolution

Andreas Brönner, Daniel Fuchs, Ulrich Brunsmann

Abstract—A ring-oscillator-based digital temperature sensor with scalable resolution is presented. Through added temperature sensitive resistors the thermal sensitivity is shaped. The circuit was fabricated in AMS 0.35  $\mu m$  CMOS technology. Unlike conventional temperature sensors relying on semiconductor pn-junctions and ADCs, the proposed sensor exploits the frequency difference of two ring oscillators as a way of converting temperature to a digital output. The experimental results show that the resolution can be scaled from 0.24 °C to 55  $\mu$ °C at the expense of sampling rate over a temperature range from -25 °C to 75 °C. We present the basics of operation, the design and layout of the chip and an evaluation of performance data.

*Index Terms*—CMOS, digital, temperature sensor, RC load, scalable resolution, ring oscillator.

#### I. INTRODUCTION

In recent years all digital temperature sensors became more interesting. The tendency towards decreasing feature size and associated reduction in transistor gate-oxide thickness forces the system voltage to decrease, making analog design difficult [1]. Analog smart temperature designs usually adopt the parasitic substrate or lateral bipolar transistor for temperature sensing taking advantage of bandgap reference [2]. Traditional analog-to-digital converters are utilized for converting a voltage or current into subsequent digital output code. In order to reduce measurement errors, additional calibration circuits at the expense of chip area and power consumption proved to be necessary [3].

Digital temperature sensors however are mostly based on temperature effects of the mobility of charge carriers and threshold voltage of the MOSFET in order to produce a pulse width variation proportional to the test temperature change. Besides TDC-based temperature sensors, generating a pulse width proportional to test temperature fed into a time-to-digital converter (TDC) for output coding [4], it is possible to

Andreas Brönner , andreas.broenner@h-ab.de, Daniel Fuchs, daniel.fuchs@h-ab.de, and Ulrich Brunsmann, ulrich.brunsmann@h-ab.de, are with University of applied sciences Aschaffenburg, engineering department, laboratory of electronic devices, Würzburger Straße 45, 63743 Aschaffenburg.

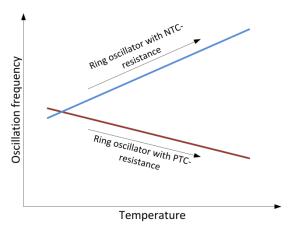

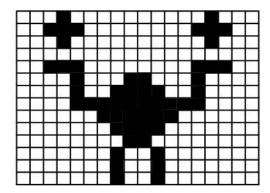

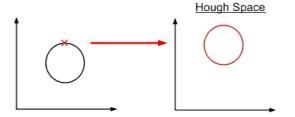

Fig. 1. Conceptual graph of temperature dependency of the oscillation frequency of ring oscillators with NTC- and PTC-resistance.

use the sensitivity of the pulse-shrinking-TDC output code to measure temperature directly without any temperature-to-pulse generator [5]. Temperature dependent propagation delays of the rising and falling edges through different gates of the pulse-shrinking TDC cause comparative temperature dependent pulse shrinking, generating a change in the digital output code. Recently starved ring oscillators, implemented as temperature dependent elements for special applications like Radio Frequency Identification Tags [6] or U-Healthcare [7], feature low power consumption (30 nW) with medium resolution (0.18 °C/LSB). Usually temperature sensitive resistors steer current through ring oscillator cells. In [8], a frequency-todigital converter based temperature sensor is presented. Temperature is measured using the difference in frequencies between a temperature sensitive oscillator and a temperature insensitive oscillator reaching a high sampling rate of 366 kS/s.

Smart temperature sensor performance requirements differ as much as application fields, for example, engine limit monitoring with low accuracy [9], temperature monitoring for home or office electronics, mobile phones, PDAs with medium accuracy [10] up to medical equipment requiring high accuracy [11].

Addressing the issue of wide range of applications in this paper a smart temperature sensor with scalable resolution is proposed. Fig. 1 shows an ideal temperature-frequency-relationship of two ring oscillators applied. The ring oscillator employing a PTC-

1

resistance increases propagation delay and thus decreases frequency as temperature increases. This oscillation frequency is used to generate a time slot within a counter counting the number of clock cycles received from the second ring oscillator. The width of this time slot can be coarsely scaled by a frequency divider. The resulting digital code is proportional to the test temperature.

The paper is organized as follows: in section II we use delay models to describe the operating principle of the proposed delay elements before we present how the resolution can be scaled. Performance data are shown in section III followed by the conclusion in section IV.

#### II. PROPOSED CMOS TEMPERATURE SENSOR

In this section we describe the ring oscillator design modeling using RC delay models. We consider in particular, how the resolution can be scaled.

#### A. 2<sup>nd</sup> Order Delay Estimation

Since propagation delay is one of the most critical performance parameters in CMOS digital circuits, much effort had been devoted to the extraction of accurate, analytical expressions for timing models of basic circuits. Besides the RC delay model, the Elmore delay model gains importance [12].

RC delay models approximate the nonlinear transistor current-voltage and capacity-voltage characteristics with average resistance and capacitance over the switching range of the MOSFET gate. This approximation works remarkably well for delay estimation despite its obvious limitation in predicting detailed analog behavior.

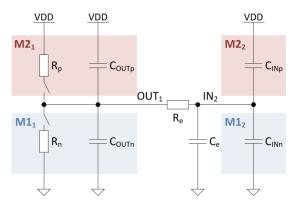

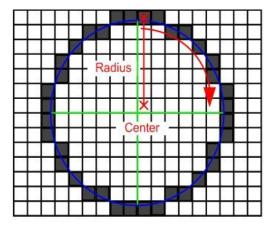

Our ring oscillators consist of an odd number of inverter gates including a subsequent on chip RC circuit. The equivalent RC circuit of one stage is shown in Fig. 2, input capacitances of stage one are neglected as well as wire capacitance. Analyzing the propagation delay of the transition from high to low  $t_{PHL}$ , we summarize the capacitors  $C_e$ ,  $C_{IN2P}$  and  $C_{IN2N}$  to  $C_{le}$  including the extra capacitor  $C_e$ . Output capacitors of the first stage are merged to  $C_l$  achieving a  $2^{nd}$  order RC circuit. Using the inverse Laplace transformation of the systems transfer function, the step response can be calculated.

$$V_{OUT}(t) = V_{DD} \frac{\tau_1 e^{-t/\tau_1} - \tau_2 e^{-t/\tau_2}}{\tau_1 - \tau_2}$$

$\tau_1$  and  $\tau_2$  depend on the resistances and capacitances:

$$\tau_{1,2} = \frac{R_n C_l + (R_n + R_e) C_{le}}{2} \left( 1 \pm \sqrt{1 - \frac{4 \frac{R_e}{R_n} \frac{C_{le}}{C_l}}{\left[1 + \left(1 + \frac{R_e}{R_n}\right) \frac{C_{le}}{C_l}\right]^2}} \right)$$

Fig. 2. Equivalent circuit for two inverters with extra RC network in between, designed as ring oscillator stage.

The system can be approximated as a 1<sup>st</sup> order system with a single time constant [12], i.e. the second order RC combination can be estimated as a first order system with one single time constant:

$$\tau = \tau_1 + \tau_2 = R_n C_l + (R_n + R_e) C_{le} .$$

If the two time constants are equal  $(\tau_1 = \tau_2)$  the error in estimated propagation delay reaches the worst case value of less than 15%. If one time constant is remarkably bigger than the other, error is less than 7 % [12]. It is possible to control the propagation delay of the stage if the extra resistance and capacitance are designed with respect to the time constant. Temperature dependant variation of resistance leads to chances of propagation delay and oscillation frequency according to temperature.

Initially, we look at temperature effects influencing the MOSFET current. If silicon is used as base material, the mobility of charge carriers  $\mu$  is a function of temperature and the current through the switches varies accordingly [13]. Operating the MOSFETS above the threshold voltage  $V_T$ , which also varies with temperature, and above cryogenic temperatures, well known empirical formula apply for silicon [14]:

$$\mu(T) = \mu(300K) \left(\frac{T}{300K}\right)^{-a}$$

$$a = 1.5 \dots 2.5$$

$$\frac{\Delta V_T}{\Delta T} = -1 \frac{mV}{^{\circ}C} \dots -3 \frac{mV}{^{\circ}C}$$

These effects have been used to build a digital sensor and, as they inversely modify the switching current, also for thermal compensation, e.g. by [4, 5, 15]. The combined temperature effects result in a current with negative temperature coefficient and propagation delay with positive temperature coefficient. Ring oscillator frequency decreases as temperature increases.

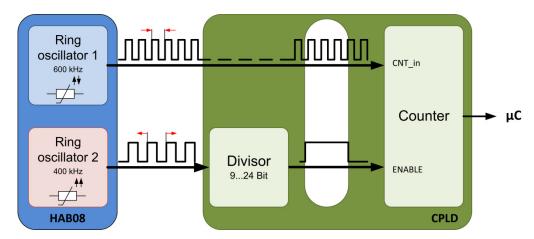

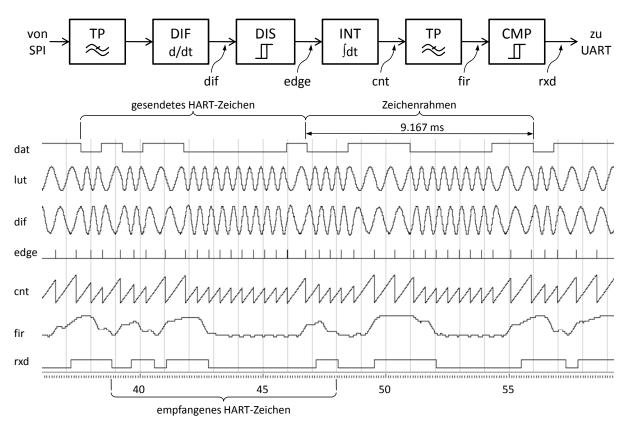

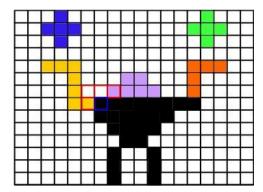

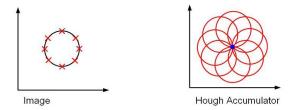

Fig. 3. Operating principle of our ring-oscillator-based digital sensor. The frequency-temperature-relationship is implemented according to Fig. 1.

To control the temperature coefficient of the ring oscillator frequency, we instead propose to use an extra resistance and capacitance which may be described by the BSIM3v3 equations [16]:

$$R(T) = R(TNOM)(1 + TCR1(T - TNOM))$$

$$C(T) = C(TNOM)(1 + TCC1(T - TNOM))$$

The temperature coefficients of different layers for resistor (TCR1) and capacitor (TCC1) given in the manufacturers design handbook are essential for the relation between frequency and temperature. In order to get the frequency characteristics shown in Fig. 1, dimensioning of the extra resistor is important. Lower MOSFET carrier mobility forces the frequency to decrease with rising temperature. This effect can be either reinforced with extra PTC resistance, or not only be compensated but excelled by implementing an extra NTC resistance in order to get a rising frequency curve with temperature. In our test chip, the negative temperature coefficient of frequency caused by MOSFET current is damped using a poly resistor R<sub>e</sub> in one oscillator, while being strengthened using an nwell resistor Re in the other.

#### B. Scaling the Resolution

The structure of our proposed temperature sensor is shown in Fig. 3. The HAB08 test chip containing two ring oscillators has already been described [5]. The oscillators differ in their fundamental frequency and temperature coefficient of frequency, achieved by scaling of the additional resistor and capacitor. In order to reach sub-degree resolution, an intelligent handling of ring oscillator signals is needed. Simple analysis of frequency difference between the two oscillators would stick the resolution to a predefined value, usually several degrees [8]. Hence, we use a different method to convert the frequency into a digital code proportional to the test temperature. Pulses of the ring oscillator frequency, having a lower or nega-

tive temperature coefficient, are fed into a configurable frequency divider, downsizing frequency by 2<sup>n</sup>, where n is set by a microcontroller. The output signal generates a time slot whilst a counter counts the number of clock cycles received from the second ring oscillator with positive temperature coefficient. Increasing the time slot width and increasing the number of pulses to be counted at the same time are the main features of our sensor system, connecting the resulting digital output code proportional to the measured temperature. Temperature resolution of our sensor system can be scaled by changing the time slot width using the frequency divider. We can change the divisor from 29 to 2<sup>24</sup> in order to scale the resolution and so the accuracy from 3.75 °C to 0.06 °C, considering  $3\sigma_{max}$ maximum standard deviation, see Table 1. With longer time slot, our sampling rate is scaled from 204.8 Hz to 0.05 Hz. Higher resolution is achieved at the expense of the measurement rate, as shown in Fig. 8.

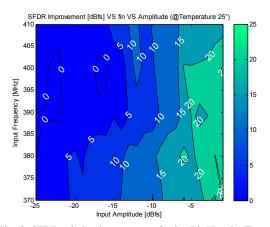

#### III. MEASUREMENT DATA

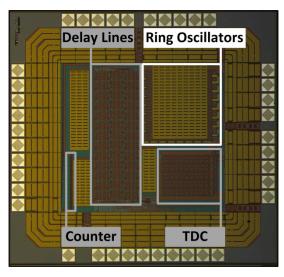

The test chip was fabricated using an AMS  $0.35~\mu m$  CMOS process. Beside the proposed ring oscillators the HAB08 test chip contains two delay lines, a counter and a pulse shrinking TDC. The chip was designed for advanced laboratory courses within our research projects on smart sensors [5]. The ring oscillator sensor occupies  $0.21~mm^2$  of chip area while complete chip size is  $3~mm^2$ , see Fig. 5. In this section, we present the temperature sensor system including experimental setup and measurement results.

#### A. Experimental Setup

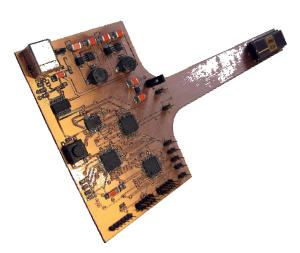

In order to evaluate the sensor system, a configurable printed evaluation board for the HAB08 test chip was designed to operate the ring oscillators as single systems or a complete sensor system. The step-down voltage regulator LM2671M-3.3 (National Semiconductor) with a constant output voltage of 3.3 V is used to simulate operating conditions and allows the board

Fig. 4. Evaluation board for our temperature sensor system showing a test chip in the background.

to be battery powered. Two CPLDs (EPM3064, Altera) and a microcontroller (PIC18F45K20, Microchip) are being utilized. As shown in Fig. 3, one CPLD is configured to divide the ring oscillator frequency, while the second CPLD counts incoming pulses and feeds the digital output to the microcontroller, where the information is evaluated and sent to a PC via a RS232 to USB converter (FT232RL). The divider is controlled by changing the configuration of a 16:1 multiplexer between the Divider-CPLD and the Counter-CPLD. The current multiplexer position is connected to microcontroller port signals, shifted by keystroke.

The finger of the evaluation board containing the chip was fitted into a temperature dry well calibrator (CTD9300-165, WIKA). The latter was certified by a DAkkS1 laboratory and ensures traceability of our temperature calibration to the german PTB<sup>2</sup> standard. In order to achieve a temperature stability of 0.02 °C and measurement errors of 0.1 °C as specified by the manufacturer of the calibrator, the sensor is placed in the lower third of the calibrator bushing. A reference PT100 sensor class AA is set on top of the HAB08 test chip package for the purpose of measuring the package temperature during calibration. The resistor value is fed into the high precision multimeter (3458A, Agilent) with  $10 \mu\Omega$  sensitivity using fourwire resistance measurement. The measurement process was almost completely automated via a Python program.

In order to determine the performance of our sensor, the digital output code was measured as a function of

Fig. 5. Microphotograph of the test chip with highlighted structures.

Table 1: Performance summary of the proposed CMOS digital temperature sensor, taking account of minimum, mean and maximum value of triple standard deviation over the complete test temperature range.

| Divisor  | fs    | $3 \sigma_{min}$ | 3 σ <sub>mean</sub> | $3 \sigma_{max}$ |

|----------|-------|------------------|---------------------|------------------|

|          | Hz    | °C               | °C                  | °C               |

| $2^{11}$ | 204.8 | 0.21             | 1.32                | 3.75             |

| $2^{13}$ | 51.2  | 0.04             | 0.61                | 1.79             |

| $2^{15}$ | 12.8  | 0.03             | 0.39                | 0.66             |

| $2^{17}$ | 3.2   | 0.01             | 0.16                | 0.54             |

| $2^{19}$ | 0.8   | 0.009            | 0.10                | 0.35             |

| $2^{21}$ | 0.2   | 0.008            | 0.05                | 0.14             |

| $2^{23}$ | 0.05  | 0.007            | 0.04                | 0.06             |

the temperature from -25 °C to 75 °C with 12.5 °C increment. The measurement rate depends on the selected frequency divisor, see Table 1. Before starting a series of measurements on each test chip, the temperature of the programmable temperature calibrator was set to -25 °C allowing it to stabilize. Every temperature value is set automatically via Python script. After the desired value and stability is reached, the measurement starts. Sensor system and multimeter are read-out almost simultaneously. After 1500 values are collected, temperature increases by 12.5 °C until it reaches 75 °C. A complete evaluation cycle takes about three weeks. It was performed on two arbitrarily selected test chips (chip 3, chip 6).

#### B. Results

Table 1 shows measured performance data of the proposed sensor system. If the divisor increases, conversion rate (fs) and accuracy decrease accordingly. We use the triple standard deviation of 100 subsequent measurement values for both chips to specify accuracy. Taking the mean value, the temperature accuracy range of our system can be scaled from 1.32 °C to 0.04 °C by changing the divisor.

<sup>&</sup>lt;sup>1</sup> DAkkS (Deutsche Akkreditierungsstelle) is the national accreditation body of the Federal Republic of Germany. It is legally mandated to carry out accreditations of conformity assessment bodies.

<sup>&</sup>lt;sup>2</sup> PTB (Physikalisch-Technische Bundesanstalt) is the national metrology institute.

| Resolution    | Conversion | Temperature    | CMOS       | Chip Area             | Sensor |

|---------------|------------|----------------|------------|-----------------------|--------|

|               | Rate       | Range          | Technology |                       |        |

| 0.7 °C/LSB    | 1 Hz       | 0 °C - 100 °C  | 80 nm      | 0.016 mm <sup>2</sup> | [17]   |

| 0.4 °C/LSB    | 10 Hz      | 8 °C - 85 °C   | 0.13 μm    | 0.04 mm <sup>2</sup>  | [6]    |

| 0.18 °C/LSB   | 100 Hz     | 5 °C - 100 °C  | 0.13 μm    | 0.05 mm <sup>2</sup>  | [7]    |

| 0.24 °C/LSB   | 205 Hz     | -25 °C - 75 °C | 0.35 μm    | 0.21 mm <sup>2</sup>  | This   |

| 0.0009 °C/LSB | 0.8 Hz     | -25 °C - 75 °C | 0.35 μm    | 0.21 mm <sup>2</sup>  | Work   |

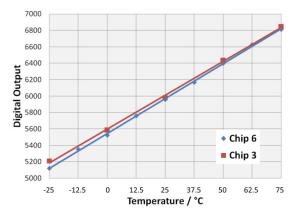

Fig. 6. Digital output code as a function of temperature, measured at 51.2 Hz conversion rate.

With increasing temperature, the digital output code of our system increases nearly linear. Thus, we define resolution by the ratio of maximum temperature difference to the corresponding difference of output codes. Fig. 6 shows the data for both test chips at a conversion rate of 51.2 Hz, reaching a resolution of 0.06 °C. The linearity of the output code as a function of temperature is equal for every suspended divisor while the difference between maximum digital output-codes at 75 °C and minimum digital output code at -25 °C increases. This increase results in a higher resolution of the sensor system.

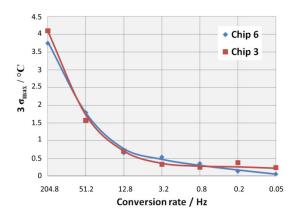

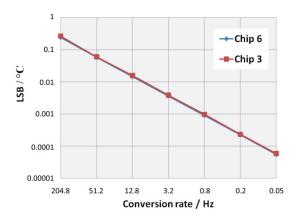

Fig. 7 demonstrates that the worst case accuracy, hence the maximum value of triple standard deviation, decreases with the conversion rate, reaching 0.06 °C getting a measured value every 20 s. Likewise, the temperature resolution of the proposed sensor system scales with conversion rate from 0.24 °C to 55  $\mu$ °C. In Fig. 8, the relationship between the resolution and the conversion rate of the ring-oscillator-based sensor is presented.

#### IV. CONCLUSION

A CMOS temperature sensor fabricated in 0.35  $\mu m$  CMOS technology featuring a scalable resolution has been presented.

Fig. 7. Accuracy as a function of conversion rate, taking account of the maximum value of the triple standard deviation over the complete temperature range.

Fig. 8. Resolution of the least significant bit (LSB) as a function of the selected conversion rate.

The sensor can be two-point calibrated at the two ending temperatures with first-order curve fitting because of the linearity of the sensor output code from -25 °C to 75 °C.

A scalable resolution from 0.24 °C to 55  $\mu$ °C is achieved through smart evaluation of two different ring oscillator output signals. A comparison of the performance data of the proposed temperature sensor with other smart ring-oscillator-based temperature sensors is presented in Table 2. This table shows that, besides scalable resolution, our sensor concept offer high resolution related to conversion rate. In our future

work we will focus on a fabrication process with smaller feature size in order to minimize chip area.

#### ACKNOWLEDGEMENT

The authors would like to acknowledge the support of the Bayerisches Staatsministerium für Wissenschaft, Forschung und Kunst in the context of the Forschungsschwerpunkt Intelligente Sensorik at University of Applied Sciences, Aschaffenburg, Germany. Technical support of WIKA Alexander Wiegand SE & Co. KG, Klingenberg, Germany, is also greatfully acknowledged.

#### REFERENCES

- [1] G. Roberts and M. Ali Bakhshian, "A Brief Introduction to Time-to-Digital and Digital-to-Time Converters," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 57, no. 3, pp. 153–157, 2010.

- [2] J. Zeng, Y. Li, H. Xie, and J. Wen, "CMOS digital integrated temperature sensor," in 6th International Conference on ASIC, 2005. ASICON 2005, 2005, pp. 248–252.

- [3] M. Pertijs, A. Bakker, and J. Huijsing, "A high-accuracy temperature sensor with second-order curvature correction and digital bus interface," in *The 2001 IEEE International Symposium on Circuits and Systems*, 2001. ISCAS 2001, 2001, pp. 368–371.

- [4] C. C. Chun, L. an Wei, C. C. Yu, and C. Poki, "An accurate CMOS time-to-digital-converter-based smart temperature sensor with negative thermal coefficient," in *Sensors*, 2005 *IEEE*, 2005, pp. 4.

- [5] A. Brönner, D. Fuchs, and U. Brunsmann, "An experimental test chip for TDC-based digital sensors," in Workshop der Multiprojekt-Chip-Gruppe Baden-Württemberg, Reutlingen, 2010, pp. 67–78.

- [6] P. Sunghyun, M. Changwook, and H. C. Seong, "A 95nW ring oscillator-based temperature sensor for RFID tags in 0.13 μm CMOS," in 2009. IEEE International Symposium on Circuits and Systems, 2009. ISCAS, 2009, pp. 1153–1156.

- [7] S. W. Sung, H. L. Jung, and C. SeongHwan, "A ring oscillator-based temperature sensor for U-healthcare in 0.13 μm CMOS," in 2009 International SoC Design Conference (ISOCC), 2009, pp. 548–551.

- [8] K. Kisoo, L. Hokyu, J. Sangdon, and K. Chulwoo, "A 366kS/s 400uW 0.0013mm2 frequency-to-digital converter based CMOS temperature sensor utilizing multiphase clock," in *Custom Integrated Circuits Conference*, 2009. CICC '09. IEEE, 2009, pp. 203–206.

- [9] A. Bakker and J. Huijsing, "Micropower CMOS temperature sensor with digital output," *IEEE Journal of Solid State Circuits*, vol. 31, no. 7, pp. 933–937, 1996.

- [10] K. Oonchom, B. Arnuttinanon, and O. Wongwirat, "A development of hybrid temperature recorder monitoring system," in 2010 International Conference on Control Automation and Systems (ICCAS), 2010, pp. 271–275.

- [11] C. Boano, M. Lasagni, K. Römer, and T. Lange, "Accurate Temperature Measurements for Medical Research Using Body Sensor Networks," in 2011 14th IEEE International Symposium on Object/ Component/ Service-Oriented Real-Time Distributed Computing Workshops (ISORCW), 2011, pp. 189–198.

- [12] N. H. E. Weste and D. M. Harris, *Integrated circuit design*, 4th ed. Boston, Singapore: Pearson, 2011.

- [13] S. M. Sze and K. K. Ng, *Physics of semiconductor devices*, 3rd ed. New York: John Wiley & Sons, 2007.

- [14] R. J. Baker, *CMOS: Circuit design, layout, and simulation*, 2nd ed. Hoboken, NJ: Wiley-Interscience [u.a.], 2008.

- [15] C. C. Chen, P. Chen, C. S. Hwang, and W. Chang, "A Precise Cyclic CMOS Time-to-Digital Converter With Low Thermal Sensitivity," *IEEE Transactions on Nuclear Science*, vol. 52, no. 4, pp. 834–838, 2005.

- [16] W. Liu, Mosfet models for spice simulation, including BSIM3v3 and BSIM4. New York: Wiley-Interscience Publication, 2001.

- [17] K. K. Chan, S. K. Bai, G. L. Chil, and H. J. Young, "CMOS temperature sensor with ring oscillator for mobile DRAM self-refresh control," in 2008. IEEE International Symposium on Circuits and Systems, 2008. ISCAS, 2008, pp. 3094–3097.

Andreas Brönner received the B. Eng. degree in electrical engineering from university of applied sciences Aschaffenburg, Germany, in 2010 where he has been working towards the M. Eng. degree in the Laboratory of electronic devices. His research interests include high-resolution time-to-digital converters and high-accuracy smart temperature sensors.

Daniel Fuchs received the B. Eng. degree in electrical engineering from university of applied sciences Aschaffenburg, Germany, in 2010 where he has been working towards the M. Eng. degree in the Laboratory of electronic devices and chip design. His research interests include integrated sensor application and high-accuracy smart temperature sensors.

Ulrich Brunsmann is a professor for Electronic Devices and Computational Intelligence at the University of Applied Sciences, Aschaffenburg. He was with Battelle-Institut, Frankfurt, before, where he headed the development of sensors and electronics for space astronomy. He received his PhD (1977) and his diploma degree (1972) in the field of solid state surface physics at the University of Gießen.

## Ein CMOS-Leistungsverstärker für niedrige Versorgungsspannungen

Lukas Schumm, Gerhard Forster

Zusammenfassung-In der vorliegenden Arbeit wird die Entwicklung einer linearen Leistungsstufe zum Treiben einer niederohmigen Ausgangslast vorgestellt. Sie wurde in einer 0,35 µm-CMOS-Technologie mit der Versorgungsspannung 3,3 V realisiert und erreicht eine Ausgangsspannung von 3,0 Vpp an 50 Ohm. Die Ruhestromaufnahme von 500 µA ist bezüglich Temperatur und Versorgungsspannung stabilisiert. Der IP-Block beinhaltet eine Rail-to-Rail-Endstufe und eine geeignete Eingangsstufe zur Rückkopplung als Buffer. Die Schleifenverstärkung beträgt 82 dB, die Transitfrequenz liegt über 10 MHz und die Offsetspannung unter 2 mV. Zu erwartende Fertigungstoleranzen wurden im Rahmen einer Entwurfsoptimierung berücksichtigt.

Schlüsselwörter—CMOS-Leistungsverstärker, Arbeitspunktstabilisierung, Entwurfszentrierung, Rail-to-Rail-Buffer.

#### I. EINLEITUNG

Der weiterhin ungebrochene Trend zur Verringerung der Strukturgrößen in der Mikroelektronik macht den Entwurf von leistungsfähigen Analogschaltungen zunehmend schwieriger. Während die steigenden Ausgangsleitwerte der Transistoren und die Variabilität der Bauelemente lediglich verhindern, dass die weitere Miniaturisierung effizient genutzt werden kann, stellt die Verringerung der Versorgungsspannung für viele Anwendungen ein ernstes Machbarkeitsproblem dar. Batteriebetriebene Systeme der Kommunikations-, Medizin- oder Automatisierungstechnik profitieren zwar von niedrigen Versorgungsspannungen, dennoch sind auch hier niederohmige Aktoren wie Lautsprecher, Laser oder Ultraschallgeber zu treiben [1]. Hierzu werden lineare Endstufen mit hohem Aussteuerbereich und geringer Offsetspannung benötigt.

Lukas Schumm, lschumm@mail.hs-ulm.de und Gerhard Forster, forster@hs-ulm.de sind Mitglieder der Hochschule Ulm, Eberhard-

Finckh-Straße 11, 89075 Ulm

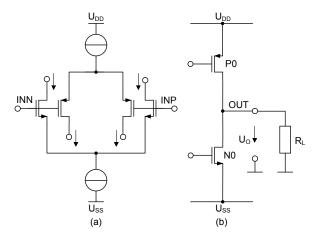

Abbildung 1: Rail-to-Rail-Prinzip am Eingang (a) und Ausgang (b)

Ziel der vorliegenden Arbeit war die Entwicklung eines Leistungsverstärkers als Standardzelle zum Betrieb eines Lastwiderstands  $R_L = 50~\Omega$  mit einer Wechselsignalleistung  $P_L = 22,5~\text{mW}$  im Frequenzbereich bis f = 1~MHz und einer Offsetspannung  $U_{os} < 2~\text{mV}$ , bei einer Ruhe-Leistungsaufnahme  $P_{Cons} < 2~\text{mW}$ . Die Realisierung sollte in einer CMOS-Standardtechnologie mit der Versorgungsspannung  $U_B = 3,3~\text{V}$  erfolgen.

Die geforderte Zielspezifikation macht eine Scheitelspannung  $\hat{u}_o = 1.5 \text{ V}$  und damit eine Rail-to-Rail-Endstufe erforderlich. Zur Erfüllung der Linearitätsund Offsetanforderung wird in diesem Fall zusätzlich eine Vorverstärkerstufe benötigt, damit die Endstufe in eine Rückkopplung eingebettet werden kann [2]. Open-Loop-Verstärkung Angesetzt wird eine  $V_u = 80 \text{ dB}$  bei angeschlossenem Lastwiderstand. Um die Leistungsaufnahme gegenüber Schwankungen der Versorgungsspannung und Temperatur zu stabilisieren, wird zusätzlich eine Versorgungseinheit benötigt. Die hohe, vom Halbleiterhersteller spezifizierte Variabilität der Prozessparameter macht es erforderlich, dass diese bereits bei der Dimensionierung der Transistoren Berücksichtigung findet. Dies soll mit Hilfe eines Optimierungstools unter Beobachtung der zu erwartenden Gesamtausbeute erfolgen.

Im nun folgenden Kapitel 2 wird, ausgehend von den grundlegenden Prinzipien, das Schaltungskonzept erarbeitet. Ebenfalls wird der Weg zu einer ersten Dimensionierung der Bauelemente erläutert. Kapitel 3

zeigt Simulationsergebnisse dieser Vordimensionierung und Kapitel 4 den Weg zur Feindimensionierung unter dem Einsatz des Optimierungstools WiCkeD. Hierbei wird der Einfluss der Variabilität, sowohl hinsichtlich der Technologieparameter als auch der Geometriegrößen, in die Dimensionierung einbezogen [3]. Kapitel 5 zeigt schließlich die Hardware-Realisierung und stellt erste Messergebnisse dar. Kapitel 6 gibt eine kurze Zusammenfassung und endet mit dem Ausblick.

#### II. SCHALTUNGSKONZEPT

Eine Rail-to-Rail-Endstufe ist nur durch den Betrieb der Endstufentransistoren in Source-Schaltung möglich (Abbildung 1b). Die Ansteuerung dieser Transistoren und die Stabilisierung des Arbeitspunktes im AB-Betrieb sind aufwändiger als mit den klassischen Drain-Schaltungen. Außerdem resultiert daraus Spannungsverstärkung, die eine starke Abhängigkeit von der zu treibenden Last R<sub>L</sub> und dem Momentanwert der Signalspannung zeigt und damit zu Verzerrungen führt. Aus diesem Grund ist ein zusätzlicher Differenzverstärker erforderlich, so dass der gesamte Verstärker als rückgekoppelter Buffer betrieben werden kann. Die gesamte Signalspannung wirkt in diesem Fall als Gleichtaktsignal am Eingang des Differenzverstärkers, weshalb auch dieser Rail-to-Rail-Eigenschaft aufweisen muss (Abbildung 1a).

#### A. Rail-to-Rail-Eingangsstufe

Damit die Eingangs-Gleichtaktspannung den gesamten Bereich zwischen  $U_{DD}$  und  $U_{SS}$  abdeckt, kommt das bekannte Prinzip der kombinierten P- und NMOS-Differenzstufe zum Einsatz [4]-[7]. Zu beachten ist, dass der Bereich, in dem keiner der beiden Transistoren arbeitet (die sogenannte Dead Zone), vermieden wird. Das gesamte Eingangssignal wirkt als Gleichtaktspannung, was die Forderung nach hoher Gleichtaktunterdrückung zur Folge hat. Für die Stromspiegel sind daher Kaskodestromspiegel vorzusehen, die jeweils zwei im Sättigungsbereich betriebene Transistoren in Serie geschaltet beinhalten. Ihr minimaler Spannungsbedarf beträgt  $2U_{DS,sat}$ . Der Eingangs-Gleichtaktspannungsbereich wird dann bestimmt durch:

$$U_{i\sigma l \min} = U_{SS} + 2U_{DS sat} + U_{GS} \tag{1}$$

$$U_{igl,\text{max}} = U_{DD} - 2|U_{DS,sat}| - |U_{GS}|$$

(2)

Die Schnittstelle der Rail-to-Rail-Differenzstufe zur Endstufe bilden jeweils zwei differentielle Stromausgänge.

#### B. Rail-to-Rail -Ausgangsstufe

Die Ausgangsspannung der Endstufe nach Abbildung 1b wird begrenzt durch

$$U_{o,\text{max}} = U_{DD} - \left| U_{DS,\text{min}} \right| \tag{3}$$

und

$$U_{o\,\min} = U_{SS} + U_{DS\,\min} \tag{4}$$

Die Transistoren befinden sich in diesem Fall im Triodenbereich. Die minimale Drain-Source-Spannung  $U_{DS,min}$  ist abhängig vom Lastwiderstand  $R_L$ . Sie lässt sich bei Annahme maximaler Ansteuerspannung am Gate  $U_{GS} \approx U_{DD} - U_{SS}$  wie folgt berechnen:

$$U_{DS,\min} = U_B - U_{TH} + \frac{1}{\beta R_L} - \frac{1}{\beta} \sqrt{\left(\beta (U_B - U_{TH}) + \frac{1}{R_L}\right)^2 - 2\beta \frac{U_B}{R_L}}$$

(5)

wobei

$$\beta = k' \frac{W}{I} \tag{6}$$

und

$$U_B = U_{DD} - U_{SS} \tag{7}$$

Im Gegensatz zum CMOS-Inverter, bei welchem die Gateanschlüsse der Transistoren miteinander verschaltet sind und direkt angesteuert werden können, benötigen die Endstufentransistoren für den AB-Betrieb eine Ansteuerschaltung.

#### C. Ansteuerung der Endstufe

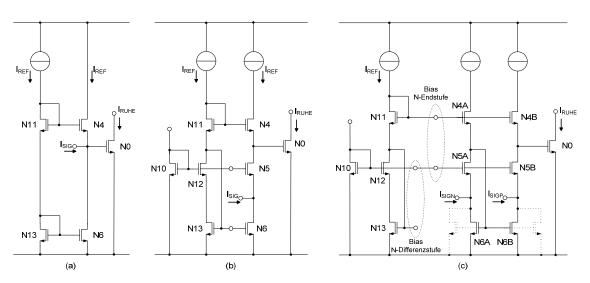

Die Grundschaltung zur Ruhestromeinstellung wird in Abbildung 2a aufgezeigt. Die Gate-Source-Spannung des Endstufentransistors N0 wird über die Gate-Source-Spannung der Transistoren N13, N11 und N4 festgelegt:

$$U_{GS0} = U_{GS13} + U_{GS11} - U_{GS4}$$

(8)

Da N0 ohne Signalstrom  $I_{Sig}$  im Sättigungsbereich betrieben wird, bestimmt sich damit der Ruhestrom zu

$$I_{RUHE} = \frac{k_n'}{2} \left(\frac{W}{L}\right)_0 (U_{GS0} - U_{THn})^2$$

(9)

Abbildung 2: Schaltungsevolution zur Endstufe: (a) Grundschaltung, (b) Low Voltage Kaskode, (c) symmetrische Erweiterung

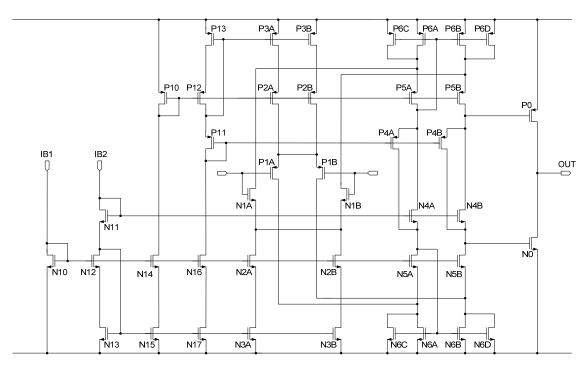

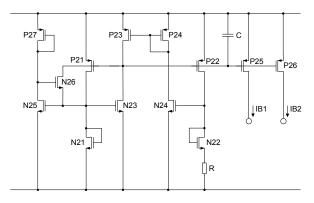

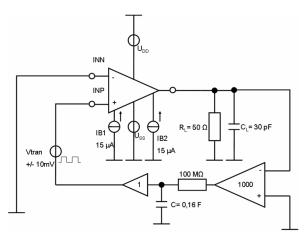

Abbildung 3: Gesamtschaltung des Verstärkerkerns

$I_{RUHE}$  ist also über  $I_{REF}$  und die W/L – Verhältnisse der Transistoren eindeutig festgelegt. Um ausreichende Spannungsverstärkung zu ermöglichen, muss der Stromeingang hochohmig sein. Die Kleinsignal-Gate-Source-Spannung von N0 wird aber durch die Source-Impedanz von N4 bestimmt:

$$u_{gs0} \approx \frac{1}{g_{m4}} i_{sig} \tag{10}$$

Die Transimpedanz  $u_{gs0}/i_{sig}$  ist damit zu klein für eine ausreichende Spannungsverstärkung des Gesamtverstärkers. Sie muss deshalb, wie in Abbildung 2b gezeigt, über den Einsatz der Kaskodetransistoren N10,

N12 und N5 erhöht werden. Der Knoten zur Einspeisung von  $i_{sig}$  bleibt nun weiterhin niederohmig, aber die Kleinsignal-Gate-Source-Spannung des Transistors N0 ergibt sich nun näherungsweise zu:

$$u_{gs0} = r_{05} (1 + g_{m5} r_{06}) i_{sig}$$

(11)

Um weiterhin den Ruhestrom über  $I_{REF}$  und die W/L-Verhältnisse zu fixieren, bedarf es weiterhin des Stromspiegels N11, N4 und einer zusätzlichen Stromquelle  $I_{REF}$ , um die Niederohmigkeit am Source-Knoten von N4 aufzuheben. Für den Betrieb bei niedriger Versorgungsspannung ist die Kaskodeschaltung als sogenannte Low-Voltage-Kaskode ausgeführt

(Verbindung des Gate-Anschlusses von N13 mit dem Drain-Anschluss von N12). Für eine symmetrische Signaleinkopplung, wie sie von der Differenzstufe geliefert wird, ist diese Version allerdings noch nicht nutzbar. Daher wird die Schaltung um eine symmetrische Kaskode erweitert (Abbildung 2c). Die Signaleinkopplung ist jetzt für beide Eingangsströme  $i_{sign}$  und  $i_{sigp}$  möglich. Die zusätzlichen Bias-Spannungen in der Schaltungsanordnung können unter anderem für die Differenzstufe genutzt werden. Infolge des Gleichstromanteils im Signalstrom muss der Transistor N6 vergrößert, z.B. verdoppelt werden. Zum Betrieb der positiven Halbwelle muss dieselbe Schaltung noch um ihr Spiegelbild, ausgeführt mit PMOS-Transistoren, ergänzt werden (Abbildung 3). Die Stromquellen sind dabei durch floatende Stromquellen (N4, P4) zu ersetzen. Nach Einfügen der Differenzstufe und weiterer Transistoren zur Festlegung der Bias-Spannungen ist die Konzeptphase des Verstärkerkerns abgeschlossen [8]. Der Verstärkerkern wird mit zwei Bias-Strömen  $I_{B1}$  und  $I_{B2}$  betrieben.

#### D. Vordimensionierung des Verstärkerkerns

#### 1) Endstufentransistoren

Um eine hohe Spannungsverstärkung zu erreichen, wird eine große Transkonduktanz angestrebt. Da die Exemplarstreuung der Endstufentransistoren für die Offsetspannung unerheblich ist, können diese mit der minimalen Kanallänge  $L=0,35~\mu m$  ausgeführt werden. Die gewünschte Scheitelspannung  $\hat{u}_o=1,50~V$  macht bei  $U_{SS}=-1,65~V$  nach Gl. 4 eine minimale Drain-Source-Spannung  $U_{DS,min}=150~mV$  am Transistor N0 erforderlich. Mit dem Lastwiderstand  $R_L=50~\Omega$  resultiert dann aus Gl. 5 und 6 eine Mindestkanalweite  $W=1100~\mu m$ .

#### 2) Stromspiegel

Um das Verhältnis von Ruhestrom in der Endstufe zum Ruhestrom in der restlichen Schaltung in einem vernünftigen Maß zu halten, sollte die Summe der einzelnen Drainströme nicht größer sein als der Drainstrom von N0. Der Strom durch die Differenzverstärker muss aber für eine hohe Bandbreite ausreichend groß sein. Um Abweichungen in den physikalischen Eigenschaften von identisch ausgelegten Transistoren zu vermeiden, sollten diese nach Möglichkeit gleich groß gewählt werden. Im einfachsten Fall ist

$$U_{GS13} = U_{GS0}$$

, (12)

was zu einer einheitlichen Gate-Source Spannung der Transistoren N13, N15, N17, N3, N6 bzw. N12, N14, N16, N2, N5 und Drain-Source Spannung der Transistoren N13, N15, N17, N3, N6 bzw. N12, N5 führt. Unter diesen Voraussetzungen und hinsichtlich des Ausgangswiderstandes, dem Ziel des Betriebs im Sät-

tigungsbereich und einem gewählten Drainstrom für alle Transistoren in Höhe von 15  $\mu$ A wurden die Werte für Kanalweite und -länge festgelegt ( $W=20~\mu\text{m}$ ,  $L=2~\mu\text{m}$ ).

#### 3) Kaskodetransistoren

Bei den Kaskodetransistoren N12, N14, N16, N2 und N5 ist nach Gl. 11 neben dem Ausgangswiderstand  $r_o$  auch die Transkonduktanz  $g_m$  von Bedeutung, während die Offsetspannung eine untergeordnete Rolle spielt. Ihre Dimensionierung wird daher auf  $W/L = 20 \ \mu\text{m}/1 \ \mu\text{m}$  angesetzt. Mit der Diodenschaltung N10 wird die Bias-Spannung  $U_{GSI0} = U_{DSI3,sat} + U_{GSI2} \approx 900 \ \text{mV}$  erzeugt. Mit der Wahl  $I_{B1} = I_{B2} = 15 \ \mu\text{A}$  und  $L_{10} = 1 \ \mu\text{m}$  ergibt sich daraus die Kanalweite  $W_{10} = 1,2 \ \mu\text{m}$ .

#### 4) Floatende Stromquellen

Die Transistoren P4A, N4A und P4B, N4B stellen jeweils eine floatende Stromquelle dar. Wenn sich unterhalb der Stromquelle die Spannung ändert, bleibt der Strom dennoch gleich. Das gleiche gilt für den Knoten oberhalb der Stromquellen. Da jeder einzelne Transistor P4A bzw. N4A nur die Hälfte des Stroms von N5A führt, wurde die halbe Kanalweite  $W_4 = 10~\mu \mathrm{m}$  festgelegt.

#### 5) Differenzstufentransistoren

Als Kompromiss zwischen den Zielgrößen: hohe Bandbreite, hohe Transkonduktanz, geringe Offsetspannung und geringe Fläche wurde die Kanallänge auf  $L=1,5\,\mu m$  angesetzt. Mit einem geringen Overdrive von  $\Delta U_{GS}=50\,\mathrm{mV}$  für eine hohe Verstärkung resultiert die Kanalweite  $W=100\,\mu m$ . Die Verstärkung setzt sich aus zwei Teilen zusammen. Die Steilheit der Differenzstufentransistoren multipliziert mit dem Widerstand am Gate-Knoten von N0 bildet den ersten Term und die Steilheit des Endstufentransistors N0 multipliziert mit dem Lastwiderstand  $R_L$  den zweiten:

$$V_u = (-g_{m1}(r_{05}(1 + g_{m5}r_{06})))(-g_{m0}R_L)$$

(13)

Die gleiche Verstärkung kommt noch einmal hinzu, wenn die PMOS-Transistoren symmetrisch zu den NMOS-Transistoren dimensioniert werden. Den PMOS-Transistoren wurde bei gleicher Kanallänge die jeweils doppelte Kanalweite gegeben. Die Biasströme  $I_{B1}$  und  $I_{B2}$  werden von einer Versorgungseinheit geliefert, welche im Folgenden beschrieben wird.

Abbildung 4: Schaltungsevolution der Versorgungseinheit: Grundschaltung (a), Erweiterung um Regelkreis (b), Eliminierung des dominanten Pols (c)

Abbildung 5: Gesamtschaltung Versorgungseinheit

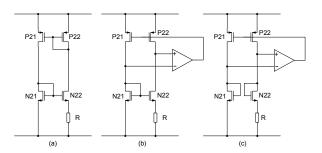

#### E. Entwicklung der Versorgungseinheit

Den Ansatz zur Versorgungseinheit bildet der Beta-Multiplizierer (Abbildung 4a). Er liefert einen konstanten Strom abhängig vom Absolutwert R, jedoch unabhängig von Temperatur und Versorgungsspannung, sofern R aus Teilen mit positiven und negativen Temperaturkoeffizienten zusammengesetzt ist [8]. Der Strom durch N22 wird dabei bestimmt durch die W/L-Verhältnisse von N22 und N21 zueinander:

$$I_{D22} = \frac{2}{R^2 k_n' \left(\frac{W}{L}\right)_{21}} \left(1 - \frac{1}{\left(\frac{W}{L}\right)_{22} / \left(\frac{W}{L}\right)_{21}}\right)^2 \tag{14}$$

Allerdings besitzt die Schaltung in dieser Form eine Nichtidealität. Unterschiedliche Drain-Source-Spannungen an den PMOS-Transistoren führen zu einem Fehler im Stromspiegel. Durch einen Regelkreis mit Hilfe eines OTAs<sup>1</sup>, dessen Ausgang an die Gateanschlüsse der PMOS-Transistoren geführt wird, kann dem entgegen gewirkt werden (Abbildung 4b).

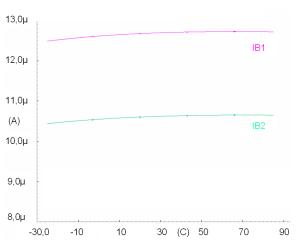

Abbildung 6: Biasströme in Abhängigkeit von der Temperatur

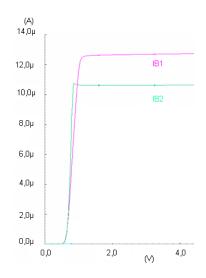

Abbildung 7: Biasströme in Abhängigkeit von der Versorgungsspannung

Dabei entstehen jedoch zwei dominante Pole, einer am Ausgang und einer am nichtinvertierenden Eingang des OTAs. Die führt zu Schwierigkeiten in der Frequenzgangkompensation. Eliminierung eines dominanten Pols wird erreicht, indem der Transistor N22 als Diode beschaltet wird (Abbildung 4c). Mit dieser Maßnahme ändert sich der DC-Wert nicht. Eine Startschaltung, eine Auskopplung und ein Kompensationskondensator werden noch benötigt, um die Versorgungseinheit zu komplettieren (Abbildung 5).

\_

<sup>&</sup>lt;sup>1</sup> Operational Transconductance Amplifier

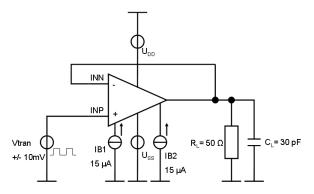

Abbildung 8: Testbench für die Transient- und DC-Analyse

Tabelle 1: Simulationsergebnisse nach der Vordimensionierung

| Performance                            | Spezifikation | Wert     |

|----------------------------------------|---------------|----------|

| Spannungsverstärkung $V_u$             | > 80 dB       | 104,8 dB |

| Ruhestrom Endstufe $I_{Ruhe}$          | < 500 μΑ      | 4,5 mA   |

| Max. AusgSpg. $U_{OUT,max}$            | > 1,5 V       | 1,56 V   |

| Min. AusgSpg. $U_{OUT,min}$            | <-1,5 V       | -1,6 V   |

| Phasenreserve $\boldsymbol{\varphi}_R$ | > 60°         | 29°      |

| Leistungsaufnahme $P_{cons}$           | < 2 mW        | 15,4 mW  |

| Transitfrequenz $f_T$                  | > 5 MHz       | 51 MHz   |

#### III. SCHALTUNGSSIMULATION

#### A. Simulation der Versorgungseinheit

Die Dimensionierung der W/L-Verhältnisse für die Versorgungseinheit soll hier nicht näher beschrieben werden. Die Simulation der beiden Bias-Ströme zeigt die Stabilität gegenüber der Temperatur- und Versorgungsspannungsänderung (Abbildungen 6 und 7).

#### B. Testbench für die Verstärkersimulation

Für die Transient- und die DC-Analyse muss der Ausgang des Verstärkers auf den invertierenden Eingang zurückgekoppelt werden (Abbildung 8). Der nichtinvertierende Eingang wird mit einer Spannungsquelle angesteuert. Zusätzlich sind noch die Versorgungsspannungen und die von der Versorgungseinheit gelieferten Biasströme anzulegen. Für die AC-Analyse bedarf es einer anderen Beschaltung (Abbildung 9). Der invertierende Eingang wird nicht mit dem Ausgang verbunden, sondern auf Masse gelegt. Der Gleichstromregelkreis sorgt dafür, dass die AC-Analyse im aktiven Bereich, unabhängig von der Offsetspannung, durchgeführt wird. Das Tiefpassfilter ist so ausgelegt, dass es im interessierenden Frequenzbereich nicht in die Verstärkung eingeht.

Abbildung 9: Testbench für die AC-Analyse

#### C. Simulation des Verstärkers

Tabelle 1 zeigt die Simulationsergebnisse des konzeptionierten Verstärkers. Die Verstärkung, die Transitfrequenz und die Aussteuergrenzen sind bereits innerhalb der Spezifikationsgrenzen. Allerdings ist der Ruhestrom viel zu hoch, die Phasenreserve zu niedrig und die Aussteuergrenzen sind unsymmetrisch. Um dem entgegen zu wirken, sind Optimierungsmaßnahmen per Hand denkbar. Das Absenken des Ruhestroms wird durch starke Reduzierung des W/L-Verhältnisses von P4B und N4B gegenüber P4A und N4A erreicht. Durch die Low-Voltage-Kaskode wird allerdings die Drain-Spannung von N5A festgehalten, weshalb das symmetrische Verhältnis von N4A zu N4B aufgegeben werden muss. Symmetrische Aussteuergrenzen werden erreicht, indem die W/L-Verhältnisse der Endstufentransistoren N0 und P0 angepasst werden. Anstelle dieser manuellen Vorgehensweise sollte die weitere Dimensionierung mit Hilfe eines Optimierungstools erfolgen.

#### IV. ENTWURFSOPTIMIERUNG

#### A. Optimierungstool WiCkeD

Dieses Optimierungstool der Fa. MunEDA wurde bereits in [9] vorgestellt. Es verfügt über drei Optimierungsarten. Die Feasibitity Optimization konzentriert sich auf die Optimierung hinsichtlich Nebenbedingungen. Am Beispiel einer N-Differenzstufe sind das die Bedingungen des Betriebs in Inversion, einer bestimmten Mindestfläche, welche den Mismatch durch die Transistoreinsatzspannung begrenzt und die Forderung nach gleicher Kanallänge und –weite. Die Optimierung in Bezug auf die Performance (sog. Nominal Optimization) führt die Kenndaten über mehrere Iterationsschritte in die vorgegebenen Spezifikationen hinein. Die rechenintensivste Optimierung richtet ihr Augenmerk auf die Verbesserung der Ausbeute (Yield Optimization).

Tabelle 2: Simulationsergebnisse nach der Nominal Optimization

| Performance                   | Spezifikation | Wert      |

|-------------------------------|---------------|-----------|

| Spannungsverstärkung $V_u$    | > 80 dB       | 82,4 dB   |

| Ruhestrom Endstufe $I_{Ruhe}$ | < 500 μΑ      | 337,6 μΑ  |

| Max. AusgSpg. $U_{OUT,max}$   | > 1,5 V       | 1,58 V    |

| Min. AusgSpg. $U_{OUT,min}$   | <-1,5 V       | -1,59 V   |

| Phasenreserve $\varphi_R$     | > 60°         | 83,8°     |

| Leistungsaufnahme $P_{cons}$  | < 2 mW        | 1,6 mW    |

| Transitfrequenz $f_T$         | > 5 MHz       | 13,05 MHz |

Durch die Designzentrierung, eine Verschiebung des Designs innerhalb des mehrdimensionalen Spezifikationsraums, wird die Schaltung unempfindlicher gegenüber Parameterstreuungen und Fertigungstoleranzen. Da zur Gesamtoptimierung unterschiedliche Testbenches in einem Lauf nötig sind, wurden diese mit Hilfe von Umschaltern festgelegt.

#### B. Entwurfszentrierung mit WiCkeD

#### 1) Feasibility Optimization

Um die Nebenbedingungen zu erfüllen, kann zwischen zwei Algorithmen gewählt werden. "Find closest point" sucht den kürzesten Abstand, um das Design in der Feasibility Region zu platzieren. Der von uns verwendete Algorithmus "find central point" bringt das Design zusätzlich noch in die Mitte der Feasibility Region. Die Nebenbedingungen konnten durch kleine Änderungen in den W/L-Verhältnissen erfüllt werden. Die Simulationszeit für zwei Iterationsschritte beträgt zwölf Minuten. Alle Transistoren befinden sich im Bereich der Feasibility Region. Damit wurde der bestmögliche Startpunkt für die nachfolgende Nominal Optimization gefunden.

#### 2) Nominal Optimization

Die Optimierung hinsichtlich der Zielspezifikationen konnte alle Werte in die vorgegebenen Grenzen führen (Tabelle 2). Die Simulationszeit für drei Iterationsschritte beträgt eine Stunde. Ein Vergleich der W/L-Verhältnisse mit den Werten aus der Vordimensionierung zeigt, wie die Spezifikationen erreicht wurden. Der Optimierer hat alle W/L-Verhältnisse verändert, aber die maßgeblichen Änderungen sind in der floatenden Stromquelle und den Endstufentransistoren zu finden (Tabelle 3). Die Symmetrie in der floatenden Stromquelle wurde aufgegeben. Dadurch konnte der Ruhestrom auf 337,6  $\mu A$  reduziert werden. Gleichzeitig verringerte sich die Verstärkung auf 82,4 dB, was aber immer noch innerhalb der Spezifikationsgrenzen liegt.

Tabelle 3: Transitorgrößen nach der Nominal Optimization

| Transistor | <i>W</i> (μm) | L (µm) |

|------------|---------------|--------|

| P1A,B      | 209           | 1,6    |

| N1A,B      | 106           | 4,8    |

| P4A        | 29            | 5      |

| P4B        | 10            | 5      |

| N4A        | 33,4          | 1,5    |

| N4B        | 6             | 1,5    |

| P0         | 2990          | 0,36   |

| N0         | 870           | 0,35   |

Mit dem Herabsetzen des Ruhestroms konnte auch die gesamte Leistungsaufnahme auf 1,6 mW gesenkt werden. Die Reserven in der Transitfrequenz konnten gegen eine Erhöhung der Phasenreserve auf 83,3° eingetauscht werden. Die Transitfrequenz ist mit 13,05 MHz immer noch ausreichend weit entfernt von der festgelegten Grenze (> 5 MHz). Bei der Betrachtung der optimierten W/L-Verhältnisse ist allerdings das unübliche Aspect Ratio der Differenzstufen  $(W/L)_{P1}/(W/L)_{N1}$  auffällig (~ 6). Nach erfolgreicher Nominal-Optimierung konnte die Ausbeute mit der Monte Carlo-Analyse abgeschätzt und beurteilt werden.

#### 3) Monte Carlo-Analyse

Neben den drei Optimierungsarten besitzt WiCkeD eine Reihe von Analysemöglichkeiten. Mit der Monte Carlo-Analyse kann die Gesamt- und Einzelausbeute simuliert werden. Die Gesamtausbeute in Höhe von 70 % wird durch die Einzelausbeute der Verstärkung (93 %), des Ruhestroms (82 %) und der Offsetspannung (94 %) bestimmt. Die Simulationszeit für 100 Samples beträgt eine Stunde.

#### 4) Yield Optimization

Im Anschluss an die Monte Carlo-Analyse wird durch die Yield Optimization die Ausbeute erhöht. Die Simulationszeit für zwei Iterationsschritte beträgt zwei Tage. Die Ausbeuteoptimierung konzentriert sich auf die Verstärkung und den Ruhestrom. Sie führt das Aspect Ratio der Differenzstufe zurück auf einen vernünftigen Wert von ca. 3 ( $W=209~\mu\text{m}$ ,  $L=2,8~\mu\text{m}$  für P1A,B und  $W=125~\mu\text{m}$ ,  $L=4,7~\mu\text{m}$  für N1A,B). Die Ausbeute konnte damit um 8 % auf 78 % erhöht werden. Für eine Serienproduktion wäre dieser Wert noch nicht zufriedenstellend. Aus Zeitgründen wurde jedoch sogleich mit der Hardwarerealisierung begonnen.

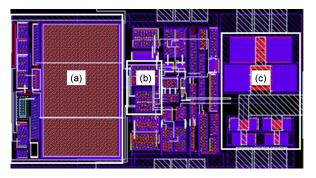

Abbildung 10: Layout (Corebereich): (a) Versorgungseinheit, (b) Differenzstufentransistoren und (c) Endstufe.

Abbildung 11: Chipfoto

#### V. HARDWAREREALISIERUNG

#### A. Layoutentwurf

Abbildung 10 zeigt die Aufteilung in die Versorgungseinheit, die Differenzstufe als Quadlayout und die Endstufe. Aufgrund der Wärmeentwicklung der Endstufe wurde diese so weit wie möglich von der Differenzstufe entfernt platziert. Die Stromdichte im Metall zwingt zu einer Aufteilung der Endstufentransistoren. Der PMOS-Transistor wird vierfach, der NMOS-Transistor achtfach angeordnet.

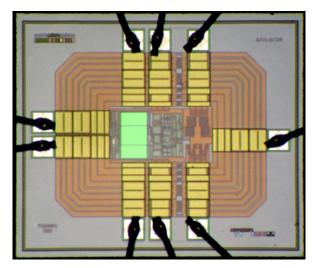

#### B. Gefertigter Chip

In Abbildung 11 ist der Verstärkerkern mit den Anschlusspins zu sehen mit den beiden Eingängen auf der linken und dem Ausgang auf der rechten Seite. Oben und unten befinden sich die Pins für die Versorgungsspannung der Versorgungseinheit und der Verstärkerstufe und die Leistungspins für die Versorgungsspannung der Endstufe. Zusätzlich sind Pins für die Biasströme  $I_{BI}$  und  $I_{B2}$  zu Testzwecken herausgeführt. Die Chipfläche beträgt 1190  $\mu$ m x 1000  $\mu$ m, die des Core-Bereichs 450  $\mu$ m x 230  $\mu$ m.

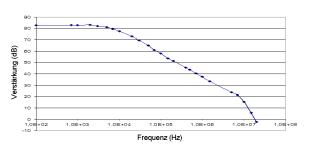

Abbildung 12: Frequenzgang der Verstärkung mit Last, jedoch ohne Rückkopplung

Abbildung 13: Spannungsbegrenzung am Ausgang

#### C. Messungen am Chip

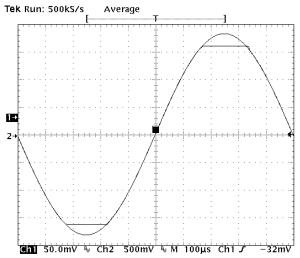

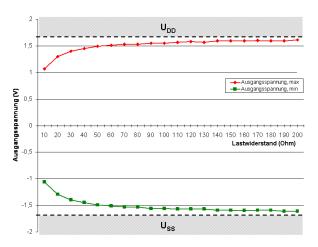

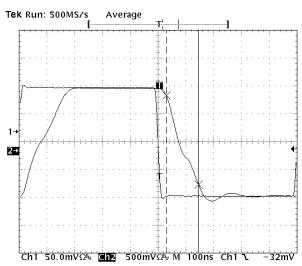

Im Bodediagramm, welches bei einer speziellen Ausgangsgleichspannung  $U_o = 0.5 \text{ V}$  aufgenommen wurde (Abbildung 12), ist zu sehen, dass vor Erreichen der Transitfrequenz ein Pol auftaucht. Dieser führt zur Instabilität des Verstärkers bei Rückkopplung als Unity Gain Buffer. Die Abhängigkeit der Phasenreserve von der Ausgangsspannung, welche in der Simulation nicht ausreichend berücksichtigt wurde, ist der Grund für diesen unerwünschten Effekt. Für die Messung des Aussteuerbereichs musste daher auf den Verstärkungsfaktor 10 zurückgekoppelt werden. Abbildung 13 zeigt die Begrenzung des Aussteuerbereichs bei Ansteuerung mit einem Sinussignal. Abbildung 14 zeigt den Aussteuerbereich als Funktion des Lastwiderstands R<sub>L</sub>. Mit derselben Messeinrichtung wurde die Impulsantwort an  $R_L = 50 \Omega$  aufgenommen (Abbildung 15). Der Übergang im Nulldurchgang ist typisch für diese Art Verstärker, da die Verstärkung der Endstufe vom momentanen Ausgangsstrom abhängt.

Abbildung 14: Spannungsbegrenzung in Abhängigkeit vom Lastwiderstand  $R_{\rm L}$

#### VI. ZUSAMMENFASSUNG UND AUSBLICK

Für batteriebetriebene Systeme in der Kommunikations-, Medizin- und Sensortechnik wurde eine lineare Leistungsstufe entwickelt und um eine Versorgungseinheit erweitert. Durch den Entwurf einer Testbench konnte die Schaltung mittels WiCkeD optimiert werden. Nach dem Layoutentwurf für den IP-Core wurde der Chip gefertigt, in die aufgebaute Messumgebung eingebettet und verifiziert.

Dabei konnten die wichtigsten Ziele wie Aussteuerbereich, Verstärkung, Offsetspannung, Ruhestrom und Bandbreite erreicht werden. Das Optimierungstool wurde bei der Dimensionierung effizient eingesetzt. Neben der verbesserten Kompensation des Verstärkers zur Frequenzstabilisierung besteht Verbesserungspotential in der weiteren Optimierung mit dem Ziel höherer Ausbeute. Dazu sollen neue WiCkeD Features genutzt werden.

#### DANKSAGUNG

Die Autoren bedanken sich bei Eugen Ringwald und Josef Schäfer für die technische Unterstützung während des gesamten Projekts, bei Alice Frapsauce, Oliver Graf und Franz Gritschneder für ihre Arbeit am Simulator, bei Jens Rechtsteiner für die Erstellung des Layouts und bei Patricia Kruger und Marisa Mitchell für Aufbau und Test.

#### LITERATURVERZEICHNIS

- G. Ferri, W. Sansen, "A Rail-to-Rail Constant-gm Low-Voltage CMOS Operational Transconductance Amplifier" *IEEE Journal of solid-state Circuits*, Vol. 32, No. 10, Oktober 1997.

- [2] S. Gierkink et al., "Some Design Aspects of a Two-Stage Rail-to-Rail CMOS Op Amp" Analog Integrated Circuits and Signal Processing, Kluwer Academic Publisher, Juli 1998.

- [3] H. E. Graeb, "Analog Design Centering and Sizing", Springer, Dordrecht 2007.

Abbildung 15: Impulsantwort

- [4] T. Stockstad, "A 0.9-V 0.5-μA Rail-to-Rail CMOS Operational Amplifier" *IEEE Journal of solid-state Circuits*, Vol. 37, No. 3, März 2002.

- [5] J. H. Huijsing, D. Linebarger, "Low-Voltage Operational Amplifier with Rail-to-Rail Input and Output Ranges" *IEEE Journal of solid-state Circuits*, Vol. Sc-20, No. 6, Dezember 1985.

- [6] J. A. Fisher, R. Koch, "A Highly Linear CMOS Buffer Amplifier" *IEEE Journal of solid-state Circuits*, Vol. Sc-22, No. 3, Juni 1987.

- [7] M. D. Pardoen, M. G. Degrauwe, "A Rail-to-Rail Input/ Output CMOS Power Amplifier" *IEEE Journal of solid-state Circuits*, Vol. 25, No. 2, April 1990.

- [8] R. J. Baker, "CMOS Circuit Design, Layout, and Simulation" *IEEE Press*, Piscataway 2005.

- [9] F. Mrugalla, G. Vallant, G. Forster, "Dimensionierung und Entwurfszentrierung analoger Schaltungen mit WiCkeD" Workshop der Multiprojekt-Chip-Gruppe Baden-Württemberg, Karlsruhe, Juli 2009.

Lukas Schumm ist seit dem Abschluss seines Bachelorstudiums 2010 Wissenschaftlicher Mitarbeiter an der Fakultät Elektrotechnik der Hochschule Ulm. Er befasst sich mit der Schaltungsentwicklung und –optimierung. Er absolviert ein Masterstudium in Systems Engineering and Management, welches er voraussichtlich im Sommersemester 2012 abschließen wird.

Gerhard Forster ist seit 1992 Professor für Elektronik und Mikroelektronische Schaltungen an der Hochschule Ulm. Sein Schwerpunkt liegt auf dem Gebiet des Entwurfs von Mixed-Signal-ASICs. Nach seinem Studium der Physik an der Universität Heidelberg befasste er sich zunächst in einer Forschungsabteilung (heute Daimler Forschungszentrum) mit der Entwicklung und Anwendung neuer Halbleiterprozesse. Er ist Herausgeber des vorliegenden Tagungsbandes.

# Universeller Sensorsignalkonverter für TDC-basierte digitale Sensorik

Daniel Fuchs, Andreas Brönner, Ulrich Brunsmann

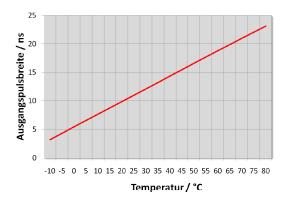

Zusammenfassung-Das Konzept eines universellen Sensorsignalkonverters (US<sup>2</sup>C) auf Basis der Zeit-zu-digital Wandlung ist Thema dieser Veröffentlichung. Die Hauptkomponenten des Systems, ein Signal-zu-Puls Generator (SPC), ein Zeit-zu-Digital Wandler (TDC) sowie ein OnChip Temperatursensor werden auf dem konfigurierbaren CMOS-Chip HAB10 integriert, der in 150nm Technologie gefertigt werden wird. Eine bereits realisierte diskrete analoge Sensoranpassschaltung ermöglicht die Auswahl des Sensoreingangs. Zu den sieben vorkonfigurierten Sensoren gehören Druck- sowie Temperatursensoren. Durch präzise Pulse sensorgrößenabhängiger Dauer, generiert von einem Signal-zu-Puls Wandler und gemessen von einem hochauflösenden TDC, wird in der Simulation bei einer Auflösung von 12-Bit eine Sensormessrate von 2 kHz erreicht. Der OnChip Temperatursensor ist für einen Temperaturbereich von -10 bis 80 °C bei einer Messrate von 500 Hz zur Kompensation temperaturabhängiger ausgelegt.

Schlüsselwörter—CMOS, Verzögerungsstrecke, Signalverarbeitung, Sensorik, konfigurierbare Verzögerung, OnChip Temperatursensor.

#### I. EINLEITUNG

Die Wandlung von Sensorsignalen ist ein unverzichtbarer Bestandteil der Prozessindustrie. Sensor-Messumformer, basierend auf der herkömmlichen Analog-zu-Digital Wandlung (ADC) überfluten den Markt. Mit Beginn der 80er Jahre wurden neben mechanischen Messumformern, die ersten elektronischen Messumformer entwickelt. Hierbei stellten elektronische Druckmessumformer [1] den Anfang einer rasanten Entwicklung in der elektronischen Sensorsignalverarbeitung dar. Heute verfügen elektronische Transmitter über eine kundenspezifische Online-Konfiguration via Software, erzeugen als Ausgangssignal meist ein normiertes analoges elektrisches Einheitssignal von 4 mA bis 20 mA und kommunizieren

Daniel Fuchs, daniel.fuchs@h-ab.de / d.fuchs@wika.de, Andreas Brönner, andreas.broenner@h-ab.de und Ulrich Brunsmann, ulrich.brunsmann@h-ab.de, sind Mitarbeiter der Hochschule Aschaffenburg, Fakultät Ingenieurwissenschaften, Labor für elektronische Bauelemente und Chipdesign, Würzburger Straße 45, 63743 Aschaffenburg.

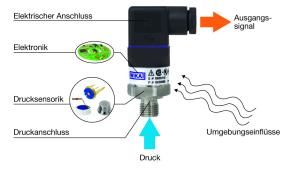

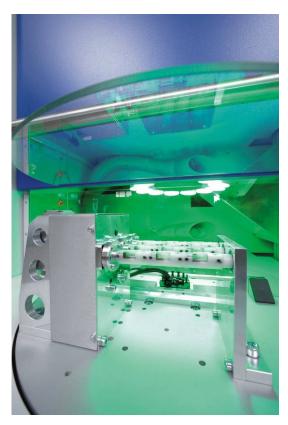

Abbildung 1: Beispielhafter Aufbau eines Drucktransmitters. (Quelle: WIKA, Alexander Wiegand SE & Co. KG)

mit der Außenwelt per Bluetooth oder HART-Protokoll. Elektronische Messumformer finden Anwendung in zahlreichen Industriesektoren, dazu gehören:

- Energietechnik

- Erneuerbare Energien

- Automotive

- Lebensmittelbranche

- Pharmaindustrie

- Maschinenbau.

Mehr als 60% aller industriell erfassten Sensordaten stammen von Druck- bzw. Temperatursensoren. Die zur Konvertierung verwendeten Messumformer verfügen in der Regel über eine herkömmliche A/D Wandlung des Sensorsignals sowie über eine digitale Signalverarbeitung mit Hilfe von Mikrocontrollern ( $\mu$ C). In Abbildung 1 ist beispielhaft der Aufbau eines aktuellen Drucktransmitters dargestellt. Die technische Herausforderung liegt bei heutigen Entwicklungen vor allem im knappen Energiehaushalt dieser Produkte, der Stromverbrauch der gesamten Elektronik darf maximal bei ca. 3 mA liegen.

Der hier vorgestellte universelle Sensorsignalkonverter auf Basis der Zeit-zu-Digital Wandlung [2] stellt ein Konzept dar, welches neue Wege in der Digitalisierung von Sensorsignalen sowie der Signalverarbeitung aufweist. Mit dem Ziel, zukünftig einen universellen Sensorsignal-ASIC einzusetzen, ist diese Arbeit ein erster Schritt hinsichtlich einer solchen Entwicklung. Die Faktoren Stromverbrauch, Messrate, Kosten, Platzbedarf und Wiederverwendbarkeit spiel-

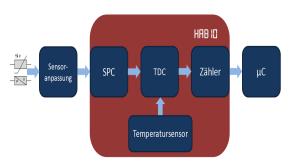

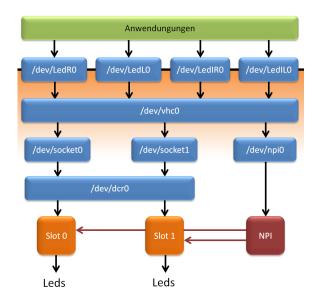

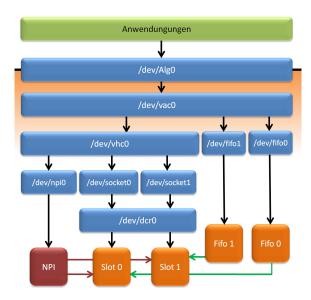

Abbildung 2: Blockschaltbild des universellen Sensorsignalkonverters.

ten bei der Konzeptionierung dieses Systems eine ausschlaggebende Rolle. Ausgelegt ist der US<sup>2</sup>C in erster Linie für Druck- und Temperatursensoren [3], weitere Sensorarten können angepasst werden.

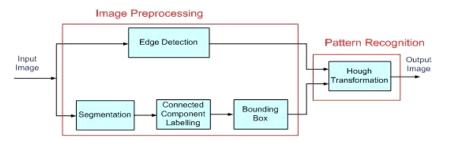

Im Folgenden wird zunächst in Abschnitt II die Funktionsweise des Gesamtsystems beschrieben, welches in Abbildung 2 schematisch dargestellt ist. Zudem wird in diesem Abschnitt die Entwicklungsumgebung vorgestellt. Daraufhin gehen wir in Abschnitt III auf Aufbau und Funktion der Einzelkomponenten ein. In Abschnitt IV wird der Messablauf des Systems im Detail behandelt. Die Simulationsergebnisse werden in Abschnitt V präsentiert. Es folgt ein Fazit sowie ein Ausblick auf zukünftige Arbeiten.

## II. AUFBAU UND FUNKTIONSWEISE DES UNIVERSELLEN SENSORSIGNALKONVERTERS

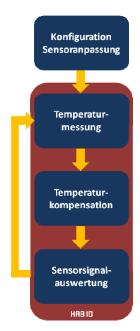

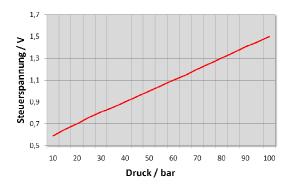

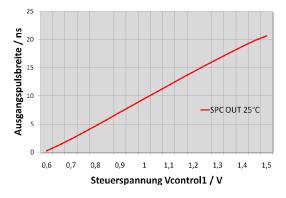

Der US<sup>2</sup>C stellt zum Einen im Sensorsignalpfad das Ergebnis einer Sensorsignalwandlung digital am Ausgang zur Verfügung. Zum Anderen ist das System dazu ausgelegt, die OnChip Temperatur [4] digital auszugeben. Abbildung 2 zeigt das Blockschaltbild der einzelnen Systemkomponenten. Sensorsignale am Eingang des US<sup>2</sup>C werden von der diskret realisierten Sensoranpassschaltung in einen definierten Steuerspannungsbereich von 0,6 bis 1,5 V angehoben. Dies geschieht durch externe Beschaltung eines Instrumentenverstärkers. Die Sensoranpassung dient somit als Schnittstelle zwischen den Sensoren am Eingang des US<sup>2</sup>C und der Eingangsstufe des SPC auf dem HAB10. Steuerspannungsabhängige Ausgangspulse, deren Dauer von dem zu messenden Sensorsignal abhängt, werden vom SPC generiert. Der sensorgrö-Benabhängige Anteil an der Dauer des Ausgangspulses beträgt maximal 30 ns, dessen Zeitoffset ist durch Konfiguration flexibel einstellbar. Ebenfalls durch Konfiguration kann der SPC in einen linearen OnChip Temperatursensor für einen Temperaturbereich von -10 bis 80 °C umgewandelt werden. Anders als bei der Auswertung des Sensorsignals sind die Ausgangspulse hierbei temperaturabhängig. Der zyklische Pulsschwund TDC [5] verkürzt den sensorgrößenabhängigen Eingangspuls zyklisch um einen als Pulsschwund bezeichneten Betrag. Die Gesamtzahl der Durchläufe, welche benötigt werden, um den Ein-

Abbildung 3: Diskret realisierte Sensoranpassschaltung.

gangspuls zu eliminieren, wird von einem nachfolgenden Zähler erfasst. Der Zählerstand enthält somit die Information über die Messgröße bzw. die OnChip Temperatur. Die Auswertung des Zählerstandes und die anwendungsspezifische Konfiguration des Systems gehören zu den Aufgaben des nachgeschalteten  $\mu C$ .

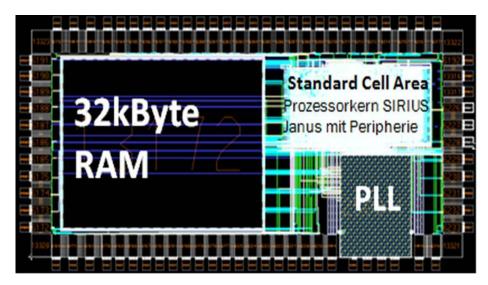

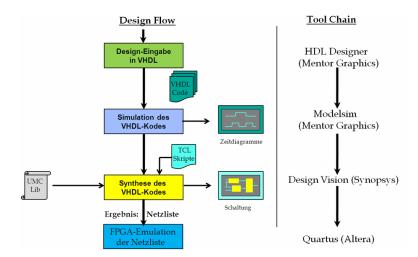

#### A. Die Entwicklungsumgebung und der Fertigungsprozess des Chips HAB10

Das Herzstück der Entwicklung stellt der CMOS-Chip HAB10 dar, auf welchem der SPC bzw. OnChip Temperatursensor, der TDC sowie ein Zähler integriert sind. Der Schaltungsentwurf des HAB10 erfolgt mit der Entwicklungsumgebung Tanner Tools Pro V.15 Design Suite. Im Design Flow befindet sich der Chip aktuell in der Layout-Phase, im Folgenden werden die Simulationsergebnisse präsentiert. Ein Großteil der Hauptkomponenten wird im full-custom Design entwickelt, der Zähler ist aus Standardzellen aufgebaut. Der Halbleiterchip wird in einen 150 nm CMOS Prozess in Kooperation mit EUROPRACTICE gefertigt.

#### III. EINZELKOMPONENTEN DES US<sup>2</sup>C

Im Rahmen dieser Arbeit werden ausschließlich die Sensoranpassschaltung sowie die Signal-zu-Puls Konvertierung (SPC) im Detail beschrieben. Die Entwicklung des zyklischen Pulsschwund TDC ist nicht Gegenstand dieser Arbeit.

#### A. Die Sensoranpassschaltung

Die analoge Sensoranpassschaltung wurde mit dem Ziel entwickelt, eine möglichst universell einsetzbare Schnittstelle zwischen Sensorik und Halbleiterchip zu realisieren. Bisherige Schwerpunkte sind die Druckund Temperaturmessung. Zentrales Element stellt der Instrumentenverstärker INA333 [6] (Texas Instruments) dar. Durch externe Beschaltung werden Verstärkung und Offsetspannung so eingestellt, dass Sensorsignale am Eingang dem definierten Steuerspannungsbereich des SPC angepasst werden. Die Auswahl des Sensors erfolgt durch Jumpereinstellung. Zu den Sensorsignalen gehören sieben bereits vorkonfigurierte Sensortypen (Tabelle 1), welche einen breiten Einsatz in industriellen Prozessen finden.

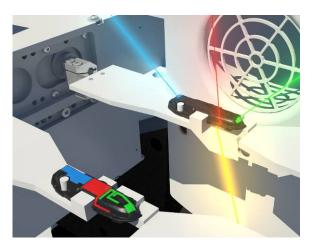

Abbildung 4: Aufbau des konfigurierbaren Signal zu Puls Konverters (SPC).

Tabelle 1: Übersicht der vorkonfigurierten Sensortypen zum Anschluss an die Sensoranpassschaltung.

| Sensortyp                      | Phsyikalische<br>Größe |

|--------------------------------|------------------------|

| Metall – Dünnfilm - Sensor     | Druck                  |

| Keramik – Dickschicht - Sensor | Druck                  |

| Piezoresistiver Sensor         | Druck                  |

| Thermoelement Typ K / L        | Temperatur             |

| Pt100 / Pt1000 Widerstands-    | Temperatur             |

| thermometer                    |                        |

Neben diesen können weitere Sensoren ausgewertet werden. Dazu wird eine externe Sensorschaltung durch Buchsen (siehe Abbildung 3) mit der Anpassung verbunden. Für die Sensorauswertung sind wahlweise eine Konstanspannungs- als auch eine Konstantstromquelle vorgesehen. Die Stabilität des Aufbaus gegen externe Störungen und Temperaturschwankungen wurde durch Messungen in der EMV-sowie in der Temperatur-Kammer bestätigt. Die Anpassschaltung stellt am Ausgang dem nachfolgenden SPC ein Signal mit einer maximalen Spanne von 900 mV und einer minimalen Spanne von 400 mV bei einem Offset zwischen 600 mV und 1,1 V zur Verfügung.

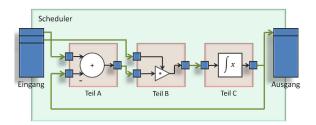

#### B. Der SPC mit OnChip Temperatursensor

Die Funktion des SPC wird aus drei Konfigurationsmöglichkeiten durch externe Beschaltung eingestellt. Diese sind:

- OnChip Temperaturmessung

- Sensorsignalwandlung

- Differentielle Sensorsignalwandlung

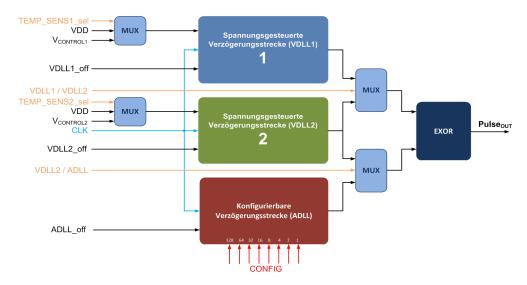

Wie in Abbildung 4 erkennbar besteht der SPC aus zwei identischen spannungsgesteuerten und einer

Abbildung 5: Blockweiser Aufbau der spannungsgesteuerten Verzögerungsstrecke.

konfigurierbaren Verzögerungsstrecke [7]. Zur Energieeinsparung ist es möglich, einzelne Verzögerungsstrecken durch Aktivierung der Pins VDLL1\_off, VDLL2\_off bzw. ADLL\_off bei Bedarf abzuschalten. Die Selektionspins TEMP\_SENS1\_sel bzw. TEMP\_SENS2\_sel zum Starten der Temperaturmessung an den Multiplexern (links im Bild), werden je nach Konfiguration des Systems gesetzt. Die Wahl der gewünschten Ausgangspulse zur Differenzbildung durch das EXOR-Gatter erfolgt durch Beschaltung der Multiplexer (rechts im Bild). Die Funktionsweisen der spannungsgesteuerten bzw. konfigurierbaren Verzögerungsstrecken werden nachfolgend beschrieben.

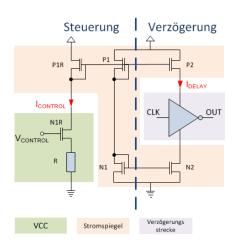

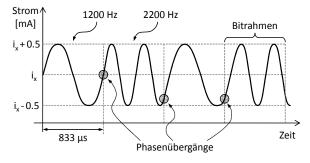

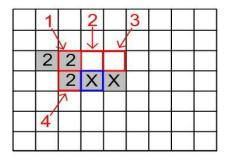

#### 1) Die spannungsgesteuerte Verzögerungsstrecke

Das Funktionsprinzip einer spannungsgesteuerten Verzögerungsstrecke (VDLL) ist in Abbildung 5 illustriert [8]. Die von der Sensoranpassung generierte sensorgrößenabhängige Steuerspannung  $V_{\rm CONTROL}$  am Eingang des Spannungs-zu-Strom Konverters (VCC),

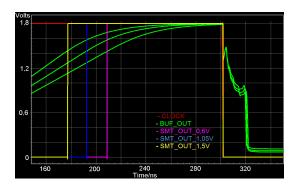

Abbildung 6: Simulationsergebnis des Ausganspulses (SMT\_OUT\_xxV) der spannungsgesteuerten Verzögerungsstrecke für die Steuerspannungen 0,6 V, 1,05 V und 1,5 V. Das Ausgangssignal der Inverterzelle vor dem Schmitt-Trigger (BUF\_OUT) ist grün bzw. das zu verzögernde Taktsignal (CLOCK) rot gekennzeichnet.

wird in einen linearen Steuerstrom  $I_{CONTROL}$  zwischen 5 bis 55  $\mu A$  konvertiert. Durch die Stromspiegel P1R, P1 und P2 sowie N1 und N2 wird dieser Steuerstrom in den für eine Verzögerung von max. 30 ns benötigten Arbeitsstrom  $I_{DELAY}$  von 80 bis 105  $\mu A$  angehoben. Dieser Strom, der durch das Verzögerungsglied bestehend aus Invertergattern fließt, bestimmt dessen stromabhängige Schaltzeiten  $t_{pHL}$  bzw.  $t_{pLH}$  [5].

$$t_{pHL} = \frac{C_{load}}{\mu_n C_{OX}(V_{DD} - V_{Tn})} \frac{L}{W} \left[ \frac{2V_{Tn}}{V_{DD} - V_{Tn}} + ln \left( \frac{4(V_{DD} - V_{Tn})}{V_{DD}} \right) - 1 \right]$$

$$t_{pLH} = \frac{C_{load}}{\mu_{p}C_{OX}(V_{DD} - |V_{Tp}|)} \frac{L}{W} \left[ \frac{2|V_{Tp}|}{V_{DD} - |V_{Tp}|} + ln \left( \frac{4(V_{DD} - |V_{Tp}|)}{V_{DD}} \right) - 1 \right]$$

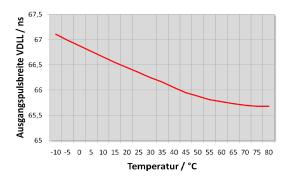

Um die gewünschte Verzögerung zu erzielen, besteht das Verzögerungsglied aus einer Aneinanderreihung zwölf identischer Inverterzellen, wobei jede Inverterzelle aus fünf parallelgeschalteten Invertergattern aufgebaut ist, um die Lade- bzw. Entladekapazität der Inverterzelle zu erhöhen. Für einen definierten Schaltpunkt sorgt ein abschließender Schmitt-Trigger [8], welcher bei Erreichen des oberen Schaltpunktes  $V_{SPH}$  = 1,4 V den Ausgangspuls bei steigender Taktflanke generiert. Der untere Schaltpunkt des Schmitt-Triggers V<sub>SPL</sub> spielt hier keine Rolle, da die fallende Flanke des Ausgangspulses mit fallender Taktflanke erzeugt wird. Die Erzeugung des Ausgangspulses der spannungsgesteuerten Verzögerungsstrecke für drei unterschiedliche Steuerspannungen wird durch das Simulationsergebnis in Abbildung 6 beschrieben. Die Temperaturabhängigkeit der VDLL nimmt mit steigender Steuerspannung ab. Die minimale Temperaturabhängigkeit liegt durch entsprechende Dimensionierung im Punkt V<sub>CONTROL</sub> = V<sub>DD</sub>, hier ist die Verzögerungszeit über einen Temperaturbereich von -10 bis 80 °C nahezu konstant (Simulationsergebnis Abbildung 11). Diese Eigenschaft der VDLL wird in der Konfiguration "Temperatursensor" zur Referenzmessung verwendet.

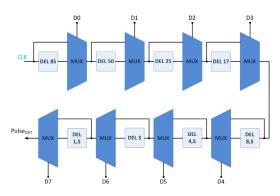

Abbildung 7: Aufbau der konfigurierbaren Verzögerungsstrecke bestehend aus acht Verzögerungszellen und acht Multiplexern. Die Ziffern innerhalb der Verzögerungsblöcke beschreiben deren Verzögerungszeit in ns bei "typical-mean" Bedingungen.

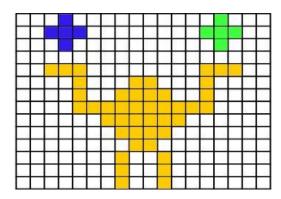

#### 2) Die konfigurierbare Verzögerungsstrecke

Die konfigurierbare Verzögerungsstrecke (ADLL) besteht aus acht unterschiedlichen Verzögerungsgliedern und acht Multiplexern [7]. Die Verzögerungsglieder unterscheiden sich in der Anzahl von Invertergattern und damit durch ihre unterschiedlichen Verzögerungszeiten. Durch externe Beschaltung der Multiplexer werden die einzelnen Verzögerungsglieder aktiv bzw. inaktiv geschaltet (Abbildung 7). Die Verzögerungszeit der ADLL berechnet sich somit zu:

$$t_{pADLL} = 8 \times t_{pMUX} + \sum t_{pDEL,AKTIV}$$

Durch die variable Verzögerungszeit ist es möglich, Temperaturabhängigkeiten entgegenzuwirken oder Offsetzeiten einzustellen, wobei unter Vernachlässigung der Verzögerungszeiten der Multiplexer t<sub>pMUX</sub> die minimale Auflösung 1,5 ns beträgt. Die Verzögerungszeit der konfigurierbaren Verzögerungsstrecke ist stark temperaturabhängig. Dies kommt in der Konfiguration "Temperatursensor" zum Tragen.

#### 3) Konfigurationsmöglichkeiten des SPC

Im Konfigurationsmodus der OnChip Temperaturmessung werden die Taktverzögerungen der konfigurierbaren Verzögerungsstrecke sowie einer der spannungsgesteuerten Verzögerungsstrecken miteinander verglichen. Genutzt wird hier zum Einen die geringe Temperaturabhängigkeit der VDLL bei Steuerspannung  $V_{\rm CONTROL} = V_{\rm DD}$  (siehe Simulationsergebnis Abbildung 11). Zum Anderen wird zur Differenzmessung die stark temperaturabhängige Pulsverzögerung der ADLL herangezogen. Der resultierende Ausgangspuls des SPC ist somit temperaturabhängig. Das Ergebnis der Differenzbildung ist unabhängig von der Wahl der VDLL.

Das Gleiche gilt für die VDLL's im Modus der Sensorsignalwandlung. Auch hier wird die Differenz der Pulsdauer einer VDLL und der ADLL ermittelt. Im

Abbildung 8: Messablauf einer Messung mit dem US<sup>2</sup>C.

Gegensatz zur Temperaturmessung ist diese Differenz jedoch sensorgrößenabhängig. Am Steuerspannungseingang des SPC liegt nun die von der Sensoranpassung generierte Steuerspannung  $V_{\text{CONTROL}}$  an. Die Aufgabe der ADLL ist es, die Temperaturabhängigkeit der VDLL zu kompensieren, indem bezugnehmend auf die gemessene OnChip Temperatur eine entsprechende Konfiguration der ADLL vorgenommen und diese somit der Temperatur nachgeführt wird. Zudem kann der Zeitoffset  $t_{\text{OFFSET}}$  des Ausgangspulses durch Konfiguration den Eigenschaften des nachfolgenden TDCs angepasst werden.

Bei der differentiellen Sensorsignalwandlung spielen nun beide VDLL's eine Rolle, wohingegen die ADLL aus Energiespargründen deaktiviert wird. Die differentielle Sensorsignalauswertung wurde vor allem zur Auswertung von Widerstandsmessbrücken konzipiert. Dazu liegt eine der Steuerspannungen auf einem festen Potenzial während die zweite Steuerspannung mit der Sensorgröße variiert. Mit Hilfe einer vorangehenden OnChip Temperaturmessung wird die Temperaturabhängigkeit der resultierenden Pulsdifferenz controllerseitig kompensiert. Somit ist das Messergebnis auch im Modus der differentiellen Sensorsignalmessung temperaturunabhängig.

#### C. Die Mikrocontrollerschaltung

Die Mikrocontrollerschaltung deckt die Schnittstellen zum Hochschulchip, zum Anwender sowie zur Messtechnik ab, wobei die Kommunikation mit dem Chip die Hauptaufgabe darstellt. Neben der Konfiguration des SPC's und des TDC's gilt es, den Zählerstand dem aktuellen Modus entsprechend in den korrespondierenden Messwert zu konvertieren. Über die

Schnittstelle zum Anwender werden Einstellungen, wie zum Beispiel die Wahl des Sensoreingangs, sowie die Auswertung der Messergebnisse an einem PC ermöglicht. Der Datenaustausch mit der Messtechnik dient der Verifizierung des Systems durch einen automatisierten Messablauf, wobei die Steuerspannungen von einer Digital-zu-Analog Wandlung generiert werden. Die computerseitige Kommunikation mit der Messtechnik zur Datenerfassung wird mittels eines Phyton-Scripts automatisiert.

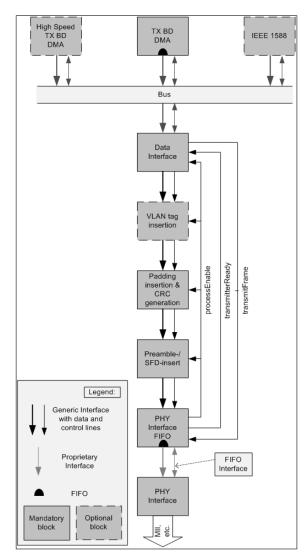

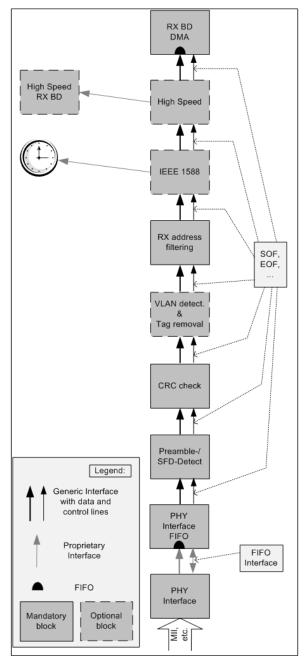

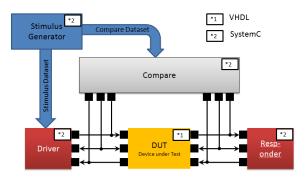

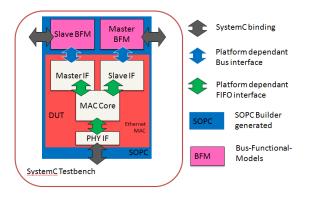

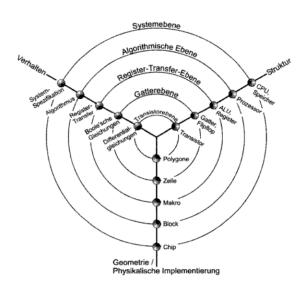

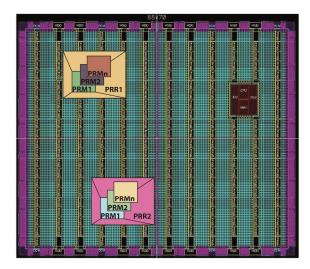

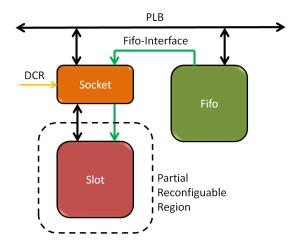

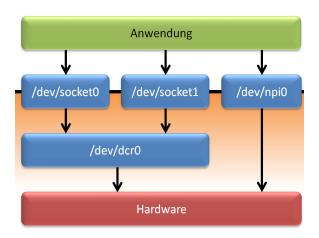

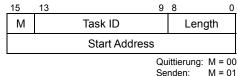

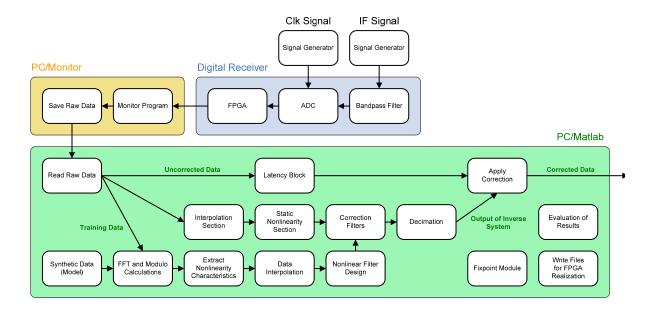

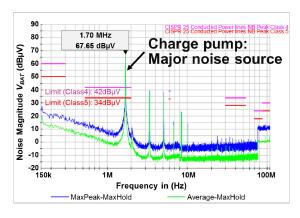

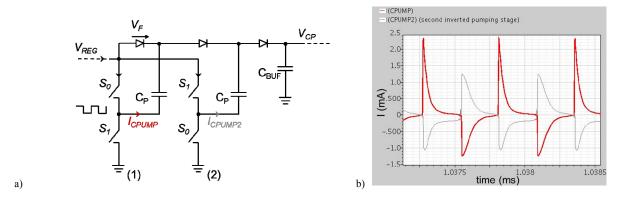

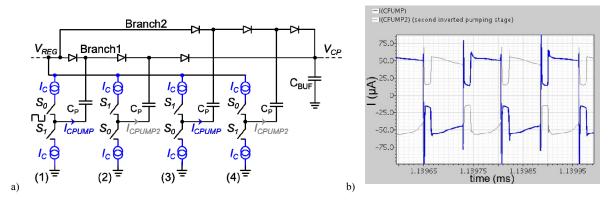

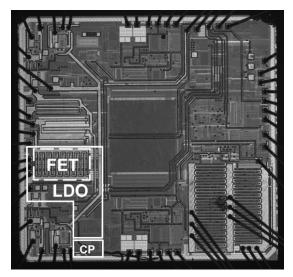

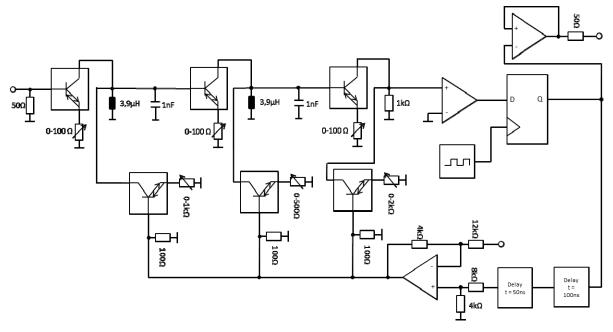

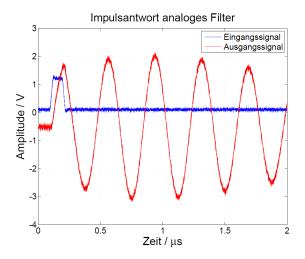

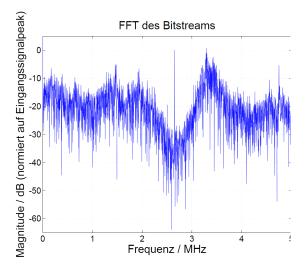

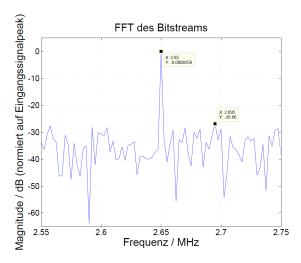

#### IV. DER MESSABLAUF