# MPC

MULTI PROJEKT CHIP GRUPPE

BADEN - WÜRTTEMBERG

**Herausgeber:** Hochschule Ulm   **Ausgabe:** 54   **ISSN** 1868-9221   **Workshop:** Ulm Juli 2015

- 1 **EUV Lithografie – optische Spitzentechnologie als Grundstein moderner Chipfertigung**

T. Heil, Carl Zeiss SMT GmbH, Oberkochen

- 9 **CMOS Image Sensors**

H. Neubauer, Fraunhofer Institut IIS, Erlangen

- 15 **Entwurf und Inbetriebnahme einer PLL in 0,35 µm CMOS-Technologie**

C. Eschenbach, B. Vettermann, J. Giehl, Hochschule Mannheim

- 23 **Ein Aufwärts-Wandler-IP im 180 nm CMOS-Prozess zur Versorgung von ASICs mittels Energy Harvesting**

M. Hiller, M. Locherer, G. Forster, Hochschule Ulm

- 35 **Flächenoptimierte Bandgap-Referenz für Low-Power-Anwendungen mit 2,5 – 5,5 V Versorgung**

I. Yasar, R. Staudt, C. L. J. Teffo, B. Schoch, T. Stoof, J. Wittmann, B. Wicht, Hochschule Reutlingen

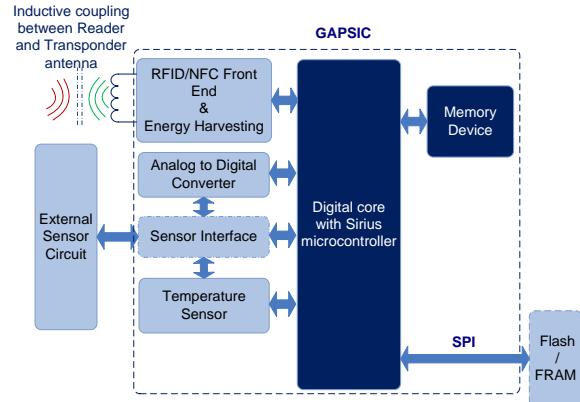

- 43 **Design and Verification of a Mixed-Signal SoC for Biomedical Applications**

M. Bhattacharyya, B. Dusch, D. Jansen, E. Mackensen, Hochschule Offenburg

- 49 **CAPABLE: A Layout Automation Framework for Analog IC Design**

D. Marolt, J. Scheible, Hochschule Reutlingen; G. Jerke, V. Marolt, Robert Bosch GmbH, Reutlingen

- 61 **Synthese eines CRC-Number-Crunchers auf einem FPGA**

S. Gebhart, I. Schoppa, Hochschule Konstanz

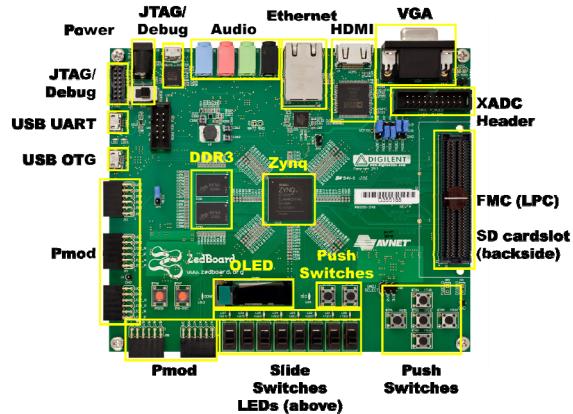

- 67 **Analyse von Hardware/Software-Varianten einer Bildverarbeitungsapplikation auf Basis eines FPGA-SoCs**

D. S. Rieber, J. Gerlach, Hochschule Albstadt-Sigmaringen

- 77 **High-Level-Synthese eines OFDM-Funkkommunikationssystems für eine auf den Einsatz in der Lehre ausgelegte Software Defined Radio-Plattform**

S. Moll, M. Welk, M. Düll, R. Münzner, Hochschule Ulm

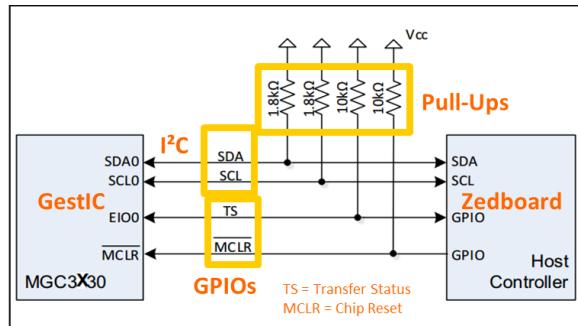

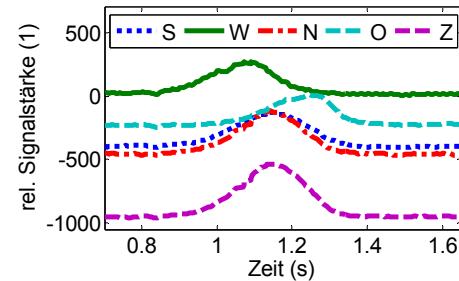

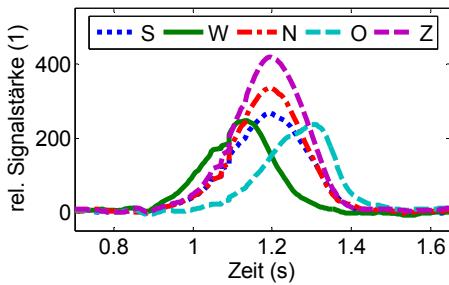

- 85 **Untersuchung maschineller Lernverfahren und Realisierung eines selbstlernenden Algorithmus zur zuverlässigeren Gestenerkennung**

D. Heese, K.-H. Blankenbach, F. Kesel, Hochschule Pforzheim

- 97 **A Web-Based Monitoring Tool for Metering Bus (EN13757-3)**

T. Matt, M. Schappacher, A. Sikora, Hochschule Offenburg

Cooperating Organisation

Solid-State Circuit Society Chapter

IEEE German Section

# Inhaltsverzeichnis

|                                                                                                  |    |

|--------------------------------------------------------------------------------------------------|----|

| <b>EUV Lithografie – optische Spitzentechnologie als Grundstein moderner Chipfertigung</b> ..... | 1  |

| T. Heil, Carl Zeiss SMT GmbH, Oberkochen                                                         |    |

| <br>                                                                                             |    |

| <b>CMOS Image Sensors</b> .....                                                                  | 9  |

| H. Neubauer, Fraunhofer Institut IIS, Erlangen                                                   |    |

| <br>                                                                                             |    |

| <b>Entwurf und Inbetriebnahme einer PLL in 0,35 µm CMOS-Technologie</b> .....                    | 15 |

| C. Eschenbach, B. Vettermann, J. Giehl, Hochschule Mannheim                                      |    |

| <br>                                                                                             |    |

| <b>Ein Aufwärts-Wandler-IP im 180 nm CMOS-Prozess zur Versorgung</b> .....                       | 23 |

| <b>von ASICs mittels Energy Harvesting</b>                                                       |    |

| M. Hiller, M. Locherer, G. Forster, Hochschule Ulm                                               |    |

| <br>                                                                                             |    |

| <b>Flächenoptimierte Bandgap-Referenz für Low-Power-Anwendungen</b> .....                        | 35 |

| <b>mit 2,5 – 5,5 V Versorgung</b>                                                                |    |

| I. Yasar, R. Staudt, C. L. J. Teffo, B. Schoch, T. Stoof, J. Wittmann,                           |    |

| B. Wicht, Hochschule Reutlingen                                                                  |    |

| <br>                                                                                             |    |

| <b>Design and Verification of a Mixed-Signal SoC for Biomedical Applications</b> .....           | 43 |

| M. Bhattacharyya, B. Dusch, D. Jansen, E. Mackensen, Hochschule Offenburg                        |    |

| <br>                                                                                             |    |

| <b>CAPABLE: A Layout Automation Framework for Analog IC Design</b> .....                         | 49 |

| D. Marolt, J. Scheible, Hochschule Reutlingen                                                    |    |

| G. Jerke, V. Marolt, Robert Bosch GmbH, Reutlingen                                               |    |

| <br>                                                                                             |    |

| <b>Synthese eines CRC-Number-Crunchers auf einem FPGA</b> .....                                  | 61 |

| S. Gebhart, I. Schoppa, Hochschule Konstanz                                                      |    |

| <br>                                                                                             |    |

| <b>Analyse von Hardware/Software-Varianten einer Bildverarbeitungsapplikation</b> .....          | 67 |

| <b>auf Basis eines FPGA-SoCs</b>                                                                 |    |

| D. S. Rieber, J. Gerlach, Hochschule Albstadt-Sigmaringen                                        |    |

| <br>                                                                                             |    |

| <b>High-Level-Synthese eines OFDM-Funkkommunikationssystems für eine</b> .....                   | 77 |

| <b>auf den Einsatz in der Lehre ausgelegte Software Defined Radio-Plattform</b>                  |    |

| S. Moll, M. Welk, M. Düll, R. Münzner, Hochschule Ulm                                            |    |

| <br>                                                                                             |    |

| <b>Untersuchung maschineller Lernverfahren und Realisierung eines selbstlernenden</b> .....      | 85 |

| <b>Algorithmus zur zuverlässigeren Gestenerkennung</b>                                           |    |

| D. Heese, K.-H. Blankenbach, F. Kesel, Hochschule Pforzheim                                      |    |

| <br>                                                                                             |    |

| <b>A Web-Based Monitoring Tool for Metering Bus (EN13757-3)</b> .....                            | 97 |

| T. Matt, M. Schappacher, A. Sikora, Hochschule Offenburg                                         |    |

**Tagungsband zum Workshop der Multiprojekt-Chip-Gruppe Baden-Württemberg**

Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie.

Die Inhalte der einzelnen Beiträge dieses Tagungsbandes liegen in der Verantwortung der jeweiligen Autoren.

Herausgeber:

Gerhard Forster, Hochschule Ulm, Prittwitzstraße 10, D-89075 Ulm

Mitherausgeber (Peer Reviewer):

Jürgen Giehl, Hochschule Mannheim, Paul-Wittsack-Straße 10, D-68163 Mannheim

Frank Kesel, Hochschule Pforzheim, Tiefenbronner Straße 65, D-75175 Pforzheim

Axel Sikora, Hochschule Offenburg, Badstraße 24, D-77652 Offenburg

Alle Rechte vorbehalten

Diesen Workshopband und alle bisherigen Bände finden Sie im Internet unter:

<http://www.mpc.belwue.de>

# EUV Lithografie – optische Spitzentechnologie als Grundstein moderner Chipfertigung

Tilmann Heil

**Zusammenfassung**—Optische Nanolithografie ist ein Schlüsselverfahren der modernen Chipfertigung, bei dem optische Systeme höchster Performance zur Strukturierung der Chips eingesetzt werden. Das „Moore’sche Gesetz“ der Halbleiterindustrie, das eine fortlaufende Miniaturisierung der Chip-Strukturen postuliert, steht dabei in direktem Zusammenhang mit Fortschritten in optischen Technologien, da die minimal erreichbare Strukturgröße auf einem Chip direkt mit dem Auflösungsvermögen der verwendeten Optik verbunden ist. Der nächste große Schritt zu noch höherer optischer Auflösung und weiterer Verkleinerung der Chipstrukturen steht mit der Einführung der Extreme Ultra Violet (EUV) Lithografie in die Chip-Volumenfertigung unmittelbar bevor. Aufgrund der kurzen Belichtungswellenlänge von 13,5 nm ermöglicht die EUV-Lithografie eine signifikante Steigerung des Auflösungsvermögens gegenüber der heute eingesetzten Immersionslithografie mit 193 nm Belichtungswellenlänge. Dieser Beitrag stellt die optischen Systeme der EUV-Lithografie vor und diskutiert die besonderen Herausforderungen und Lösungen dieser Technologie. Ein Ausblick auf zukünftige EUV-Optiken mit weiter gesteigerter Auflösung zeigt, dass die EUV-Lithografie über mehrere Technologieknoten hinweg erweiterbar ist und damit eine Fortsetzung der Halbleiter-Roadmap bis unter 9 nm Auflösung hinaus ermöglicht.

**Schlüsselwörter**—Optische Lithografie, EUV.

## I. EINLEITUNG

Bereits 1965 machte der Intel-Mitgründer Gordon Moore die Beobachtung, dass sich die Anzahl der Transistoren eines integrierten Schaltkreises auf einem Chip etwa alle 2 Jahre verdoppelt [1]. Als Treiber dieser Entwicklung identifizierte Moore die Tatsache, dass die relativen Herstellkosten pro Komponente mit der Verkleinerung der Strukturgrößen, also steigender Integrationsdichte, sinken. Dieses sogenannte „Moore’sche Gesetz“ ist seit 50 Jahren gültig, ein einmali-

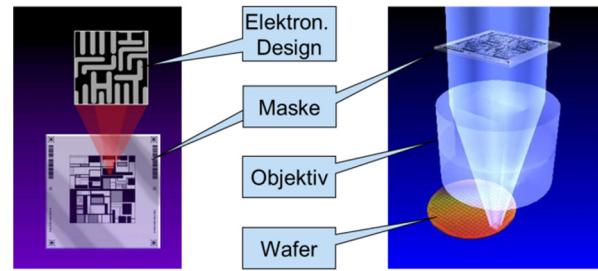

Abbildung 1: Illustration des Funktionsprinzips der optischen Lithografie.

ger Vorgang in der Industriegeschichte. Ein durch Kostenvorteile getriebener Kreislauf ermöglicht fortlaufende Innovationsschübe: neue Produktionsmaschinen ermöglichen die Verkleinerung der Chip-Strukturen, damit sinken die Kosten pro Funktioneinheit, womit auch die Preise von High-Tech-Geräten stark fallen. Dadurch erschließen sich neue und größere Märkte. Die dabei erzielten Gewinne werden wiederum in Technologie und letztlich in noch leistungsfähigere Produktionsmaschinen investiert, was den Innovationskreislauf von Neuem beginnen lässt. Es ist daher nicht verwunderlich, dass sich ein Multi-Milliarden Markt für Geräte zur Herstellung von Halbleitern entwickelt hat. Das weltweite Marktvolumen für Halbleiterkomponenten wird 2015 etwa 340 Mrd. \$ umfassen [2]. Über 30 Mrd. \$ davon gehen in die Geräte zur Herstellung der Halbleiter, wovon ein sehr großer Anteil mit knapp 7 Mrd. \$ auf die Lithografiegeräte, die sogenannten Wafer-Scanner, entfällt. Dieser hohe Anteil begründet sich durch die besondere Wertigkeit des Lithografieschritts in der hochkomplexen Herstellungskette eines Chips.

Abbildung 1 zeigt schematisch das optische Lithografie Verfahren zur Strukturierung der Chips. Das Design des zu erzeugenden elektronischen Schaltkreises wird in viele Ebenen zerlegt (typischerweise > 50). Das Bild jeder Ebene wird physisch auf eine sogenannte Maske aufgebracht. Die Maske wird durch ein optisches System im Wafer-Scanner auf den zuvor mit lichtempfindlichem Lack beschichteten Wafer abgebildet. Dieses Verfahren ermöglicht eine kontaktfreie Vervielfältigung der Maskeninformation bei höchst möglicher Produktivität. Die optische Lithografie ist daher die Methode der Wahl für die Strukturierung

aller modernen Chips. Die Schlüsselfunktion des optischen Systems in diesem Prozess ist unmittelbar einsichtig. Ein höheres Auflösungsvermögen der Optik ermöglicht kleinere Strukturen auf dem Wafer und liefert damit dem „Moore’schen Gesetz“ folgend signifikante Kostenvorteile.

Das folgende zweite Kapitel beleuchtet die zentrale Rolle der Optik für die Fortsetzung der Halbleiter näher und gibt einen Überblick über die wichtigsten optischen Innovationen der letzten Jahre bis hin zur EUV-Lithografie. Das dritte Kapitel stellt das optische System eines EUV-Wafer-Scanners vor und diskutiert die größten Herausforderungen bei der Entwicklung und Fertigung dieser Optiken. Das vierte Kapitel stellt verschiedene Optionen für neuartige EUV-optische Systeme mit nochmals deutlich gesteigerter Auflösung vor, die eine Fortsetzung der Halbleiter-Roadmap über die nächste Dekade hinaus ermöglichen sollen. Das abschließende Fazit fasst die wesentlichen Botschaften dieses Artikels zusammen.

## II. OPTIKEN FÜR DIE FORTSETZUNG DER HALBLEITER-ROADMAP

Ernst Abbe, der die wissenschaftliche Grundlage für die Produkte der Firma Carl Zeiss legte, entwickelte 1873, also fast 100 Jahre vor Gordon Moore, seine Theorie der optischen Abbildung, die auch eine Formulierung für die Auflösungsgrenze eines Objektivs beinhaltet:

$$d = \frac{\lambda}{2 n \sin \alpha}$$

$$= \frac{1}{2} \frac{\lambda}{NA}$$

Die Auflösungsgrenze formulierte er dabei mit  $d$  als den minimal noch auflösbaren Abstand zweier Linien eines Gitters, wobei  $\lambda$  die Belichtungswellenlänge,  $n$  der Brechungsindex,  $\alpha$  der halbe objektivseitige Öffnungswinkel und  $NA$  die numerische Apertur des Objektivs ist. Ernst Abbes Formulierung wird bis heute in der optischen Nanolithografie der Halbleiterindustrie in nur leicht abgewandelter Form verwendet. Die kleinste mögliche Struktur auf einem Chip, die Critical Dimension CD, ist gegeben durch

$$CD = k_1 \cdot \frac{\lambda}{NA}$$

Der Prozessparameter  $k_1$  ist dabei ein Maß für die Schwierigkeit des Herstellungsprozesses. Je kleiner  $k_1$ , desto schwieriger und teurer der Herstellungsprozess, wobei die Grenze in einem Einzelbelichtungsprozess bei  $k_1 = 0,25$  liegt. Dem „Moore’schen Gesetz“ folgend verlangt die Halbleiter-Roadmap [3] eine stetige Reduktion der CD. Offensichtlich bieten sich drei Optionen an.

Erste Option ist die Erhöhung der NA des optischen Systems. Dies ist die seitens der Chiphersteller bevor-

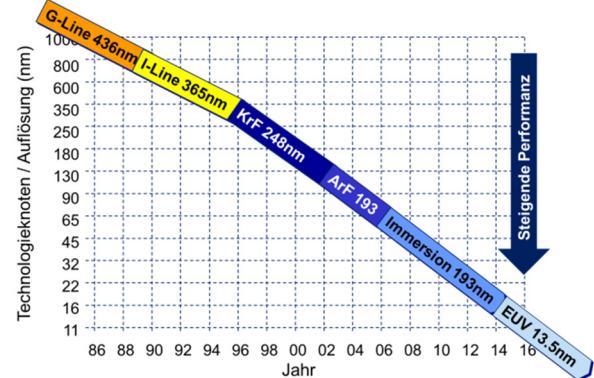

Abbildung 2: Schematische Darstellung, welche Betriebswellenlänge über welche Zeiträume und Technologieknoten in der optischen Lithografie führend eingesetzt wurde. Die zeitliche Steigerung der Auflösung innerhalb einer Betriebswellenlänge wird dabei durch eine Steigerung der NA der optischen Systeme und einer Reduktion von  $k_1$  getrieben.

zugte Option, da sowohl Prozesse als auch Technologieplattform weiter verwendet werden können. Zweite Option ist die Reduktion von  $k_1$ . Sollte eine höhere NA nicht rechtzeitig oder gar nicht mehr zur Verfügung stehen, wird der Faktor  $k_1$  gesenkt. Dies erhöht zwar die Komplexität und Kosten der Prozesse, vermeidet aber den mit einer neuen Belichtungswellenlänge verbundenen Sprung zu einer neuen Technologieplattform. Als dritte Option bleibt der Wechsel zu einer kürzeren Belichtungswellenlänge. Diese Option ist mit dem höchsten Aufwand verbunden und erfolgt typischerweise erst, wenn Optionen 1 und 2 ausgereizt sind.

Abbildung 2 zeigt, dass sich die Sequenz aus Steigerung der NA, Absenken von  $k_1$  und Sprung zu einer neuen Belichtungswellenlänge in den letzten 25 Jahren mehrfach wiederholt hat. Aktuell steht der Halbleiterindustrie erneut ein Sprung zu einer kürzeren Belichtungswellenlänge bevor. Die heute in Volumenproduktion eingesetzte Immersionstechnologie mit  $\lambda = 193$  nm soll von der EUV-Technologie mit  $\lambda = 13,5$  nm abgelöst werden. Da sich mit Wasser als Immersionsflüssigkeit die NA ökonomisch vernünftig nicht über 1,35 steigern lässt, haben die Chiphersteller in den letzten Jahren den Faktor  $k_1$  ihrer Prozesse immer weiter abgesenkt, über Mehrfachbelichtungsverfahren sogar weit unter das für Einzelbelichtungen gültige Limit von 0,25. Die damit verbundene massive Steigerung der Komplexität führte aber zu immer ungünstigeren Kostenstrukturen. Die EUV-Technologie soll nun neben einer Verbesserung der Auflösung eine Rückkehr zu Einzelbelichtungsverfahren und damit eine deutlich reduzierte Prozesskomplexität ermöglichen. Der Übergang zu EUV war ursprünglich deutlich früher geplant. In diesem Jahr verdichten sich positive Konferenzberichte von Chipherstellern über die Produktionsreife von EUV und eine erste Volumenbestellung von ASML EUV-

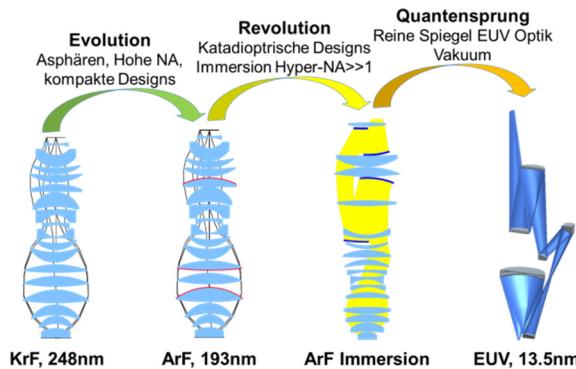

Abbildung 3: Schematische Darstellung einiger optischen Innovationen, die eine Fortsetzung der Halbleiter-Roadmap ermöglichen haben.

Scannern [4] zu einem Gesamtbild, das heute mit einer unmittelbaren Einführung von EUV in die Chip-Volumenfertigung rechnen lässt.

Die in Abbildung 2 skizzierten Innovationsschübe wurden wesentlich durch Fortschritte in optischen Technologien und den verwendeten optischen Konzepten geprägt.

Abbildung 3 zeigt einige Beispiele, wie Innovationen der Firma ZEISS bei optischen Konzepten und Technologien über den Einsatz in den ASML Wafer-Scannern neue Optionen für die Halbleiter-Roadmap eröffnet haben. Der Übergang zur 193 nm-Technologie ging einher mit einem verstärkten Einsatz von Asphären-Technologie, was kompaktere und damit ökonomisch darstellbare Designs hoher NA ermöglichte. Der Übergang zur Immersionstechnologie konnte nur durch neuartige katadioptrische Designs realisiert werden, die herkömmliche Linsenoptiken mit Spiegeloptiken kombinieren und so den Hyper-NA-Bereich bis  $NA = 1,35$  eröffnen. Der Übergang zur EUV-Technologie erfordert disruptiv neue optische Technologien, die in den folgenden Abschnitten näher erläutert werden sollen. Abbildung 3 verdeutlicht damit, wie sehr optische Systeme Schlüsselemente der modernen Nanoelektronik sind und eine Fortführung des „Moore'schen Gesetzes“ mit ermöglichen.

### III. BESONDERHEITEN UND HERAUSFORDERUNGEN EUV-OPTISCHER SYSTEME

EUV ermöglicht aufgrund seiner kurzen Betriebswellenlänge nie dagewesene Abbildungsleistungen. Allerdings führt die kurze Wellenlänge von 13,5 nm dazu, dass das optische System mehreren Randbedingungen genügen muss.

Erstens wird EUV-Licht von allen Medien so stark absorbiert, dass das gesamte System in Vakuum betrieben werden muss. Dementsprechend müssen auch alle optischen Elemente inklusive der Maske Spiegel sein.

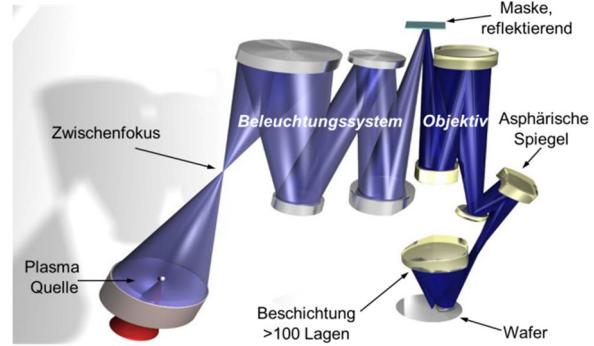

Abbildung 4: Design-Beispiel für ein EUV-optisches System. Das in den ASML Scanner NXE:3300 integrierte optische System Starlith™ 3300 weist als Kenngrößen eine Betriebswellenlänge von 13,5 nm, eine NA von 0,33, eine volle Feldgröße von 26 mm x 33 mm und eine Verkleinerung von -4 x auf.

Zweitens ist der Brechungsindex  $n$  aller Materialien bei 13,5 nm nahe 1. Die Beschichtungen der Spiegel müssen daher als Bragg-Reflektoren aus sehr vielen Lagen ausgeführt werden.

Drittens begrenzt die Absorption der zur Beschichtung der Spiegel eingesetzten Materialien die maximal mögliche Reflektion von EUV-Spiegeln auf etwa 70 %. Um also eine möglichst hohe Transmission des EUV-optischen Systems erreichen zu können, muss die Anzahl der eingesetzten Spiegel minimiert werden. Dies ist am effektivsten durch den Einsatz von asphärischen Oberflächen möglich, was allerdings höchste Ansprüche an die Fertigungstechnologien stellt.

Viertens ist die Lichtemission der Plasmaquelle sehr breitbandig. Dies hat zur Folge, dass die Selektion der Betriebswellenlänge des Scanners erst durch die Schichten der Spiegel des Beleuchtungssystems erfolgt. Insbesondere die ersten Spiegel werden daher thermisch sehr stark belastet.

In Summe führen diese Randbedingungen der EUV-Lithografie zu einem völlig neuartigen optischen System, das in Abbildung 4 skizziert ist. Das von einer Plasmaquelle erzeugte EUV-Licht wird durch einen Kollektor auf einen Zwischenfokus gebündelt. Dieser Zwischenfokus definiert den Eingang in das optische System. Dort formt das Beleuchtungssystem das Licht so, dass die in Reflektion betriebene Maske homogen und aus wohldefinierten Winkeln beleuchtet wird. Die Maske erzeugt durch die auf ihr befindlichen Strukturen ein komplexes Muster an Beugungsordnungen. Die Projektionsoptik „fängt“ dieses Beugungsmuster auf und bildet so die Maske auf den Wafer ab.

#### A. Herausforderungen bei der Fertigung von EUV-optischen Systemen

Die große Herausforderung bei der Fertigung von EUV-Systemen liegt darin, einzelne an sich bereits höchst anspruchsvolle Teile und Verfahren zu einem funktionierenden Ganzen zu integrieren. Zudem lassen

sich einige Kernpunkte identifizieren, die im Folgenden besprochen werden.

### 1) Die Oberflächen der Spiegel

EUV-Spiegel erfordern eine sehr genaue Kontrolle der Oberfläche über mehrere Größenordnungen an Raumfrequenzen. Die Messtechnik ist hier von zentraler Bedeutung. Alle Raumfrequenzbereiche müssen mit höchster Präzision vermessen werden, um eine zielführende Fertigung zu ermöglichen und die Abbildungsleistung des Systems sicher zu stellen.

Langwellige Fehler führen zu Aberrationen der Abbildung. Dies würde zu nicht formtreuer Abbildung der Maskenstrukturen auf den Wafer (CD Uniformity) und zu einer Verschiebung der Strukturen auf dem Wafer (Overlay) führen. Um funktionierende elektronische Schaltkreise erzeugen zu können, sind hier sehr enge Toleranzen vorgegeben, die sich in extreme Anforderungen an die optischen Oberflächen übersetzen. Fehler im mittleren Frequenzbereich führen zu Streulicht, das aber den Wafer noch erreicht. Da dieses Licht nicht zur Abbildung beiträgt, führt dies zu Kontrastverlust und entsprechend schlechterer Kontrolle der Strukturen auf dem Wafer. Dieser Effekt skaliert mit dem Inversen des Quadrats der Betriebswellenlänge. Verglichen mit den Spiegeln in Immersionssystemen ist für EUV-Spiegel diese Anforderung also mehr als 100 mal schärfer. Sehr kurzwellige Fehler der Spiegeloberfläche führen zu Streulicht, das nicht mehr auf dem Wafer landet. Auch diese unerwünschten Lichtverluste sind zu vermeiden.

Das folgende Beispiel soll die extremen Anforderungen an die Oberflächen der EUV-Spiegel verdeutlichen. Die Passen der Spiegeloberflächen des Starlith™ 3300 werden so genau gefertigt, dass die Abweichungen von der Idealform  $\sim 75$  pm Root Mean Square nicht überschreiten. Würde man einen solchen EUV-Spiegel auf die Größe Deutschlands skalieren und die Abweichungen als Berge ansehen, so wäre der höchste Berg im Bundesgebiet niedriger als 0,2 mm.

### 2) Die Beschichtung

EUV-Spiegel werden mit hochgenauen Nano-Multilagen beschichtet. Typischerweise werden dabei mehr als 50 Doppellagen, jeweils bestehend aus Mo und Si, auf den Spiegel aufgebracht. Dabei ist eine sehr genaue Kontrolle der Schichtdicken im Sub-Nanometer-Bereich erforderlich, zum einen, um die Zentralwellenlänge aller Schichten des optischen Systems aufeinander abzustimmen, zum anderen, um dem theoretischen Maximum der Reflektivität möglichst nahe zu kommen. Zudem müssen die Schichten sehr hohen Thermallasten standhalten.

### 3) Mechatronik und Positionierung der Spiegel

EUV-optische Systeme verlangen eine nahezu perfekte Ausrichtung aller Spiegel, da sich der Kipp eines

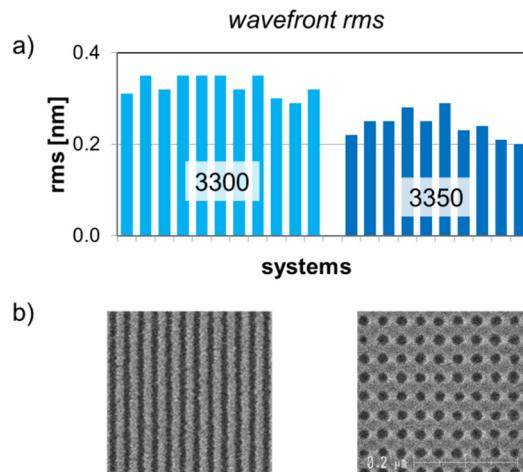

Abbildung 5: a) Wellenfront RMS der bisher gefertigten ZEISS Starlith™ 3300 Serie. Jeder Balken stellt die Wellenfront Performance eines Systems dar. b) Beispiele von Wafer-Strukturen, gefertigt mit einer ASML NXE:3300. Links: Liniensystem mit 13,5 nm half-pitch-Auflösung, Dosis 31,5 mJ/cm². Rechts: Kontaktlöcher mit 18 nm half-pitch-Auflösung, Dosis ~49 mJ/cm².

Spiegels aus Idealposition unmittelbar in einen Bildversatz auf dem Wafer übersetzen würde, was gleichbedeutend mit einer Verschiebung der Strukturen des Schaltkreises wäre. Die Overlay-Spezifikation setzt hier sehr enge Grenzen. Typische Werte für das Gesamtsystem liegen in der Größenordnung von  $\sim 1$  nm. Bei einer optischen Weglänge in der Größenordnung von  $\sim 1$  m ergibt sich damit, dass die Spiegel im Sub-Nano-Rad-Bereich positioniert und während des gesamten Belichtungsvorgangs gehalten werden müssen. Um dies sicher zu stellen, sind aufwändige mechatronische Systeme Teil der EUV-optischen Systeme.

### 4) Systemmesstechnik

Für die Qualifikation von EUV-optischen Systemen ist die Entwicklung speziell abgestimmter Messmaschinen erforderlich. Eine Qualifikation mit sichtbarem Licht ermöglicht es, die Position und Form der Oberflächen im System sicher zu stellen. Um jedoch auch energetische Effekte und Effekte innerhalb der Beschichtungen qualifizieren zu können, ist die Verwendung einer aktinischen Messtechnik notwendig. Dies erfordert den Aufbau einer entsprechenden EUV-tauglichen Interferometrie, was zum Beispiel große Vakuumkammern beinhaltet.

Abbildung 5a) zeigt die Ergebnisse der Wellenfrontmessungen der bisher gefertigten ZEISS Starlith™ 3300 Serie. Es handelt sich um EUV-Projektionsoptiken mit  $NA = 0,33$ , die in den EUV-Scanner NXE:3300 von ASML integriert werden. Abbildung 5 demonstriert eine sehr gute und konsistente Performance der Wellenfront über die gesamte bisher gefertigte Population. Diese gute Performance des

Tabelle 1: Auflösung eines EUV-Projektionsobjektivs in Abhängigkeit von der NA.

| NA                                           | 0.25 | ... | 0.33 | ... | 0.5 | ... | 0.6 |

|----------------------------------------------|------|-----|------|-----|-----|-----|-----|

| Auflösung @ $k1=0.3$<br>Einzelbelichtung/ nm | 16.2 | ... | 12.3 | ... | 8.1 | ... | 6.8 |

optischen Systems übersetzt sich in bislang unerreichte Abbildungsleistungen auf dem Wafer. Abbildung 5b) zeigt einige Beispiele von Wafern, die mit dem ASML EUV Wafer-Scanner NXE:3300 belichtet wurden [6]. Strukturen von bis zu 13 nm Auflösung in Einzelschussbelichtung verdeutlichen das enorme Potential der EUV-Technologie.

#### IV. HOCH-APERTURIGE EUV-OPTIKEN ZUR FORTSETZUNG VON “MOORE’S LAW”

Der Übergang zur EUV-Technologie ermöglicht der Halbleiterindustrie die Rückkehr zur „NA-Roadmap“. Kleinere Strukturen auf dem Chip lassen sich durch eine Steigerung der NA des optischen Systems erzielen. Tabelle 1 zeigt dieses Potential auf. Eine Steigerung der NA eines EUV-Systems auf  $\sim 0,5$  eröffnet den Bereich von 8 nm Auflösung für Einzelschussbelichtungen.

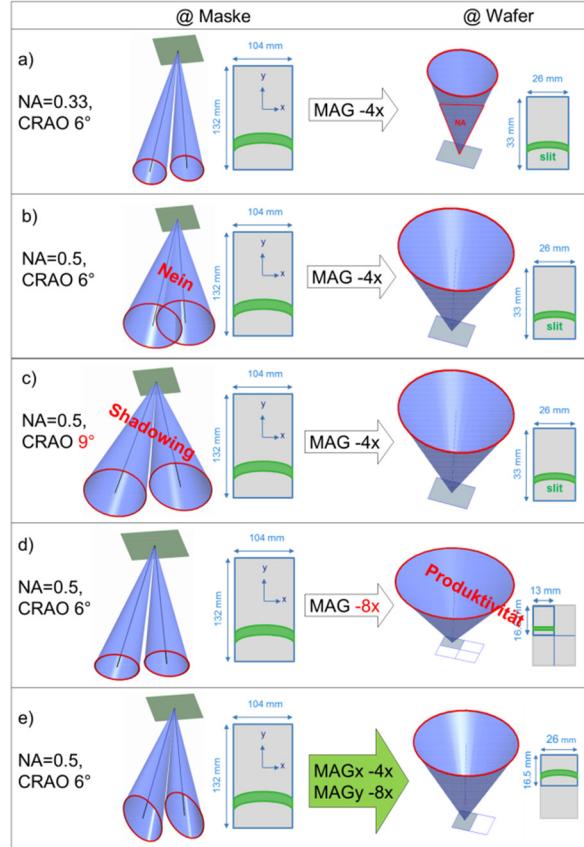

Dieser Abschnitt diskutiert, welchen Randbedingungen eine solche hoch-aperturige EUV-Optik unterliegt und wie mögliche Lösungen aussehen könnten. Die erste Randbedingung ist die NA selbst. Höhere NA ermöglicht Abbildungen mit größerem Öffnungswinkel. Dies bedeutet größere Winkel und Winkelvariation auf den Oberflächen des optischen Systems. Dabei spielt die EUV-Maske eine besondere Rolle. Abbildung 6a) illustriert die Situation an Maske und Wafer, wie es in der NA-0.33-Optik des NXE:3300 Scanners umgesetzt ist. Über jedem Punkt der Maske ist ein vom Beleuchtungssystem eingehender Lichtkegel definiert. Der Öffnungswinkel dieses Lichtkegels entspricht der beleuchtungsseitigen numerischen Apertur  $NA_{Maske}$ . Der zur Trennung der ein- und ausgehenden Lichtkegel notwendige Winkel zwischen Maskennormale und dem Hauptstrahl der Lichtkegel wird als „Chief Ray Angle at Object“ (CRAO) bezeichnet. In der NXE:3300 beträgt er CRAO =  $6^\circ$ . Der Lichtkegel wird von der Maske reflektiert und tritt in das Projektionsobjektiv ein. Das Objektiv hat eine Vergrößerung von  $-4x$ . Das heißt, dass das 104 mm x 132 mm große Feld der Maske mit einer vierfachen Verkleinerung auf 26 mm x 33 mm auf den Wafer abgebildet wird. Die Konstanz des Lichtleitwerts eines abbildenden Systems hat zur Folge, dass sich dabei die numerische Apertur entsprechend der Verkleinerung vervierfacht. Einer  $NA = 0,33$  auf Wafer-Ebene entspricht also eine  $NA_{Maske} = 0,0825$  auf Maskenebene.

Abbildung 6b) zeigt, dass die oben skizzierte Konfiguration für höhere NA nicht übernommen werden

Abbildung 6: Schematische Darstellung verschiedener Optionen zur Realisierung einer hoch-aperturigen EUV-Optik im Vergleich zu der realisierten NA-0.33-Konfiguration.

kann.  $NA = 0,5$  führt bei einem  $-4x$  Objektiv zu einer entsprechenden Vergrößerung von  $NA_{Maske}$  auf 0,125. Der halbe Öffnungswinkel des auf der Maske ein- und ausgehenden Lichtkegels übersteigt den CRAO =  $6^\circ$ . Die Lichtkegel schneiden sich. Ein abschattungsfreies System ist so nicht möglich.

Abbildung 6c) zeigt die naheliegende Option, die durch die hohe NA weit geöffneten Lichtkegel durch eine Erhöhung des CRAO auf  $9^\circ$  wieder zu trennen. Leider ist dies nicht möglich. Abschattungseffekte der Strukturen auf der Maske, das sogenannte „Shadowing“, verhindern dies: da die Maske aus Multi-Lagen besteht, auf denen Absorberstrukturen aufgebracht sind, erfolgt die Reflektion bildlich gesprochen aus den Multi-Lagen heraus. Die durch die Absorber entstehende Abschattung wird damit abhängig vom Einfallswinkel. Je steiler der Winkel, desto stärker die Abschattung. In Richtung des Scans ist der Lichtkegel symmetrisch um  $0^\circ$  verteilt, was die Winkel auf  $\pm 7,2^\circ = \arcsin(0,5/4)$  limitiert, so dass die Abschattungseffekte auch bei der höheren NA noch unproblematisch sind. Senkrecht dazu wäre der Lichtkegel um  $9^\circ$  verteilt, was einem Winkelbereich von  $1,8^\circ$  bis  $16,2^\circ$  entspricht. Es entstehen Asymmetrien in der Intensität der bildgebenden Beugungsordnungen, die

den Kontrast des Bildes auf dem Wafer reduzieren. In der in Abbildung 6c) gezeigten Konfiguration ist dieser Kontrastverlust so stark, dass die Bildqualität auf dem Wafer unzureichend ist. Da es sich hierbei um einen fundamentalen Effekt handelt, bleibt als Ausweg nur,  $NA_{Maske}$  zu reduzieren. Dies lässt sich im optischen System beispielsweise durch eine stärkere Verkleinerung der Abbildung erreichen.

Abbildung 6d) zeigt die Konfiguration eines NA 0.5 Objektivs mit einer Vergrößerung von -8x. Der CRAO kann bei  $6^\circ$  gehalten werden. Die Öffnung der Lichtkegel ist klein, so dass die Abschattungseffekte unproblematisch sind. Allerdings führt die Vergrößerung von -8x dazu, dass sich das Feld auf dem Wafer auf ein Viertel, d. h. auf 13 mm x 16,5 mm verkleinert. Die resultierenden Einbrüche in der Produktivität des Scanners sind so groß, dass auch diese Konfiguration nicht attraktiv ist. Die denkbare Alternative, bei einer Vergrößerung des Objektivs von -8x die Maskengröße zu vervierfachen, um die Chipgröße auf dem Wafer zu halten, ist aufgrund der notwendigen völlig neuen Maskeninfrastruktur ebenfalls unattraktiv.

Abbildung 6e) zeigt den Ausweg aus diesem Dilemma. Ein anamorphotisches Design mit richtungsabhängiger Vergrößerung ermöglicht es durch eine Vergrößerung von -8x in Faltungsrichtung das Shadowing zu kontrollieren und durch eine Vergrößerung von -4x senkrecht dazu die Feldbreite auf 26mm zu belassen. Ergebnis auf Wafer-Ebene ist ein Halbfeld von 26 mm x 16,5 mm Größe. Nur diese Konfiguration ermöglicht sowohl eine Abbildung mit maximaler NA und Auflösung als auch eine befriedigende Produktivität. Diese für die Lithografie neuartige optische Lösung wird in [6] näher beschrieben.

Die mit der hohen NA inhärent verbundene hohe Winkelbelastung führt aber nicht nur auf der Maske zu Schwierigkeiten. Auch innerhalb des Objektivs treten auf den Spiegeln hohe Winkel und hohe Winkelbereiche auf. Eine reine Skalierung des NA-0.33-Systems auf ein NA-0.5-System würde die Akzeptanzbereiche vorhandener Schichtsysteme auf den Spiegeln deutlich überschreiten und zu nicht akzeptablen Transmissionsverlusten führen. Ein Treiber für die hohe Winkelbelastung in Spiegelsystemen ist die Notwendigkeit, den Lichtkegel um die Spiegel herum zu führen. Der Lichtkegel muss also von der optischen Achse weg gekippt werden. Diese Kippwinkel führen zu zusätzlicher Winkelbelastung auf den Oberflächen. Die Lösung für dieses Problem besteht darin, den Lichtkegel nicht an den Spiegeln vorbei, sondern durch die Spiegel hindurch zu führen. Dazu müssen Löcher in die Spiegel gebohrt werden, was zu einer teilweisen Abschattung, einer sogenannten Obskuration, führt. Eine zentrale Obskuration in der Pupille des Objektivs kann bezüglich der Abbildungsperformanz toleriert werden, wenn sie eine Größe von etwa 20 % Radius nicht überschreitet. Durch diese Maßnahme lässt sich die Winkelbelastung der Spiegel trotz der signifikant höheren NA so weit minimieren, dass die Transmissi-

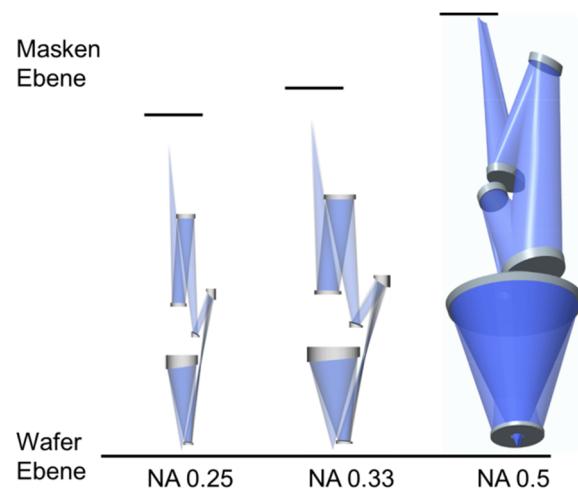

Abbildung 7: Design-Beispiele für EUV-Projektionsobjektive für NA 0.25, NA 0.33 und NA 0.5.

on des NA-0.5-Systems die des NA-0.33-Systems sogar übersteigt. Dies wird eine entsprechend höhere Produktivität des NA-0.5-Scanners ermöglichen.

Abbildung 7 zeigt Design-Beispiele für optische Systeme mit NA 0.25, NA 0.33 und NA 0.5. Während das NA-0.33-System sich noch als eine Skalierung des NA-0.25-Systems darstellen lässt, weist das NA 0.5 deutliche Änderungen auf. Auffallend ist die starke Zunahme der Größe. Auch die zentrale Obskuration der letzten Spiegel ist deutlich sichtbar. Eine weitere Besonderheit ist der sehr große letzte Spiegel. Die Größe dieses Spiegels wird direkt durch die NA des optischen Systems getrieben: die direkt mit der NA verbundenen Öffnungswinkel der auf den Wafer auftreffenden Lichtkegel bestimmen über den Abstand zwischen Spiegel und Wafer direkt die minimale Größe des Spiegels. Auch diese größer werdenden optischen Oberflächen müssen deutlich engere Spezifikationen bei weiter steigender Asphärität erfüllen, weil mit den zukünftigen Technologieknoten auch die Anforderungen an Abbildungsleistung, Kontrast und Streulicht relativ zu der NA-0.33-Optik steigen.

In Summe stellt das optische System NA 0.5 große Herausforderungen für die Optik-Herstellung und -Technologie dar. Andererseits zeigen sich keine fundamentalen Limits. Daher kann man davon ausgehen, dass hoch-aperturige EUV-Lithografie-Systeme die Fortführung der Halbleiter-Roadmap über die nächste Dekade hinaus ermöglichen werden.

## V. FAZIT

EUV-Lithografie ist die Strukturierungstechnologie zukünftiger Chip-Generationen und ermöglicht eine Fortsetzung der Halbleiter-Roadmap bis unter 9 nm Auflösung hinaus. Innovationen und Fortschritte der optischen Systeme sind hierbei von entscheidender Bedeutung. Die Industrialisierung der EUV-

Technologie zeigt mittlerweile große Fortschritte. Die ersten Scanner NXE:3300 von ASML mit integrierter ZEISS EUV-Optik sind bei den führenden Chipherstellern im Einsatz, und eine große Volumenbestellung für weitere EUV-Scanner ist erfolgt.

#### DANKSAGUNG

Der Autor dankt dem Bundesministerium für Bildung und Forschung für Förderung in den Projekten 13N8088, 13N8837, 13N9112 und 13N10567 im Rahmen der MEDEA+/CATRENE-Programme sowie den EUV-Teams bei ZEISS, ASML und unseren Partnern. Insbesondere danke ich Bernhard Kneer, Martin Lowisch und Sascha Migura für Bildmaterial und wertvolle Diskussionen.

#### LITERATURVERZEICHNIS

- [1] G.E. Moore, "Cramming more components on electronic circuits", *Electronics Volume 38, No 8*, 1965.

- [2] Gartner Dataquest (April 2015).

- [3] International Technology Roadmap for Semiconductors, 2013 Edition, [www.itrs.net](http://www.itrs.net).

- [4] ASML Press Release, "ASML reaches agreement for delivery of minimum of 15 EUV lithography systems", April 2015, [www.asml.com](http://www.asml.com).

- [5] A. Pirati et al., "Performance overview and outlook of EUV lithography systems", *Proc. SPIE 9422, Extreme Ultraviolet (EUV) Lithography VI, 94221P* (13 March 2015).

- [6] B. Kneer et al., "EUV lithography optics for sub-9nm resolution", *Proc. SPIE 9422, Extreme Ultraviolet (EUV) Lithography VI, 94221G* (16 March 2015).

Dr. Tilmann Heil ist Director Lead System Engineering bei der Carl Zeiss SMT GmbH. Er studierte Physik an der TU Darmstadt und der KTH Stockholm und promovierte 2001 an der TU Darmstadt. Nach einem Post Doc bei ATR Kyoto begann er als Wissenschaftlicher Mitarbeiter bei der Carl Zeiss SMT GmbH und arbeitet seither in System Engineering, Technischem Marketing, Forschungsförderung und Konzeptentwicklung.

# CMOS Image Sensors

Harald Neubauer

**Abstract**—CMOS Image Sensors (CIS) are used in a lot of (mobile) devices. An overview of current CMOS technology enhancements for image sensors is summarized and challenges for the ASIC implementations are described. Methods to optimize the design of analog to digital converters (ADC) are shown.

**Index Terms**—CMOS Image Sensors, ASIC design, ADC.

## I. INTRODUCTION

CMOS Image Sensors (CIS) are used in many applications, mainly in mobile devices (see fig. 1). CMOS image sensors are dominating the market for imaging devices, where the former used CCD sensors have about 6.5 % remaining market share. The change of the last 10 years from CCD towards CIS devices is mostly driven by cost and features:

- Signal processing on the same device

- Similar image quality compared to CCD

- Higher speed

- Lower cost

- Advantages from general technology scaling

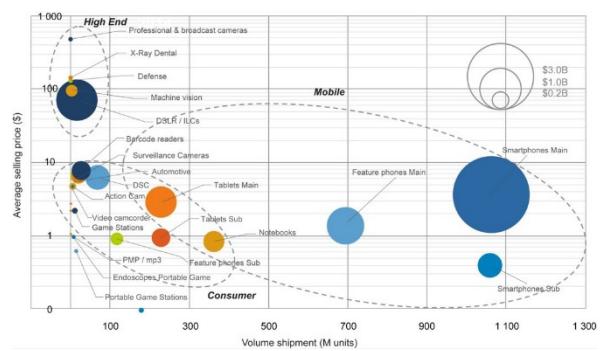

Imagers for mobile devices are driven by a race for more pixels. More pixels lead to smaller pixels due to optical boundary conditions (mostly the height of the lens stack). Currently pixels around 1  $\mu\text{m}$  pitch are used for mobile devices. The market segmentation of CIS devices in 2014 is depicted in fig. 2. In total 3.8 B devices were built in 2014 with a revenue of 10.2 B \$. The annual growth rate is around 10 %.

## II. ARCHITECTURE OF CMOS IMAGE SENSORS

An image sensor usually is built of a pixel array and readout electronics. The pixels are connected by row and column lines. The row connections are used to select one row, where each of the pixels is connected in the selected row to the column line, as shown in fig. 3. The readout is done by reading the sensor out row by row. The information of the pixels is processed with the readout circuitry. This usually has a circuit for noise reduction through correlated double sam-

Figure 1: Number of CIS devices for different applications [1].

Figure 2: Number and average selling price of CIS devices for different applications [2].

pling. Often the value is already digitized on the sensor with an analog to digital converter.

### A. Rolling and Global Shutter

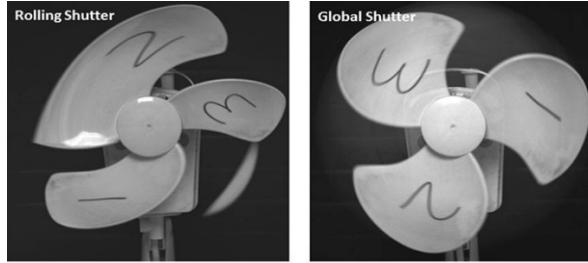

Usually, imagers are read out in a rolling shutter configuration. That means that the pixel is reset after it was read out. By this the maximum exposure can be reached and this readout scheme is very simple. As a drawback this creates unwanted image artifacts with moving objects. A rotating fan is often used as a target to show the effect (fig. 4).

Figure 3: Architecture of a CMOS image sensor.

Figure 4: Moving fan imaged with rolling shutter [4].

Figure 5: Rolling readout [5].

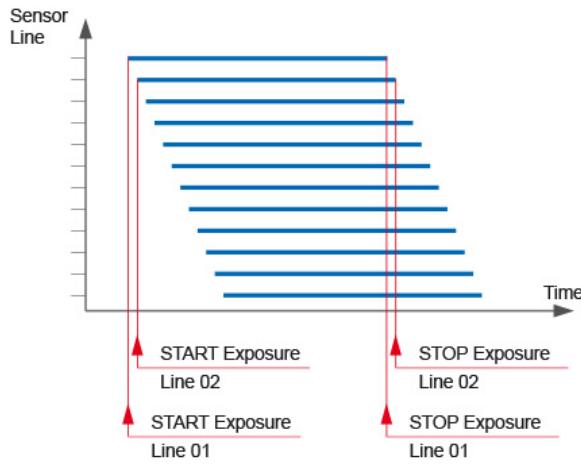

Although all rows have the same exposure length, the start and end of the exposure is shifted from one row to the next by the readout speed. The fan moves while the image is read out. This is further shown in fig. 5.

To circumvent these artifacts, the exposure interval needs to be the same for all pixels. The exposure start and stop become global signals, so every pixel is exposed in the same interval. During this exposure the previous acquired value is read out of an additional memory in a sequential manner (fig. 5).

Figure 6: Basic 3 transistor pixel [3].

Figure 7: ‘Pinned’ 4 transistor pixel [3].

## B. Pixel Circuits

In image sensors different pixel electronics are used. The pixels are usually named according to the average number of transistors per pixel.

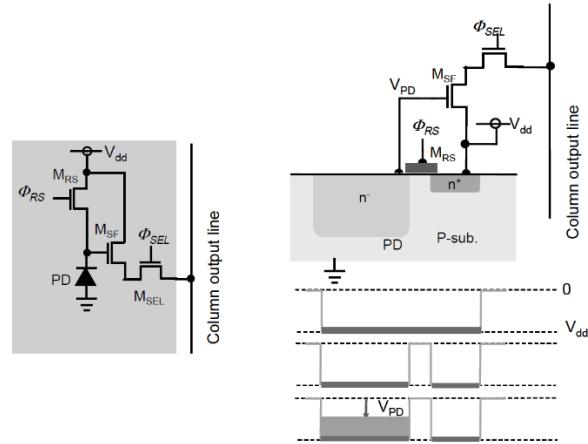

### 1) 3T Pixel

The basic cell is shown in fig. 6. It contains 3 transistors per pixel (reset, source follower, select). For the exposure, first the pixel is reset, so that the photodiode (usually an n diffusion in the p substrate) is charged to a positive voltage. To compensate for the threshold voltage of the reset transistor, either the supply voltage of the pixel is lowered, or the reset voltage is around one threshold voltage above the pixel supply voltage. After the reset the incoming light discharges the photodiode to a lower voltage. When the pixel is read out the row select signal connects the source-follower to the column line. The first element at the end of the column line is a current sink.

Figure 8: 5T Global shutter pixel [3].

Figure 9: 1.75T (shared) pixel [3].

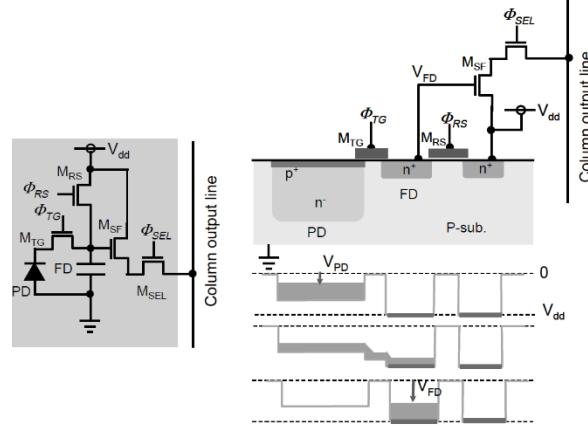

## 2) 4T (pinned) Pixel

In order to increase pixel performance a modification of this pixel is commonly used as shown in fig. 7. The modified pixel enables reduction of noise and dark current. The pixel separates the photodiode from the readout node. By this a conversion gain between these two nodes can be enabled. Several process steps need to be added to a conventional process, so these pixels cannot be used in standard processes. The operation is different from the described 3T-pixel.

The readout node called floating diffusion (FD) is reset through the reset transistor. The value of this reset is sampled in the readout circuit at the column line. Then the transfer of the charge is done by switching the transfer transistor to the ON state. The charge is fully transferred out of the photodiode to the floating diffusion. Also this value is acquired by the readout circuit. The difference of these two readings is generated which eliminates the reset noise and the source follower offset. As the capacity of the floating diffusion can be chosen smaller than the capacity of the photodiode, a conversion gain can be established. The voltage change on the floating diffusion is higher than on the photodiode.

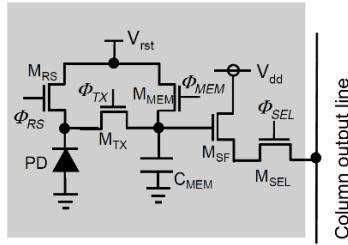

## 3) 5T (global shutter) Pixel

To enable global shutter, for some applications (mainly in machine vision) a storage node and a global reset is introduced in the pixel (fig. 8). The pixel in fig. 8 is based on the basic pixel of fig. 6 with the addition of a global reset for the photodiode and a pixel storage ( $C_{MEM}$ ). All pixels are reset at the same time and integration of light is stopped by transferring the information to the capacitor at the same time. As 2 additional transistors are needed, this pixel is usually only used if features are extracted for quality control, or fast moving objects are recorded. Some global shutter pixels work similarly to the 4T (pinned) pixels with full charge transfer, although further additional process steps are needed.

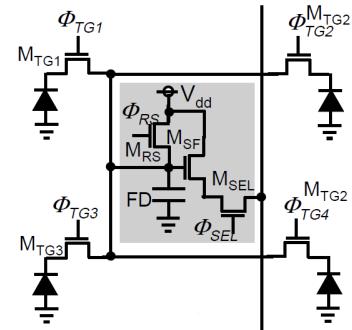

## 4) 1.75T (shared) Pixel

For small pixels ( $< 3 \mu\text{m}$ ) the readout transistors are shared between different pixels to reduce the area

consumption (fig. 9). Configurations of 2 or 4 pixels are common. Only half of the column lines are needed and they have twice the pixel pitch, which reduces the area consumption for the readout electronics.

### C. Readout Circuits

Column readout circuits process the pixel information and feed them off the sensor. This can be a simple multiplexer or an analog to digital converter (ADC) with a chain of image processing algorithms. There are several possibilities for the implementation of the ADC.

- Sensor ADC. The column signals are multiplexed and digitized in one ADC (or only a few). This concept requires high throughput ADCs and high analog bandwidth, which results in a higher noise bandwidth.

- Pixel ADC. Only suitable for pixels, where an ADC can be fit into without losing too much photodiode area. This is usually used with pixel pitches over  $50 \mu\text{m}$ .

- Column ADC. One ADC is used per column. This is the most frequently used architecture, as it permits flexible choice of different ADC types.

For the ADC several requirements have to be met. For a column ADC this could result in the following specifications:

- Usually a sensor has a frame rate from 25 up to several hundred frames per second (fps). The speed of the ADC is the frame rate multiplied by the number of rows. For a 2 MP sensor of  $1920 \times 1080$  pixels, this gives  $1080 \cdot 25 \text{ fps} = 25 \text{ kS/s}$ .

- The ADC-resolution is often around 10 bit.

- Spacing of the ADC is around  $2 \times$  pixel pitch (if 4-shared pixels are used) or  $4 \times$  pixel pitch if the ADC are distributed to the top and bottom of the sensor. Therefore spacing in the example is  $4 \mu\text{m}$  or  $8 \mu\text{m}$ .

- Power consumption is also a challenge as in the example 540 ADCs are needed.

Several architectures for the column level ADC are suitable.

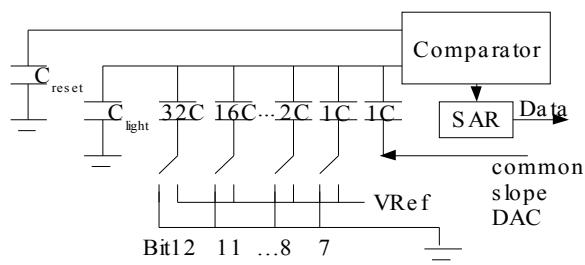

Figure 10: Hybrid SAR slope converter.

Table 1: Comparison of SAR, slope and hybrid converter.

| Type            | DAC Elements | Cycles |

|-----------------|--------------|--------|

| 12 bit SAR      | 4096         | 12     |

| 12 bit slope    | 0            | 4096   |

| 6 SAR – 6 slope | 64           | 70     |

### 1) Single Slope Ramp ADC

This is the most popular architecture as there is very little circuitry per column needed. Only a comparator and memory is needed per column. A global common ramp for all ADCs is implemented once on the sensor. However, this concept becomes challenging in mega-pixel applications where row lines increase which makes high clock rates necessary.

### 2) Successive Approximation Converter (SAR)

This type of converter is very power efficient. Unfortunately a lot of implementations require considerable area as the needed digital to analog converter is built using a capacitor or resistor array. A new type of converter can be built out of the combination of a slope and a SAR converter. The upper half of the resolution is built out of a SAR and the lower half is done using slope conversion (fig. 10). This implementation mixes the two concepts. It requires less hardware than the SAR and less clock cycles than the slope converter. A comparison is shown in table 1.

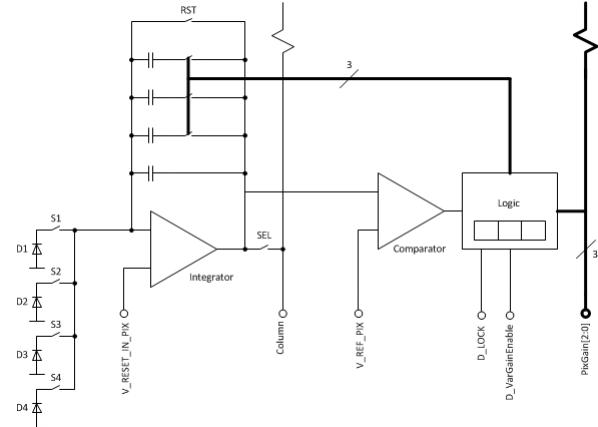

### 3) Pixel Level Preconversion

If the pixels are big enough and the application demands for high dynamic range a preconversion in the pixels can be carried out. With the preconversion the first most significant bits are already digitized in the pixel extending the dynamic range of the remaining system.

An example is a sensor working in an x-ray application with pixels of 200  $\mu\text{m}$  pitch. A schematic is shown in figure 11. The first 2 bits are digitized in the pixel and the residuum is converted at 12 bit level in the system. In the pixel an operational amplifier

Figure 11: Pixel preconversion.

Figure 12: Backside illumination [3].

charges the switchable capacitors, which are binary scaled. A comparator decides if the threshold level is reached and then a small logic block switches to the next capacitor. The digital information is read out by 2 digital lines. The residuum is transferred as usual by an analog column line to the read circuit to digitize the required resolution.

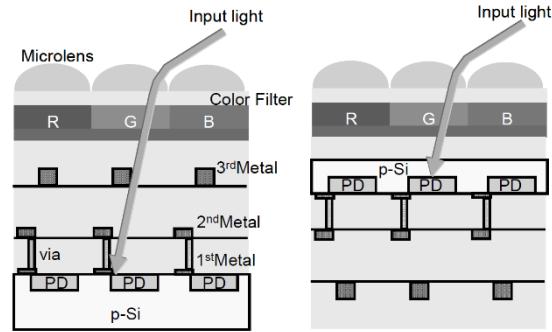

## III. TRENDS IN CMOS IMAGE SENSORS

There have been a lot of improvements from the first CMOS image sensors to current state of the art. Around 10 years ago imaging was dominated by charge coupled device imagers (CCD). These need a specific technology and usually higher voltages than CMOS. The CMOS image sensors enabled complex digital processing on the same device and used mainstream and cheap processes. To improve the CMOS performance, a lot of techniques already used in CCD were introduced to CMOS image sensors like the complete charge transfer or the backside illumination. The conception of backside illumination (BSI) is depicted in figure 12.

With BSI a much greater angle of incident light can be accepted. Further the use of more metals in the CMOS process is possible resulting in a higher density of the digital circuits. After processing the wafer is

Harald Neubauer received the Dipl.-Ing. in Electrical Engineering in 1997 from Friedrich-Alexander University Erlangen-Nürnberg. He heads the group CMOS Image Sensors at the Fraunhofer Institute for Integrated Circuits in Erlangen.

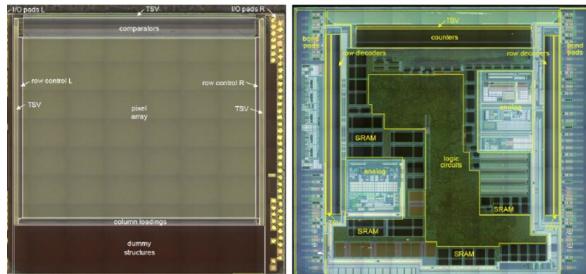

Figure 13: 3D stacked image sensor [6].

attached to a handling structure and thinned down to a few  $\mu\text{m}$ . The color filters and microlenses are put on the backside. The electrical connection is realized with through silicon vias.

Recently sensor systems were developed, which separate the acquisition of light and the processing. A sensor die with little circuitry is attached to a processing die where digitization and digital processing is done. In figure 13 the sensor is realized in a 90 nm process, while the processing wafer is manufactured in 65 nm. Together an 8 megapixel image sensor with a pixel pitch of 1.12  $\mu\text{m}$  is formed.

#### IV. SUMMARY

CMOS image sensors are mixed signal circuits which process several thousand input signals in parallel. The analog to digital conversion is a challenging task in the implementation of such systems. Several enhancements to CMOS processes have been introduced to make these processes more suitable for the implementation of image sensors. New techniques for the sensors as backside illumination and stacked systems using different processes have been recently introduced.

#### REFERENCES

- [1] Yole Developpement: [http://www.yole.fr/iso\\_album/illus\\_cisapplications\\_yole\\_oct2014.jpg](http://www.yole.fr/iso_album/illus_cisapplications_yole_oct2014.jpg)

- [2] Yole Developpement: [http://www.yole.fr/iso\\_album/illus\\_cismarket\\_landscape\\_yole\\_jan2015.jpg](http://www.yole.fr/iso_album/illus_cismarket_landscape_yole_jan2015.jpg).

- [3] Jun Ohta, „Smart CMOS Image Sensors and Applications“, CRC Press 2007 ISBN: 978-0-8493-3681-2.

- [4] Andor:<http://www.andor.com/learning-academy/rolling-and-global-shutter-exposure-flexibility>.

- [5] Basler <http://www.baslerweb.com/de/vision-campus/kamera-auswahl>.

- [6] Chipworks:<http://image-sensors-world.blogspot.de/2015/06/iftle-on-stacking-technology-progress.html>.

# Entwurf und Inbetriebnahme einer PLL in 0,35 µm CMOS-Technologie

Christian Eschenbach, Bernd Vettermann, Jürgen Giehl

**Zusammenfassung**—Die „Phase-Locked Loop“ ist ein elektronischer Regelkreis, der zur Erzeugung stabiler Frequenzen eingesetzt wird. Dieser Schaltungstyp stellt eine wichtige Komponente in frequenzabhängigen Systemen dar, die für eine korrekte Funktionsweise stabile Betriebsfrequenzen benötigen. Anhand eines Phasenvergleichs des Ausgangssignals der PLL-Schaltung gegenüber einer vorgegebenen Referenz kann durch eine Schleifenschaltung eine fortwährende Synchronisierung der Ausgangsfrequenz auf die Referenzfrequenz stattfinden. Somit wird die ausgegebene Frequenz in Abhängigkeit von der Eingangsfrequenz stabil gehalten. In dieser Arbeit wird die Entwicklung und die Inbetriebnahme einer Phasenregelschleife mit der Erweiterung durch einen Frequenzteiler in 0,35 µm CMOS-Technologie präsentiert. Die PLL ist auf eine Signalfrequenz von 80 MHz bei einer Referenzfrequenz von 10 MHz ausgelegt. Sie erlaubt eine Frequenzabstufung über 3 Bit bei einer Einschwingzeit von 3,8 µs.

**Schlüsselwörter**—PLL, Chipentwurf analog, Chipentwurf digital, Platinenentwurf.

## I. EINLEITUNG

In der integrierten Schaltungstechnik ist die Phasenregelschleife aufgrund ihrer frequenzregulierenden Funktionsweise ein Schaltungstyp, der nicht mehr wegzudenken ist. Die hauptsächlichen Anwendungsbereiche betreffen Frequenzmodulation/-demodulation, Frequenzstabilisierung von Eingangssignalen für andere Systemelemente und Frequenzsynthese [1]-[3].

In ihrer Ausführungsart gibt es unterschiedliche Varianten, was sowohl den grundlegenden Gesamtaufbau, als auch einzelne Komponenten der PLL-Schaltung betreffen. PLLs können vollständig mit analogen oder mit digitalen Schaltungskomponenten entwickelt werden, wobei auch Mischformen möglich sind. Mit digitalen Signalprozessoren besteht prinzipiell auch die Möglichkeit, eine PLL mit Hilfe von Software (z. B. VHDL) zu realisieren. Was die feinere

Christian Eschenbach, christian.eschenbach1@hs-mannheim.de, Jürgen Giehl, j.giehl@hs-mannheim.de, Bernd Vettermann, b.vettermann@hs-mannheim.de, Hochschule Mannheim, Paul-Wittsack-Str. 10, 68163 Mannheim.

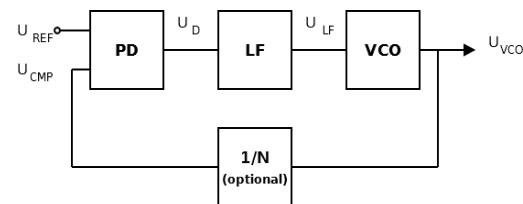

Abbildung 1: PLL-Blockschaltbild.

Struktur der Phasenregelschleife angeht, können verschiedene Varianten der Phasendetektion sowie unterschiedliche Filterstrukturen eingesetzt werden, die sich maßgeblich auf die Verhaltensweise des Phasenregelkreises auswirken.

Im Falle der Phase-Locked Loop, über die in diesem Beitrag berichtet wird, handelt es sich um eine Mischform, die aufgrund des in digitaler Logik arbeitenden Phasendetektors den „Digital PLLs“ zuzuordnen ist. Zur Phasendetektion wird ein sogenannter Phasen-Frequenz-Detektor verwendet, der gegenüber einem herkömmlichen XOR-Phasendetektor Vorteile im Zieh- sowie im Fangbereich vorweisen kann.

## II. STAND DER TECHNIK UND ANFÄNGLICHE SPEZIFIKATION

Die Funktionsweise einer Phase-Locked Loop ist relativ unkompliziert. Sie ist in ihrer Grundkonfiguration mit nur drei notwendigen Komponenten ausgestattet (Abb. 1). Das Hauptmerkmal einer PLL ist eine Rückkopplung ihres Ausgangs auf eine Art Komparator, der Phasendetektor genannt wird. In diese Vergleicherschaltung wird ein Referenzsignal mit einer bestimmten Frequenz gespeist, gegen welches das Ausgangssignal auf Phasendifferenzen verglichen wird. Es ergibt sich wiederum ein hochfrequentes Signal, das abhängig von diesen Differenzen schwingt und als Steuersignal eines spannungsgesteuerten Oszillators fungieren soll. Damit dieser einen von der Höhe seiner Eingangsspannung abhängigen PLL-Ausgangstakt generieren kann, müssen die hochfrequenten Anteile des Komparatorsignals über einen Tiefpass herausgefiltert werden, bevor der VCO (spannungsgesteuerter Oszillator, voltage-controlled oscillator) sein Steuersignal erhält. Durch die Rückkopplung des Ausgangstakts auf den Komparator für einen Phasenvergleich kann somit eine Nachregelung und gegenüber Tempe-

Tabelle 1: Spezifikation der PLL.

| Parameter                        | Symbol           | Spezifikation |

|----------------------------------|------------------|---------------|

| Versorgungsspannung              | $V_{DD}$         | 3,3 V         |

| Referenzfrequenz                 | $f_{REF}$        | 10 MHz        |

| Max. Ausgangsfrequenz            | $f_{max}$        | 80 MHz        |

| Teilerfaktor                     | $N$              | 2-8           |

| Ziehzeit                         | $T_P$            | 1 $\mu$ s     |

| Fangzeit                         | $T_L$            | 2 $\mu$ s     |

| Einschwingzeit                   | $T_P + T_L$      | 3 $\mu$ s     |

| Frequenzabweichung (1 $\sigma$ ) | $\Delta f_{CMP}$ | < 5 kHz       |

| Jitter bei 10 MHz                |                  | < 100 ps      |

ratur oder sonstigen Einflüssen zuverlässige Stabilisierung der Ausgangsfrequenz erreicht werden.

Ziel dieses Projektes war es, eine Phasenregelschaltung für zukünftige Designs bereitzustellen. Die PLL soll die Referenzfrequenz stabilisieren und weitere Frequenzen synthetisieren. Dazu wurde die PLL-Grundschaltung neben den 3 Hauptkomponenten Phasendetektor, Schleifenfilter und spannungsgesteuerter Oszillator um einen Frequenzteiler mit den Teilungsfaktoren 2 bis 8 erweitert (Abb. 1). Zur Verbesserung der Frequenzeigenschaften wurde ein Phasen-Frequenz-Detektor (PFD) verwendet.

Der PFD ermöglicht einen genaueren Phasenvergleich des Ausgangssignals  $U_{CMP}$  der Frequenzteilerstufe gegenüber dem Referenzsignal  $U_{REF}$ , indem er anstatt eines logischen „HIGH“- und „LOW“-Signals (wie es bei einem XOR-Detektor der Fall ist) ein Tristate-Signal generiert, das 3 Regulierungsrichtungen der Frequenz ermöglicht: Erhöhen, Verringern oder Halten. Dieses Tristate-Signal, in dem sich die Phasendifferenzen zwischen PLL-Ein- und Ausgang widerspiegeln, schwingt mit hoher Frequenz und muss somit über ein Tiefpassfilter gemittelt werden, damit sich eine niederfrequente Steuerspannung für den spannungsgesteuerten Oszillator ergibt. Die Höhe dieser Steuerspannung bestimmt die Ausgabefrequenz des durch den VCO generierten Taktsignals  $U_{VCO}$ . Der VCO erzeugt die Eingangsfrequenz des frequenzbestimmenden Elements der PLL-Schaltung, also des Frequenzteilers. Das in der Frequenz um den Faktor  $N$  heruntergeteilte Signal  $U_{CMP}$  wird auf den Eingang des Phasendetektors rückgekoppelt, wodurch die Schleifenwirkung der PLL entsteht.

Der angestrebte Betriebszustand einer PLL, also der „eingeklemmte Zustand“, wird dann erreicht, wenn Rückkoppelfrequenz  $f_{CMP}$  und Referenzfrequenz  $f_{REF}$  sich gleichen:

$$f_{CMP} \cong f_{REF}$$

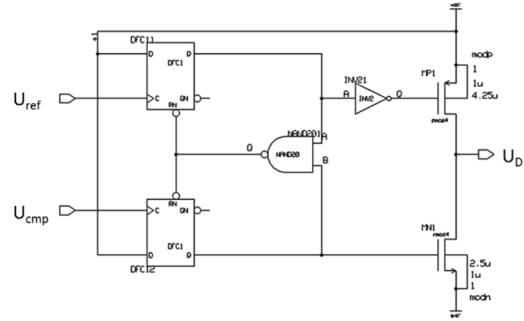

Abbildung 2: Phasen-Frequenz-Detektor.

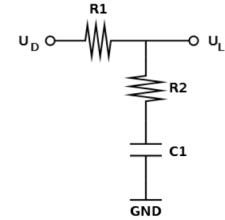

Abbildung 3: PLL-Loop-Filter.

In Kombination mit einem Frequenzteiler des Teilerfaktors  $N = 8$  ergibt sich damit die VCO-Frequenz  $f_{VCO}$  zu

$$f_{VCO} = N \cdot f_{ref}.$$

Bei einer Referenzfrequenz von 10 MHz und einem Teilerfaktor  $N = 8$  liefert der VCO eine Frequenz von 80 MHz.

### III. ENTWURF UND DIMENSIONIERUNG

Phase-Locked Loops können mit unterschiedlicher Motivation, die vor allem vom Anwendungszweck abhängig ist, dimensioniert werden. Hier wurde ein eher genereller Ansatz verfolgt, da es keine genauen Einschränkungen oder Vorgaben gab, was bspw. Aufstartgeschwindigkeit oder Rauschen der Schaltung angeht. Deswegen wurde ein Ansatz speziell im Hinblick auf eine kurze Einschwingzeit gewählt, welcher nach Vorbild einer beispielhaften Entwicklungslinie für Phasenregelschaltungen [1, S. 126-134] durchgeführt wurde. Als Ziehzeit (pull-in time) wurde  $T_P = 1 \mu$ s und als Fangzeit (lock-in time) wurde  $T_L = 2 \mu$ s festgelegt. Tabelle 1 zeigt die angestrebte Spezifikation der PLL. Als Referenz sollte ein 10 MHz-Quarzoszillator dienen, der bereits in einer früheren Arbeit [4] umgesetzt wurde. Die maximale Ausgangsfrequenz sollte 80 MHz betragen. Mit Teilerfaktoren 2-8 sollten 7 weitere Frequenzen zwischen 80 MHz und 10 MHz ermöglicht werden.

Abbildung 2 zeigt den verwendeten Phasen-Frequenz-Detektor. Die beiden D-Flip-Flops werden mit einem HIGH-Signal kontinuierlich durchgeschaltet. Abhängig von den logischen Pegeln der Eingangssignale können sich zur Übermittlung an die PMOS-

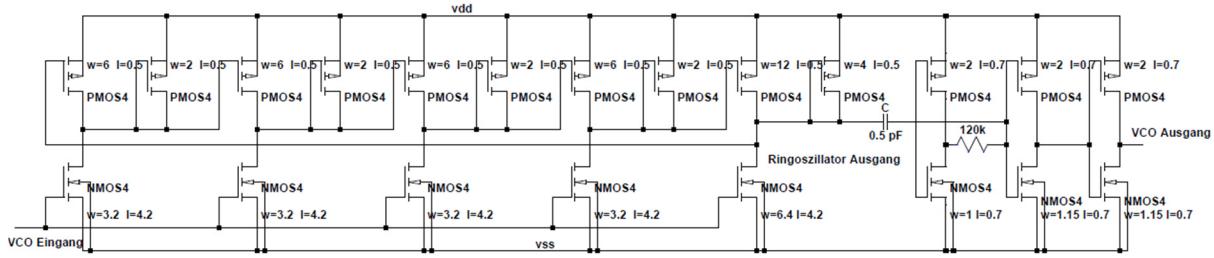

Abbildung 4: Schaltbild des VCO mit Dimensionierung (Einheit  $\mu\text{m}$ ).

und NMOS-Transistoren 3 Zustände einstellen: 1/0, 0/1 und 0/0. Der vierte Zustand 1/1 wird durch eine Aktivierung des Resets über ein NAND-Gatter unterbunden. Die Zustände bestimmen das Schaltverhalten der Transistoren. 1/0 bewirkt ein Durchschalten des PMOS-Transistors, wodurch das PFD-Ausgangssignal  $U_D$  auf  $V_{DD}$  gezogen wird. Dies hat zur Folge, dass die Frequenz der PLL erhöht wird. Mit 0/1 wird das PFD-Ausgangssignal auf GND gezogen, während 0/0 eine Sperrung beider Transistoren bewirkt. Dadurch stellt sich ein hochohmiger Zustand ein, der die Frequenznachführung unterbricht und die aktuelle Frequenz beibehält.

Abbildung 3 stellt das Loop-Filter für die Mittelung des PFD-Signals  $U_D$  dar. Es wird ein passives Tiefpassfilter verwendet. Die Dimensionierung des Filters beginnt mit der Festlegung der Dämpfungskonstante  $\zeta$ . Bei einem konstanten Skalierungsfaktor  $N$  ist es sinnvoll, diese auf einen Wert zwischen 0,5 und 1,5 [1, S. 129] festzulegen, um die Stabilität der Regelschleife zu gewährleisten. Hier wurde 0,7 gewählt. Die Übertragungscharakteristik des passiven Filters erster Ordnung wird durch die beiden Zeitkonstanten  $\tau_1 = R_1 \cdot C_1$  und  $\tau_2 = R_2 \cdot C_1$  bestimmt.  $\omega_2 = 1/\tau_2$  definiert den Punkt im Bodediagramm, bei dem die Übertragungsfunktion wieder horizontal verläuft, also eine Nullstelle [1, S. 107].

$$\tau_2 = \frac{2\zeta}{\omega_n}$$

Die Bedingung  $\omega_0 = 1/(\tau_1 + \tau_2)$  bestimmt die -3dB-Eckfrequenz der Übertragungsfunktion. Die natürliche Frequenz  $\omega_n$  bestimmt sich aus dem Verhältnis  $2\pi/T_L$ . Für  $T_L = 2 \mu\text{s}$  benötigt man somit  $\tau_2 = 446 \text{ ns}$ . Die Zeitkonstante  $\tau_1$  bestimmt sich unter Zuhilfenahme von  $\tau_2$  und den Verstärkungsfaktoren  $K_0$  des VCOs und  $K_D$  des PFDs zu:

$$\tau_1 = \frac{K_0 K_D}{N \omega_n^2} - \tau_2$$

Mit geeigneten Werten für  $K_0$  und  $K_D$  erhält man daraus  $\tau_1 = 1,23 \mu\text{s}$ . Mit einer Festlegung der Kapazität  $C_1$  auf 15 pF ergeben sich die Widerstände  $R_1 = 82 \text{ k}\Omega$  und  $R_2 = 30 \text{ k}\Omega$ .

Das tiefpassgefilterte Ausgangssignal  $U_{LF}$  steht dem spannungsgesteuerten Oszillatoren als Steuersignal zur

Verfügung. Dessen Schaltplan ist in Abbildung 4 dargestellt. Das niederfrequente Steuersignal  $U_{LF}$  kontrolliert über den VCO-Eingang den maximalen Laststrom in den Invertern des Ringoszillators und damit deren Verzögerungszeit. Die Inverter bewirken jeweils eine Phasendrehung um  $180^\circ$  der Eigenschwingung des VCO, wodurch sich mit dem Durchlauf der einzelnen Inverterstufen eine hochfrequente Schwingung  $U_{VCO}$  ergibt, deren Frequenz von der Schaltgeschwindigkeit bzw. dem Stromfluss abhängig ist. Der Ringoszillator liefert an seinem Ausgang keinen vollen logischen Pegel von 0 bis 3,3 V. Deshalb ist dessen Ausgangssignal auf einen durch 2 MOS-Dioden vorgespannten Inverter kapazitiv gekoppelt, so dass hier wiederum der volle logische Pegel erreicht wird.

Die HF-Rechteckschwingung aus dem VCO gibt den Takt des PLL-Frequenzteilers vor. Der Frequenzteiler mit einstellbarem Skalierungsfaktor  $N$  wird durch eine einfache digitale Zählerschaltung realisiert. Diese besteht aus D-Flip-Flops und bildet ein 3-Bit-Zählsystem der Zustände 000 bis 111. Bis Zustand 111 verstreichen 8 Taktzyklen, womit sich also der Teilerfaktor  $N = 8$  der PLL ergibt. Die zwischen 2 und 8 liegenden Faktoren werden durch zusätzliche Teilerstufen mit entsprechenden Zählern erzeugt, womit sich verschiedene Frequenzen entsprechend der Faktoren ausgeben lassen. So zählt der Zähler beispielsweise für  $N = 3$  drei Takte des VCOs.

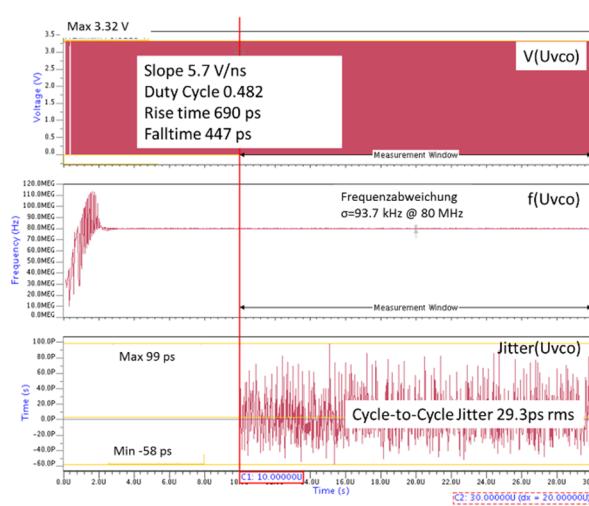

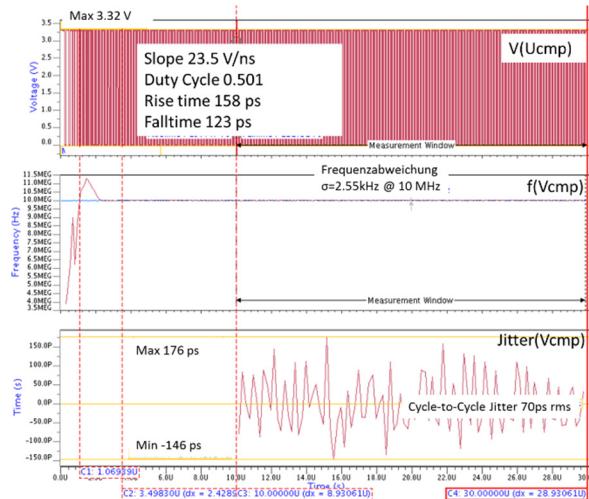

#### IV. SIMULATION

Die Simulationen sowie auch die Auswertungen nach Inbetriebnahme der Phasenregelschleife bezogen sich vor allem auf die PLL-Signale  $U_{REF}$ ,  $U_{CMP}$  und  $U_{VCO}$  und die Bestimmung der Ziehzeit  $T_p$  und Fangzeit  $T_L$ . Es wurden Temperatur- und Spannungsschwankungen sowie Toleranzen der CMOS-Parameter (durch Monte-Carlo-Simulation) miteinbezogen. Die Abbildungen 5 und 6 zeigen Simulationsergebnisse der Signale  $U_{VCO}$  und  $U_{CMP}$  bei normalen Betriebsbedingungen (keine Prozessschwankungen,  $T = 25^\circ\text{C}$ ). Es sind jeweils das Taktsignal, der entsprechende zeitabhängige Frequenzverlauf und eine Messung des Cycle-to-Cycle-Jitter von oben nach unten abgebildet.

Abbildung 5: Simulation von  $U_{VCO}$  mit 80 MHz Taktfrequenz.

Abbildung 6: Simulation von  $U_{CMP}$  mit 10 MHz Taktfrequenz.

Anhand Abbildung 5 kann ein Vergleich zwischen den Werteverhältnissen von Vergleichs- und Oszillatortsignal durchgeführt werden. Das Oszillatortsignal  $U_{VCO}$  schwingt im Mittel um die gewünschte Oszillatortfrequenz  $f_{VCO} = 80$  MHz. Dabei beträgt die mittlere Standardabweichung 93,72 kHz, also 0,12 % von 80 MHz. Es ist also zu erkennen, dass die Abweichungen keinen linear proportionalen Zusammenhang zu den ausgegebenen Frequenzen haben. Bei der gegenüber dem Referenzsignal von 10 MHz 8-fachen Frequenz des Ausgangstakts  $U_{VCO}$  ist die Standardabweichung mehr als 36-mal höher als beim auf die Referenz synchronisierten Vergleichssignal  $U_{CMP}$ . Das Taktjitter ist dagegen mit 29,3 ps geringer als beim Vergleichssignal.

In Abbildung 6 lässt sich am Vergleichssignal  $U_{CMP}$  der charakteristische Einschwingverlauf der PLL beobachten, welche den eingerasteten Zustand erreicht hat, sobald nach dem Ziehvorgang auf die Sollfre-

Abbildung 7: PLL-Layout.

Abbildung 8: Platine mit Wechselsockel.

quenz von 10 MHz die Vergleichsfrequenz  $f_{CMP}$  innerhalb einer Ober- und Unterschwingung auf die Sollfrequenz einrastet. Der ganze zeitliche Ablauf lässt sich in Zieh- und Fangzeit unterteilen, die sich zu jeweils 1,07  $\mu$ s bzw. 2,43  $\mu$ s aus der Simulation ergeben. Damit ist das Dimensionierungsziel der Fangzeit  $T_L = 2$   $\mu$ s relativ genau erreicht. Im eingerasteten Zustand schwingt das Rückkopplungssignal der PLL mit einer geringen Standardabweichung von 2,55 kHz um die Sollfrequenz 10 MHz, was in Relation etwa 0,026 % entspricht. Der Cycle-to-Cycle-Jitter beträgt dabei rund 70 ps.

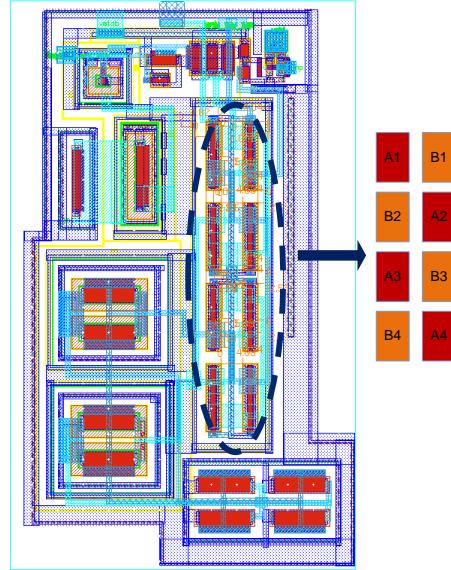

## V. LAYOUT

Abbildung 7 zeigt das Gesamtlayout der Phase-Locked Loop. Digital arbeitende Schaltungsteile wie PFD und Frequenzteiler sind mit ihren Gatterzellen und innenliegender Verdrahtung links oben bzw. rechts oben angeordnet. Die analogen Schaltungskomponenten, also VCO und Schleifenfilter sind mittig oben bis unten angeordnet. Die Ein- und Aus-

Abbildung 9: Verbleibende Störungen in der 3,3V-Versorgung.

gangssignale  $U_{REF}$ ,  $U_{CMP}$  (10 MHz) und  $U_{VCO}$  (80 MHz) liegen am oberen Rand. Die Verdrahtung befindet sich mit wenigen Ausnahmen auf den ersten beiden Metalllagen des Mikrochips, sodass die zwei übrigen Lagen für eine globale Chipverdrahtung mit Spannungsversorgung und anderen Schaltungen auf dem Chip nutzbar sind. Insgesamt misst das Schaltungslayout der PLL alleine 247  $\mu$ m x 188  $\mu$ m.

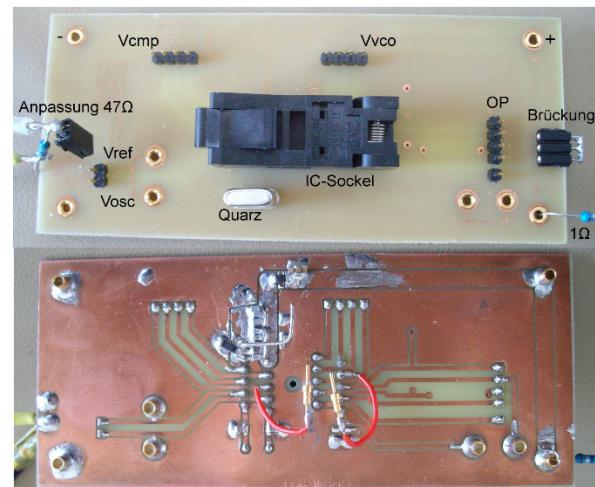

## VI. PCB-ENTWICKLUNG

Zu Testzwecken wurde die PLL zusammen mit weiteren Projekten gefertigt und in ein SOIC20 Gehäuse gepackt. Die Platine für die Laboruntersuchungen ist in Abbildung 8 dargestellt. Mittig auf dem PCB ist ein Wechselsockel für SOIC20-Gehäuse angeordnet, so dass Reihenmessungen über mehrere ICs möglich sind. Von dort führen Leitungen an die jeweiligen Steckerleisten und Buchsen zum Anschluss oder Abgriff von Signalen. Die Anschlüsse für die PLL befinden sich in der Draufsicht oben (Signale der Frequenzteilerstufen) und links (Buchsen sowie Steckerpins für  $U_{REF}$  und den Ausgang eines chipinternen Quarzoszillators). An die Buchsen am oberen Rand wird die Spannungsversorgung angeschlossen.

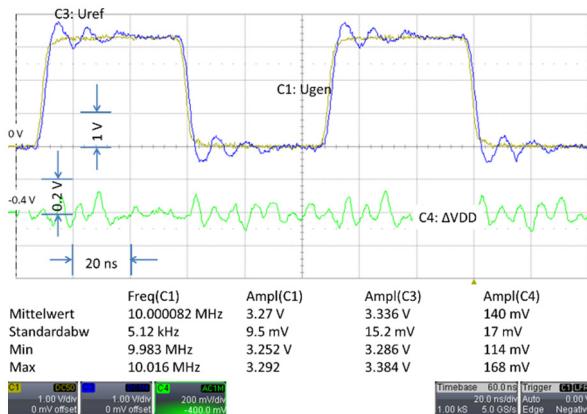

## VII. INBETRIEBNAHME

Bei Anschluss eines Taks an den Referenzeingang der PLL wurde eine deutlich erkennbare Überkopplung des 80 MHz-Ausgangs  $U_{VCO}$  auf die Spannungsversorgung beobachtet. Der Grund für diese HF-Einstrahlung auf die Stromversorgung konnte noch nicht vollständig festgestellt werden. Verschiedenste Untersuchungen ergaben, dass bereits chipintern geringe 80 MHz-Störschwingungen auf der Versorgungsspannung vorliegen, die durch parasitäre Leitungskapazitäten und Induktivitäten überkoppeln.

Eine deutliche Verringerung der Störungen wurde durch die Einbindung entsprechender Blockkondensatoren und Ferritkerne in die beiden Versorgungsleitungen auf der Platine bewirkt. Das Resultat ist mit-

Abbildung 10: Messung der Ziehzeit  $T_p$ .Abbildung 11: Messung der Einrastzeit  $T_L$ .

samt der Störung in Abbildung 9 zu sehen. C3 ist das am PLL-Eingang gemessene Referenzsignal  $U_{REF}$  und C4 die AC-gekoppelte Versorgungsspannung  $V_{DD}$  mit der Störung. C1 ist das vom Pulsgenerator gelieferte Signal. Die Amplitudenwerte der Störschwingungen konnten auf  $\pm 139$  mV reduziert werden. Trotzdem liegt hier noch Verbesserungspotential vor, z. B. durch Einfügen eigener Versorgungspads und die Verbesserung der chipinternen Anschlussleiterbahnen. Als Treiber der Ausgangssignale wurden fertige Pads aus der Library verwendet, die dazu ebenfalls genauer untersucht werden müssen.

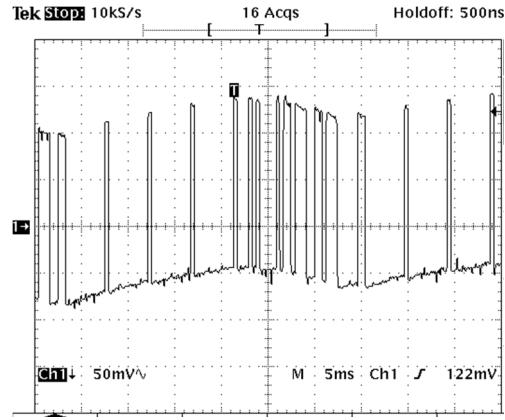

Die hier vorgestellten Messergebnisse konzentrieren sich auf die Betrachtung der Parameter  $T_L$  und  $T_p$  sowie des Vergleichssignals  $U_{CMP}$  im eingerasteten Zustand. Die Ziehzeit gibt dabei die Zeitdauer nach einer Frequenzstörung bis zum Erreichen der Sollfrequenz an.

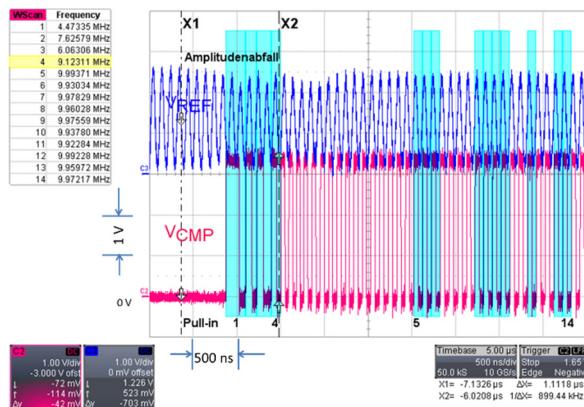

In den Abbildungen 10 und 11 sind die Signalverläufe des Referenzsignals  $U_{REF}$  und des Ausgangssignals  $U_{CMP}$  dargestellt. Zur Erfassung des Einschwingvorgangs der PLL können verschiedene Messansätze gewählt werden, wie z. B. das Aufstarten eines externen Referenzgenerators oder der Spannungsversorgung bei schon aktivem Referenzsignal  $U_{REF}$ . Hier wird eine Variante gezeigt, die mit Hilfe eines Chip-

Abbildung 12: Messung im eingerasteten Zustand.

internen Kristalloszillators durchgeführt wurde und hinsichtlich der Auswertung des PLL-Einschwingvorgangs anschauliche Messungen und damit auch sinnvolle Ergebniswerte liefert. Dazu wird das vom Kristalloszillator generierte 10 MHz-Referenzsignal an den Referenzanschluss der PLL angeschlossen und auf die Flanken des Referenztakts Single-Shot getriggert.

Abbildung 10 zeigt die Erfassung der Ziehzeit  $T_P$ . Die Zeitmessung wird anhand der Momentanfrequenzen der Signalpulse durchgeführt. Dazu wird zur Messung der Ziehzeit  $T_P$  abgeprüft, welche Taktpulse Momentanfrequenzen von unter 10 MHz aufweisen (grau hinterlegt). Dies trifft auf die Pulse 1-4 zu Beginn des Anschwingens zu. Danach wird die 10 MHz-Sollfrequenz überschritten, was den Einrastvorgang einleitet. Anhand des schon vor Puls 1 eintretenden Amplitudenabfalls kann die Ziehzeit  $T_P \approx 1,11 \mu\text{s}$  abgelesen werden.

Zur Messung der Fangzeit werden in Abbildung 11 Pulse mit Momentanfrequenzen über 9,9 MHz hervorgehoben, was auf den gesamten Bereich nach dem Ziehvorgang zutrifft. Anhand der Betrachtung von Abweichungen gegenüber der 10 MHz-Frequenz lässt sich feststellen, wann die PLL eingerastet ist. Als Schwellwert, den die Frequenzabweichungen nicht überschreiten dürfen, damit die PLL als eingerastet gilt, wurde die Standardabweichung herangezogen. Diese Bedingung wird ab Puls 29 erfüllt, was einer gemessenen Fangzeit  $T_L = 2,72 \mu\text{s}$  entspricht. Addiert man die Ziehzeit, so ergibt sich eine Gesamteinenschwingzeit von 3,83  $\mu\text{s}$ .

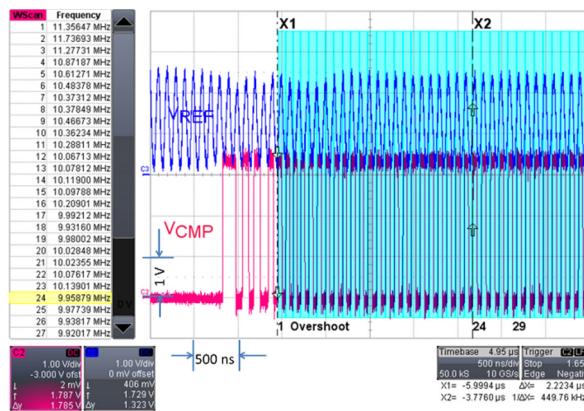

Abbildung 12 zeigt die Messwerte des Vergleichssignals  $U_{CMP}$  im eingerasteten Zustand. Im abgebildeten Vergleichssignal  $U_{CMP}$  sind die Restungenaugkeiten in der Signalamplitude, die durch die 80 MHz-Störungen in der Spannungsversorgung verursacht werden, zu erkennen. Diese haben aber keine größeren Auswirkungen auf die Richtigkeit des 3,3 V-Signalpegels, der im Mittel bei 3,338 V liegt. Die Stan-

Tabelle 2: Ergebniszusammenfassung.

| Parameter                                | Symbol           | Spezi-<br>fikati-<br>on | Simula-<br>tion    | Messung            |

|------------------------------------------|------------------|-------------------------|--------------------|--------------------|

| Versorgungs-<br>spannung                 | $V_{DD}$         |                         | 3,3 V              |                    |

| Referenz-<br>frequenz                    | $f_{REF}$        |                         | 10 MHz             |                    |

| Teilerfaktor                             | $N$              |                         | 2-8                |                    |

| Ziehzeit                                 | $T_P$            | N/A                     | 1,07 $\mu\text{s}$ | 1,11 $\mu\text{s}$ |

| Fangzeit                                 | $T_L$            | 2 $\mu\text{s}$         | 2,43 $\mu\text{s}$ | 2,72 $\mu\text{s}$ |

| Einschwing-<br>zeit                      | $T_P + T_L$      | N/A                     | 3,5 $\mu\text{s}$  | 3,83 $\mu\text{s}$ |

| Frequenz-<br>abweichung<br>(1 $\sigma$ ) | $\Delta f_{CMP}$ | N/A                     | 2,56 kHz           | 47,9 kHz           |

| Jitter                                   |                  | N/A                     | 70 ps              | 804 ps             |

dardabweichung der Frequenz von  $U_{CMP}$  bei 10 MHz beträgt 47,91 kHz und der Clock-Jitter 804 ps.

Diese Werte übersteigen deutlich die Ergebnisse der Simulation, was in erster Linie auf die realen Betriebsverhältnisse und auch auf die Ungenauigkeiten in der PLL-Stromversorgung und vor allem auf die Signalverhältnisse der Referenzquelle zurückzuführen ist, die einen geringeren und deutlich verschliffeneren Taktpegel ausgibt als beabsichtigt. Tabelle 2 fasst die wichtigsten Ergebnisse zusammen.

## VIII. FAZIT

Es wurde eine PLL mit 10 MHz Referenztakt und Ausgangstakten im Bereich 10 MHz bis 80 MHz realisiert und charakterisiert. Im Verlauf verschiedener Messungen konnte weitgehend die korrekte Funktionsweise der PLL festgestellt werden. Das Ziel der Dimensionierung auf eine Einrastzeit von 2  $\mu\text{s}$  wird mit geringer Abweichung erreicht. Anhand der bestehenden Schaltung können Ansätze zur Weiterentwicklung der PLL-Funktionalität für weitere Hochschulprojekte ausgearbeitet werden.

## DANKSAGUNG

Die Autoren bedanken sich bei Frau Ninja Koetsier, die das Toplevel-Layout umgesetzt hat und bei Goran Bratek, der den Quarzoszillator entworfen hat. Besonderer Dank gilt der MPC-Gruppe für die Unterstützung bei der Entwicklung und der Chipherstellung.

### LITERATURVERZEICHNIS

- [1] R. E. Best, *Phase-Locked Loops: Design, Simulation, & Applications*, McGraw-Hill, 3. Auflage, 1997.

- [2] B. Razavi, *Monolithic Phase-Locked Loops and Clock-Recovery Circuits*, IEEE Press, 1996.

- [3] B. Razavi, *Design of Analog CMOS Integrated Circuits*, McGraw-Hill, 2001.

- [4] G. Bratek, J. Giehl, B. Vettermann, „Design eines Quarzoszillators in 0,35 µm CMOS-Technologie“, *Tagungsband Workshop der Multiprojektkip-Gruppe*, S. 9 – 14, Göppingen 2010, ISSN 1862-7102.

Christian Eschenbach erhielt 2014 den akademischen Grad des Bachelor of Science im Fachbereich Informationstechnik mit Schwerpunkt Nachrichtentechnik/Elektronik der Hochschule Mannheim. Dort wird er 2015 ebenfalls den Master of Science in Informationstechnik abschließen.

Bernd Vettermann ist seit 1994 an der Hochschule Mannheim im Institut für integrierte Schaltkreise als Ingenieur tätig. Er erhielt 2006 von der Universität Mannheim den akademischen Grad eines Doktors der Naturwissenschaften.

Jürgen Giehl erhielt den akademischen Grad Diplom-Physiker 1990 von der Universität Mainz und den Dr.-Ing. in Elektrotechnik von der Universität Siegen im Jahr 1997. Von 1997 bis 2007 hat er bei ITT Semiconductors (seit 1998 Micronas GmbH) in Freiburg i. Breisgau als Projektmanager und Designer für analoge Schaltungen gearbeitet. Seit 2007 ist er Professor mit Lehrgebiet Entwurf integrierter Schaltkreise an der Hochschule Mannheim.

# Ein Aufwärts-Wandler-IP im 180 nm CMOS-Prozess zur Versorgung von ASICs mittels Energy Harvesting

Michael Hiller, Marc Locherer, Gerhard Forster

**Zusammenfassung**—Mit der zunehmenden Vernetzung (Internet of Things) wächst die Zahl der autonomen elektronischen Systeme stark an, so dass die dezentrale Stromversorgung dieser Systeme an Bedeutung gewinnt. Der anhaltende Trend zur Reduktion der Verlustleistung in sogenannten Micropower-ASICs ermöglicht zunehmend deren Betrieb durch Energie, die unmittelbar der Umwelt entnommen wird (Energy Harvesting). Häufig ist die verfügbare Energie ausreichend, jedoch die vom Wandler gelieferte Spannung zu niedrig für den Betrieb elektronischer Schaltungen. Ziel ist es daher, ein IP verfügbar zu haben, mit dessen Einsatz ein Chip betrieben werden kann, auch wenn die Versorgungsspannung noch unterhalb der Schwellenspannung der Transistoren liegt. Im vorliegenden Beitrag wird der Entwurf eines Aufwärtswandlers beschrieben, das ab einer externen Versorgungsspannung von 170 mV eine interne Versorgungsspannung von 1,8 V erreicht und dabei 10  $\mu$ A abgeben kann. Mit höherer Versorgungsspannung nimmt die verfügbare Leistung zu. Der Wandler ist vollständig in einem 180 nm CMOS-Prozess integriert. Er beinhaltet einen Low-Voltage-Oszillator mit Resonator sowie eine Ladungspumpe. Externe Bauelemente sind somit nicht erforderlich.

**Schlüsselwörter**—Aufwärtswandler, Oszillator, Ladungspumpe, Energy Harvesting.

## I. EINLEITUNG

Das Internet of Things (IoT) ist schon heute ein wichtiges Thema der Mikroelektronik-Entwicklung und wird in Zukunft eine noch größere Rolle spielen. Es bringt eine große Zahl autonomer elektrischer Systeme mit sich, welche separat mit elektrischer Energie versorgt werden müssen. Energie ist in ihren verschiedenen Erscheinungsformen allgegenwärtig, allerdings nur bedingt nutzbar. Wird die Energie aus der Umwelt in eine nutzbare Energieform überführt (Energy Harvesting), so lässt sich eine autarke Energieversorgung von Verbrauchern realisieren. Damit

Michael Hiller, mhiller@mail.hs-ulm.de, Mark Locherer, locherer@mail.hs-ulm.de und Gerhard Forster, forster@hs-ulm.de sind Mitglieder der Hochschule Ulm, Prittwitzstraße 10, 89075 Ulm.

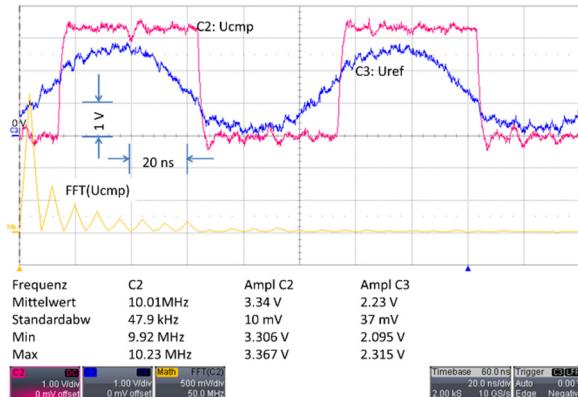

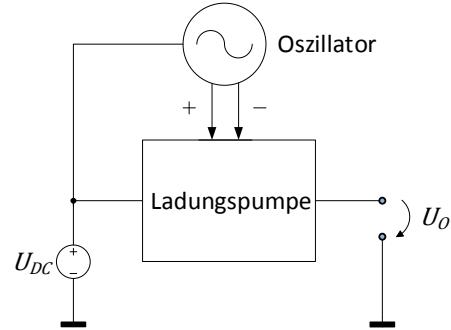

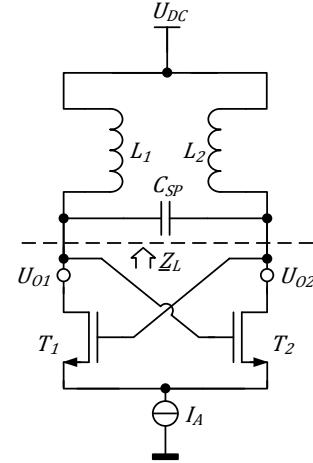

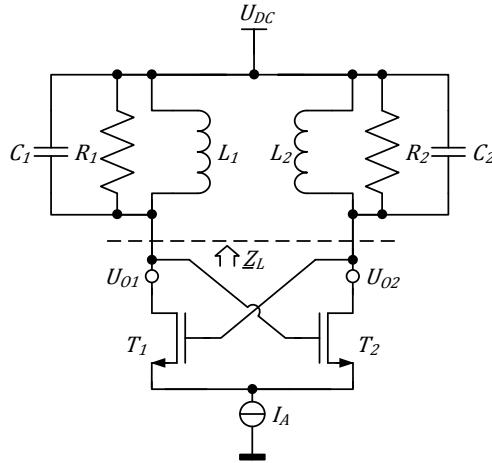

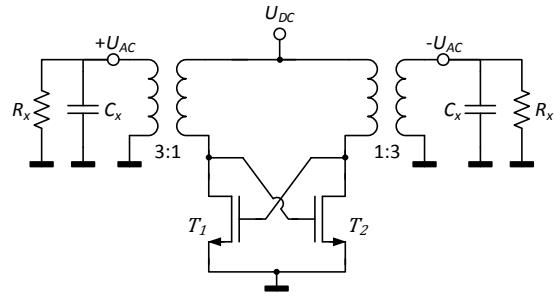

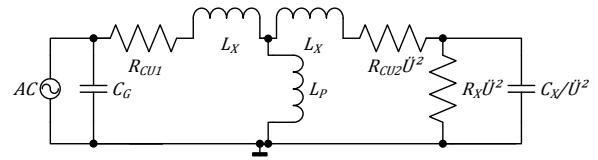

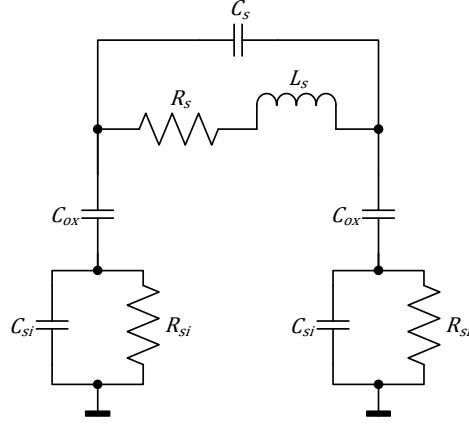

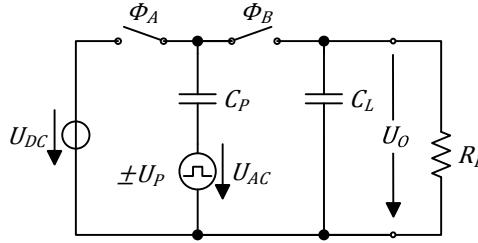

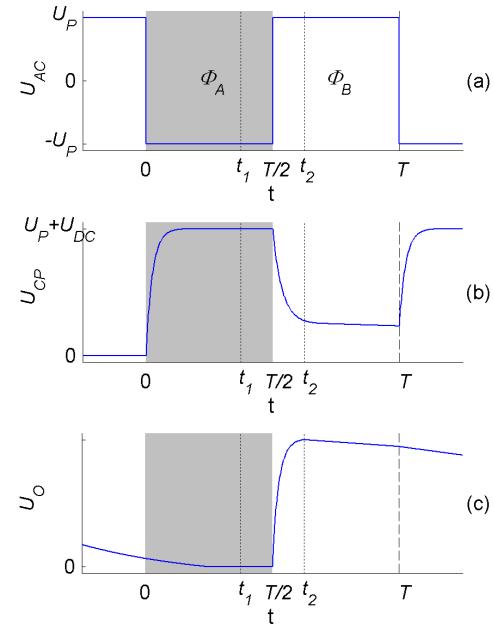

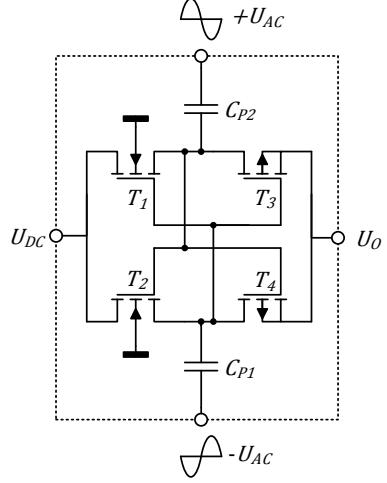

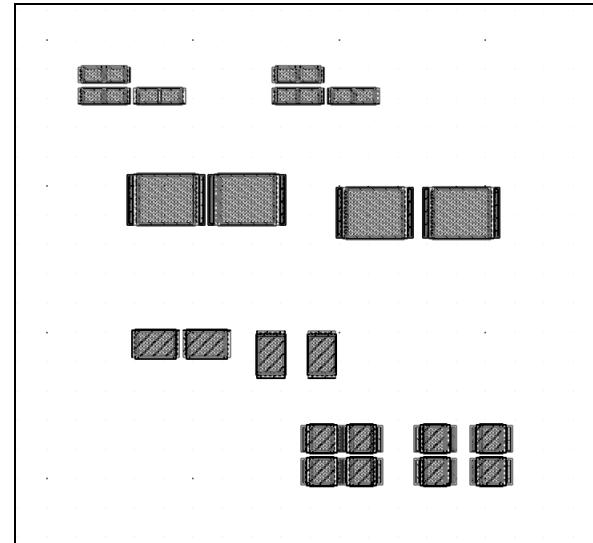

Abbildung 1: Schaltungskonzept mit Ladungspumpe und symmetrischem Oszillator als Taktquelle.

sind für einen fortlaufenden Betrieb keine Batteriewchsel oder das Laden des Gerätes erforderlich. Problematisch beim Energy Harvesting ist, dass häufig nur geringe Leistungen und Spannungen unterhalb der Transistorschwellenspannung zur Verfügung stehen. So sind bei der Nutzung von Körperwärme am Menschen mittels Peltier-Elementen in der Regel nur Spannungen unter 200 mV erzielbar.

Ziel dieser Arbeit war es, eine Schaltung zu entwickeln, welche den Betrieb eines ASICs mit Eingangsspannungen  $U_{DC} < U_{TH}$  zulässt und damit eine Versorgung des ASICs über Energy Harvesting erlaubt. Da es sich sowohl bei der Ein- als auch bei der Ausgangsspannung um eine Gleichspannung handelt, entspricht das System einem DC/DC Wandler, wobei folgende Zielspezifikationen angesetzt wurden:

- Eingangsspannung  $U_{DC} \leq 150$  mV

- Ausgangsspannung  $U_o \geq 1,6$  V (typ. 1,8 V)

- Laststrom  $I_L \geq 10 \mu$ A

Die Schaltung soll vollständig integriert sein und ohne externe Bauelemente auskommen.

Mit ähnlichen Zielsetzungen haben sich bereits unterschiedliche Arbeitsgruppen befasst. Gemeinsames Merkmal dieser Arbeiten ist jedoch, dass entweder eine höhere Eingangsspannung vorausgesetzt wird [1]-[4] oder zusätzliche Bauelemente erforderlich sind (z.B. Transformatoren mit großer Übersetzung), die sich nicht monolithisch integrieren lassen [5]-[9]. H. Fukuta et al. berichten hingegen erstmals von einem vollständig integrierten Aufwärtswandler, realisiert in einem 65 nm CMOS-Prozess [10].

Der vorliegende Beitrag befasst sich mit dem Systementwurf und der Umsetzung eines vollintegrierten

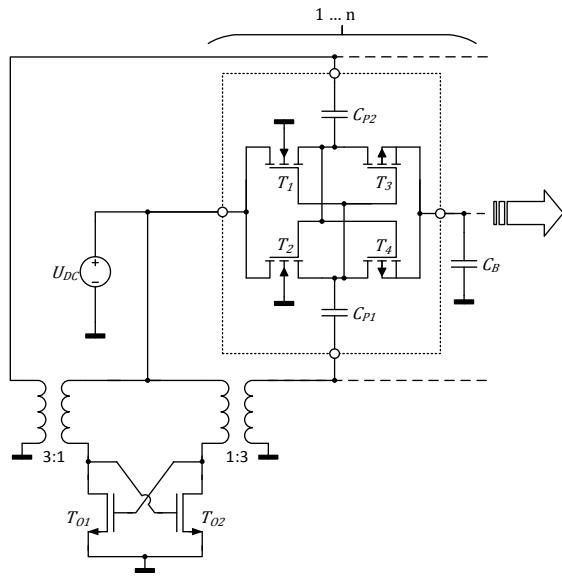

Aufwärtswandlers in einem 180 nm CMOS-Prozess der Fa. UMC. Das folgende zweite Kapitel gibt eine kurze Einführung in das System- und Schaltungskonzept. Das dritte Kapitel befasst sich mit dem Schaltungsentwurf des Gegentaktoszillators und der dazu erforderlichen Modellierung des vollintegrierten Transformators. Im vierten Kapitel wird, ausgehend von einer theoretischen Analyse der Prinzipschaltung, die Entwicklung der Ladungspumpe beschreiben. Das Gesamtsystem und die ermittelten Ergebnisse werden schließlich im fünften Kapitel vorgestellt. Der Beitrag schließt mit einer Zusammenfassung und dem Ausblick.

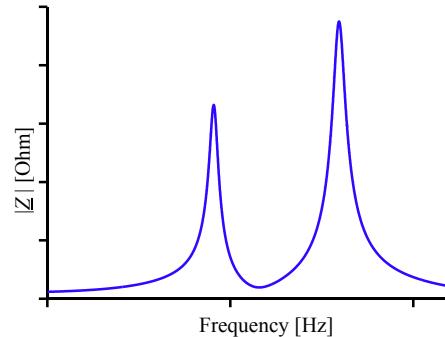

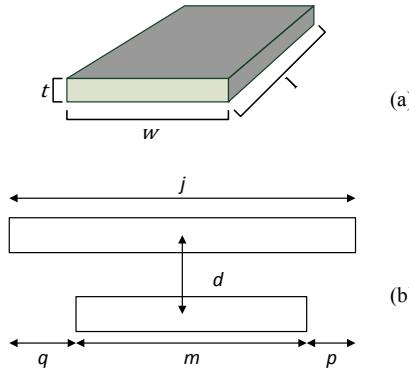

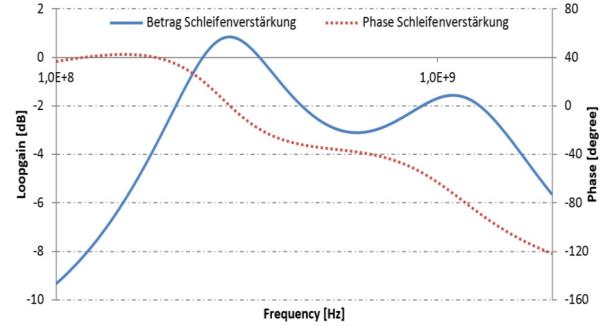

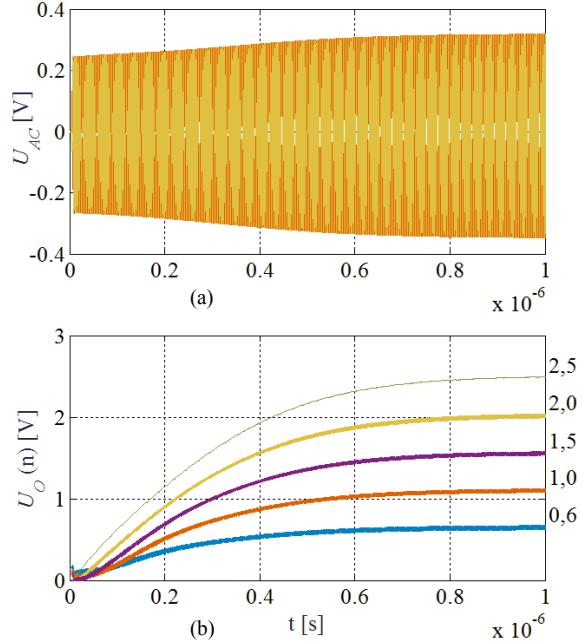

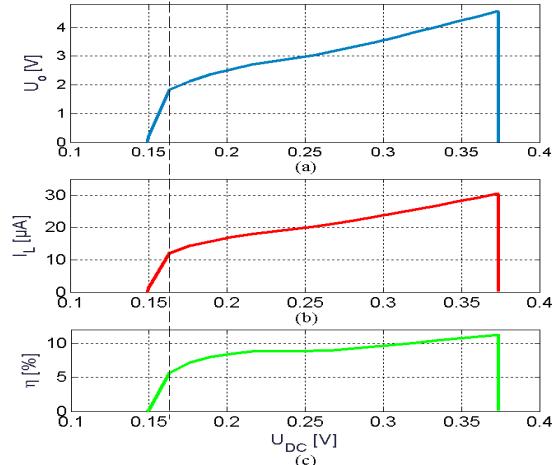

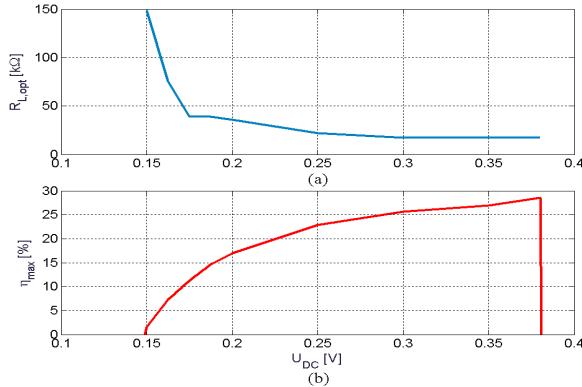

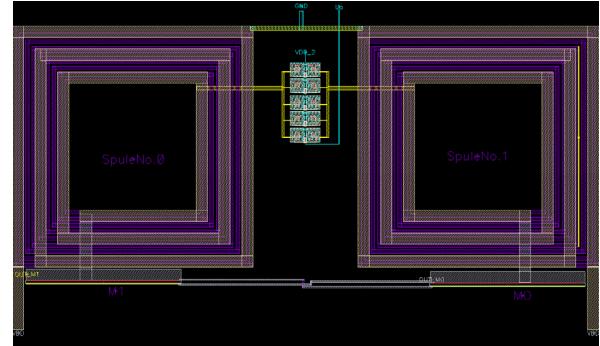

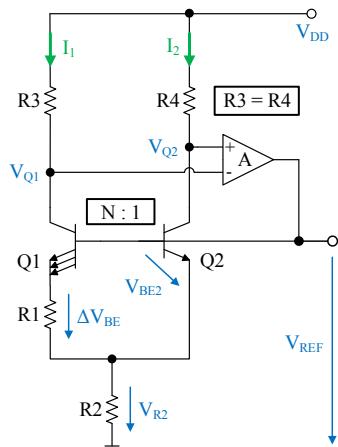

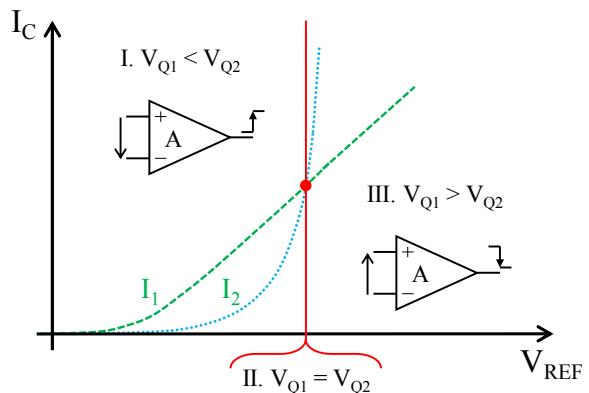

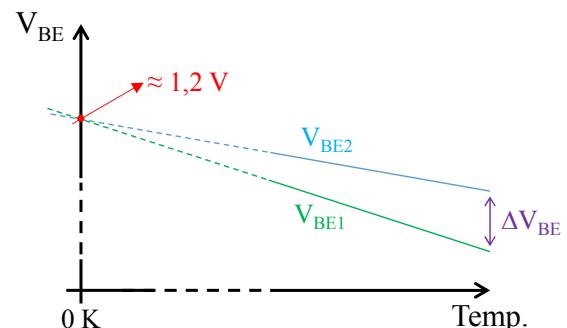

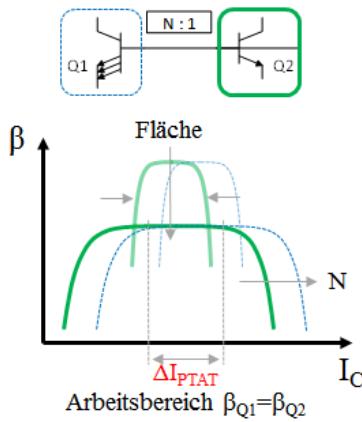

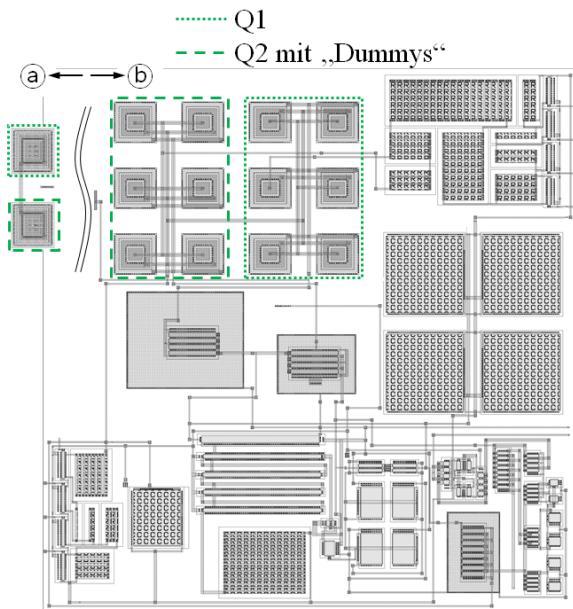

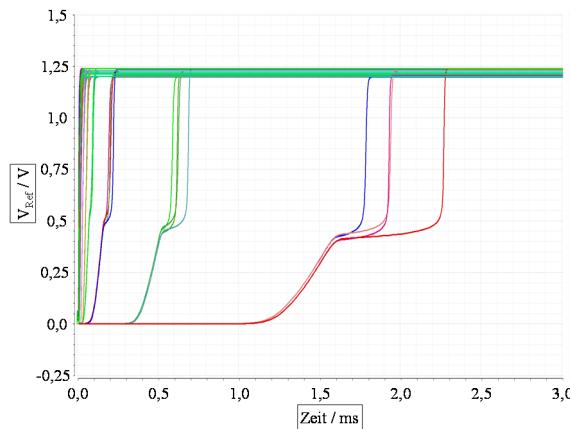

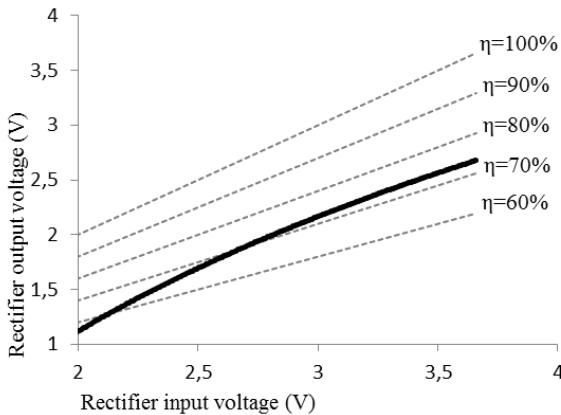

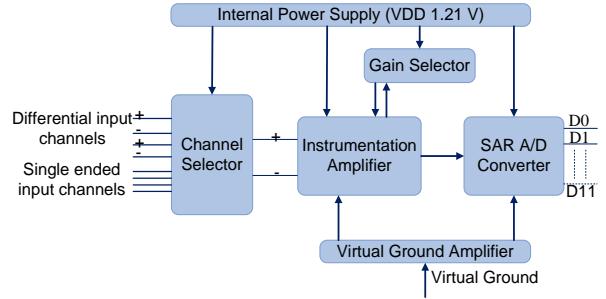

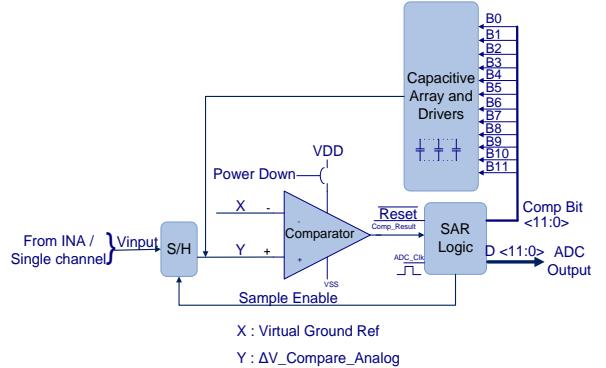

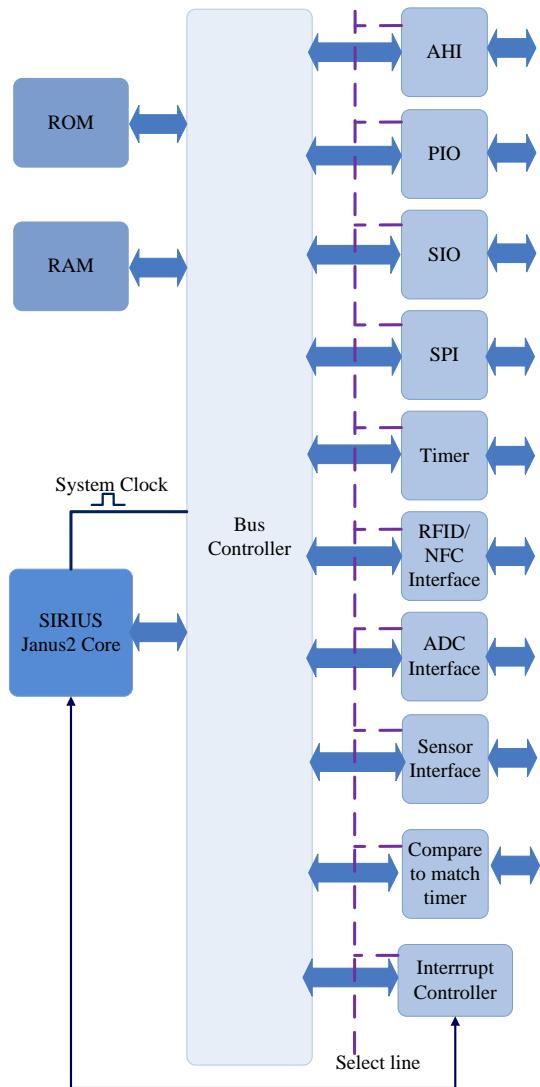

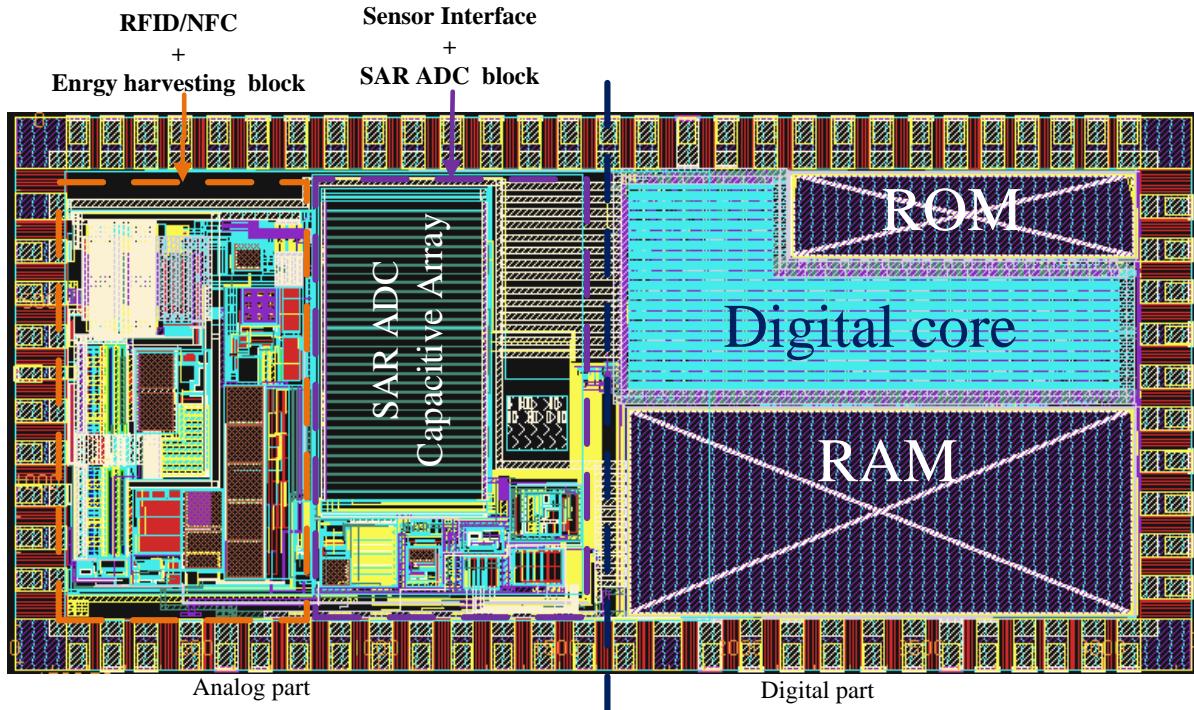

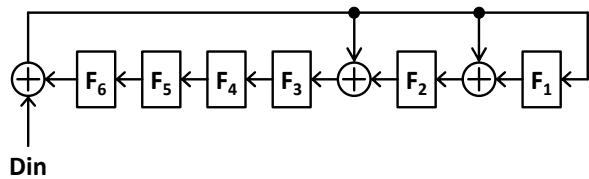

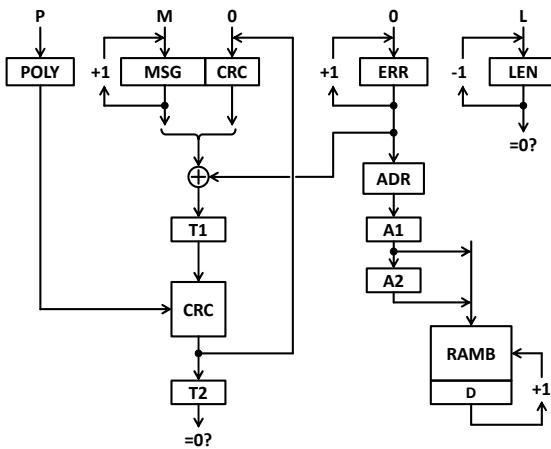

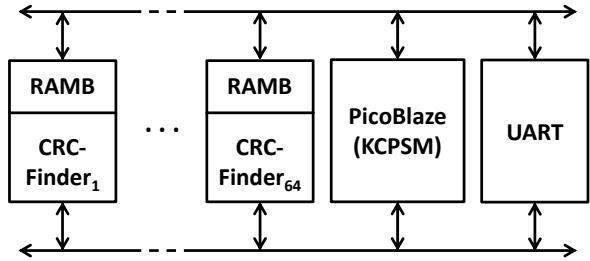

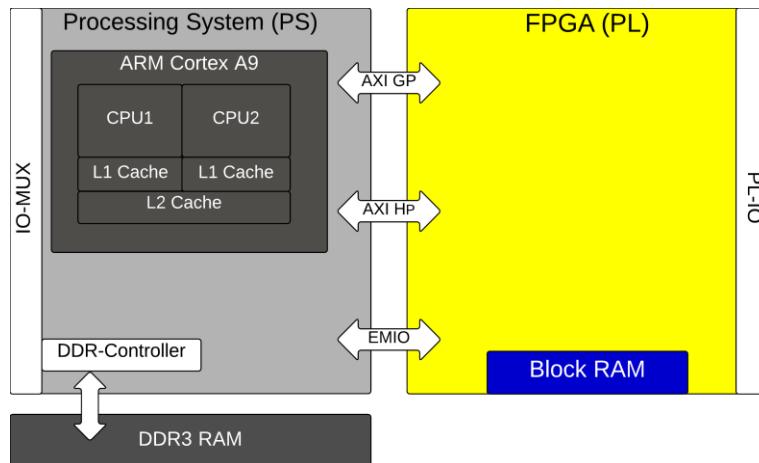

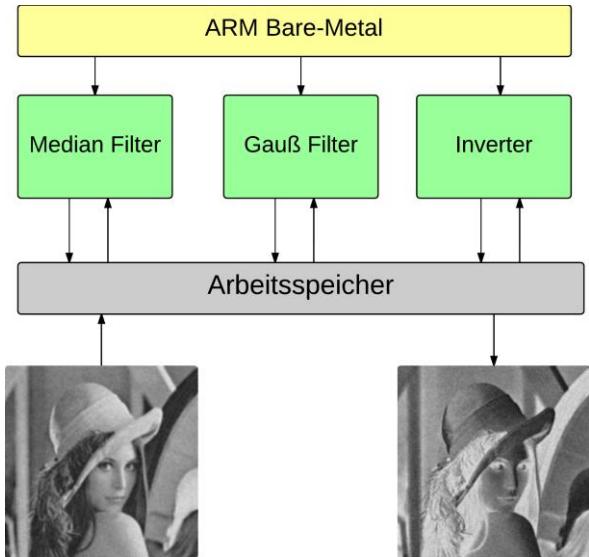

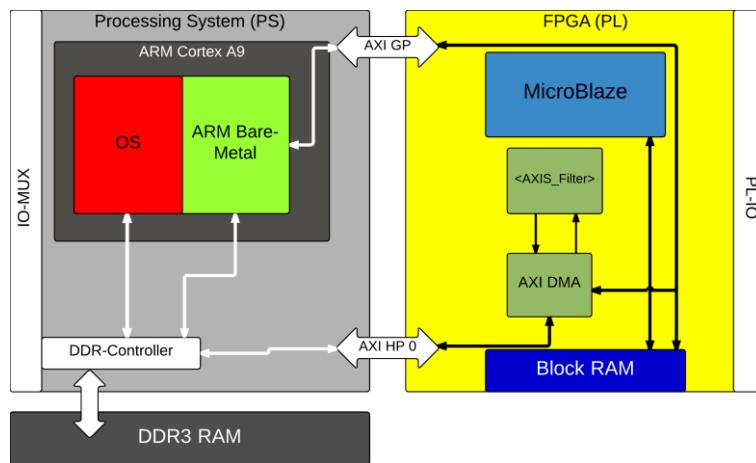

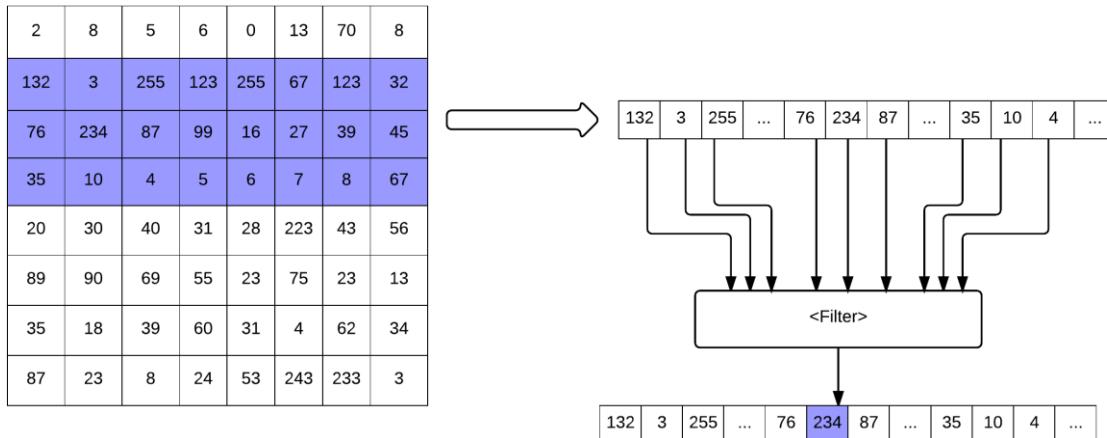

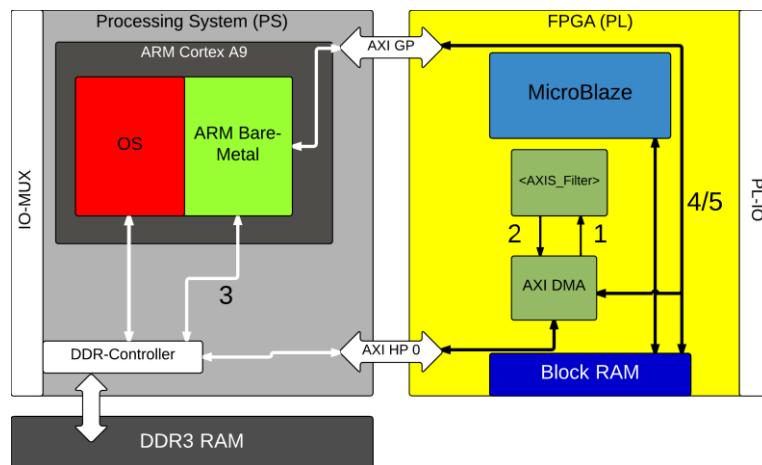

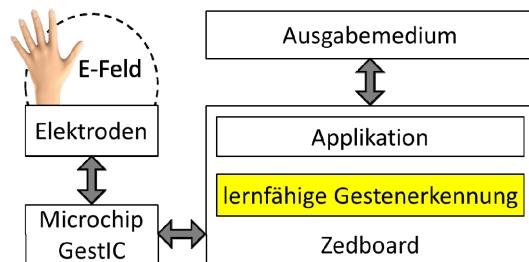

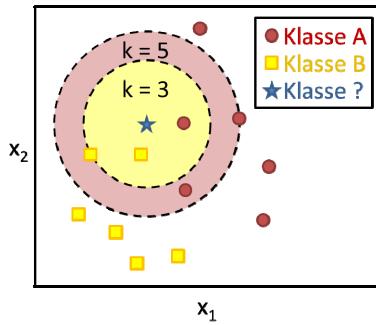

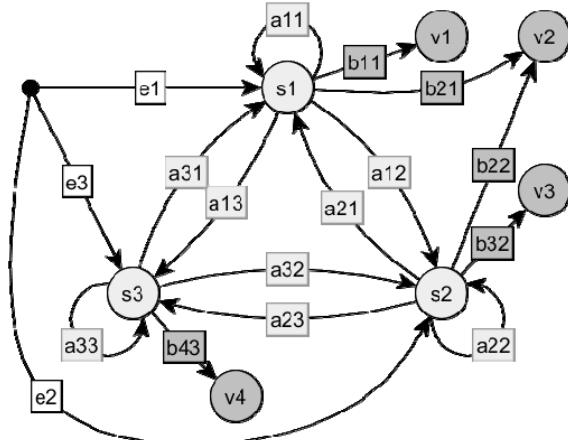

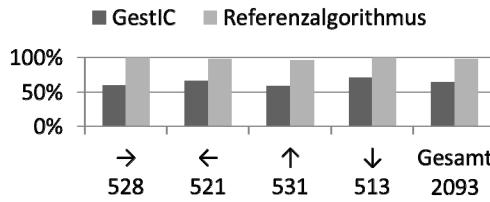

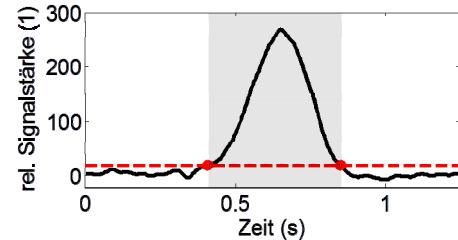

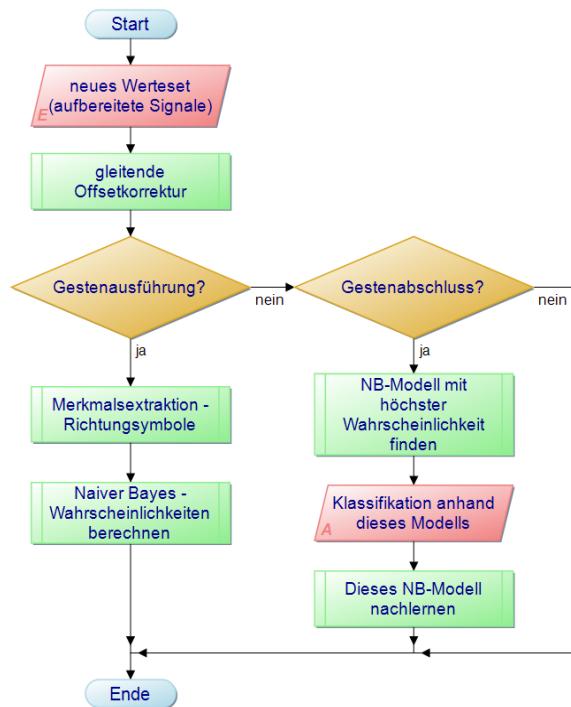

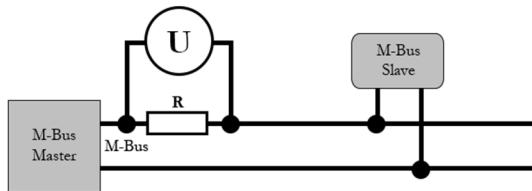

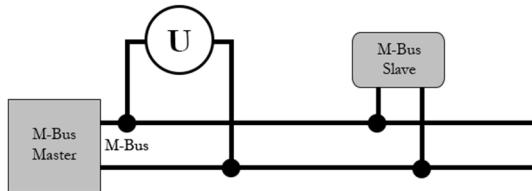

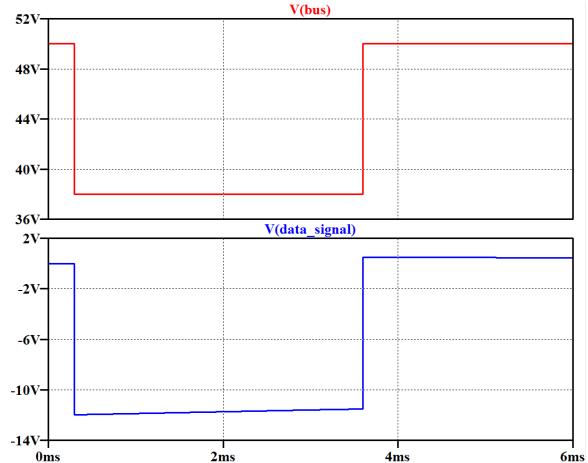

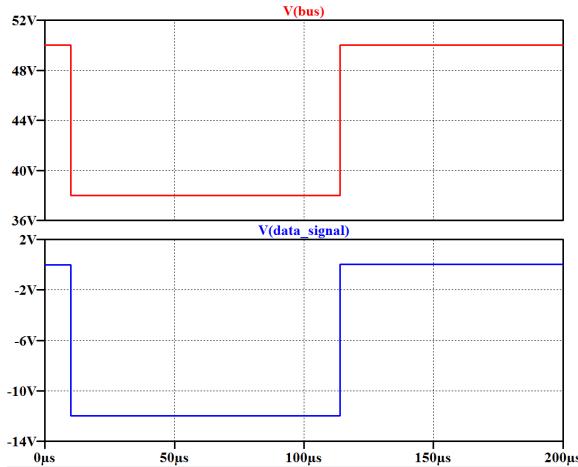

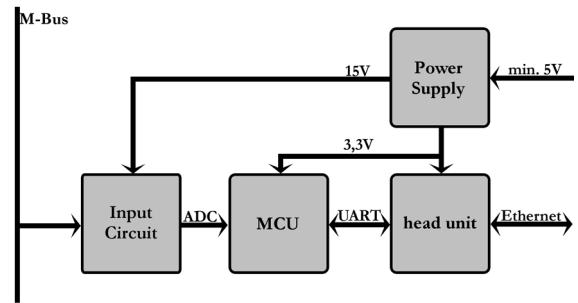

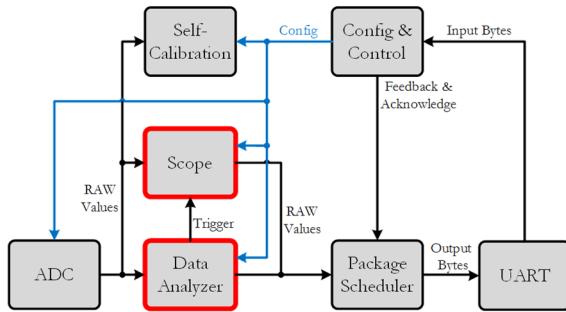

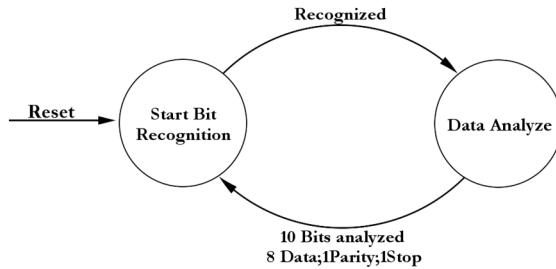

## II. SCHALTUNGSKONZEPT