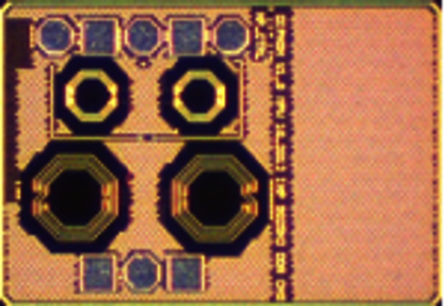

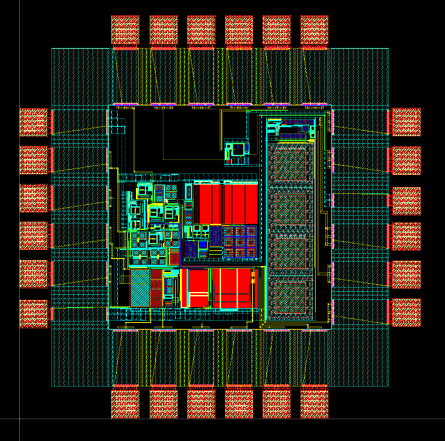

MMIC-Phasenschieber für den Einsatz in phasengesteuerten Arrayantennen im C-Band

Verantwortliche für den Entwurf:

Dennis Dario Aschenbrenner, Christoph Schick

Hochschule Konstanz

Fakultät für Elektrotechnik und Informationstechnik

Brauneggerstr. 55, 78462 Konstanz

| Entwurfsverfahren | Full Custom Design |

|---|---|

| Technologie | IHP SG25H3 250 nm BiCMOS 5M |

| Chipfläche | 0,7 mm x 1,0 mm |

| Gehäuse | Bare die |

| Funktionsblöcke | Chip mit schaltbarer Einfügungsphase |

| Funktion | Bei einer Betriebsfrequenz von 5.4GHz ermöglicht der Chip die spannungs-gesteuerte Änderung der Einfügungsphase um 0° bzw. -180°. Der Chip kommt zusammen mit dem ebenfalls im Q1/2014 für die Hochschule Konstanz gefertigten Phasenschieber im Speisenetzwerk einer elektronisch schwenkbaren Antenne zum Einsatz. |

| Herstelldatum | I. Quartal 2014 |

| Kostenträger | MPC-Gruppe Baden-Württemberg |

Chip-Daten zum Download:

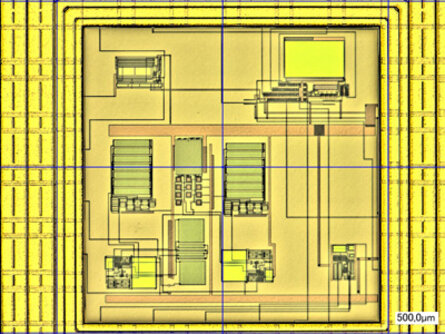

Operationsverstärker, Bandgap-Referenz, Quarzoszillator und PLL

Verantwortliche für den Entwurf:

Marcio Camoleze de Andrade, Andreas Arnold, Goran Bratek, Christian Eschenbach, Ninja Koetsier, Gaelle Ritha Ngassa Tchouta, Bernd Vettermann, Jürgen Giehl

Hochschule Mannheim

Institut für Entwurf integrierter Schaltkreise

Paul-Wittsack-Straße 10, 68163 Mannheim

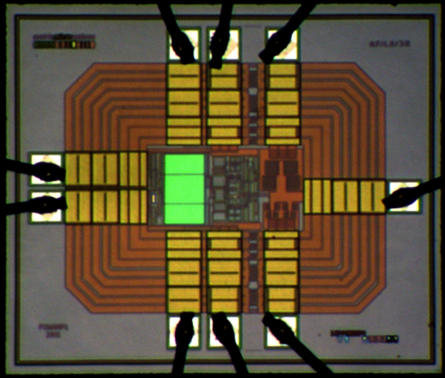

| Entwurfsverfahren | Full Custom Design |

|---|---|

| Technologie | AMS S35D4M5 0,35 μm CMOS 4M/2P |

| Chipfläche | 2,35 mm² |

| Gehäuse | SOIC 20 |

| Funktionsblöcke | Operationsverstärker, Bandgap-Referenz, Strombank, Quarzoszillator, Peaking Current Source, VCO (voltage controlled oscillator), Frequenzteiler mit Teilerverhältnis n = 2 … 8, Treiberpads |

| Funktion | Es handelt sich um einen Testchip mit 4 unterschiedlichen Baugruppen. Der Operationsverstärker (OTA) hat eine Leerlaufverstärkung AV0 = 80 dB und eine Transitfrequenz ft = 25 MHz. Er ist auf maximale kapazitive Last CLmax = 50 pF ausgelegt. Die Bandgap-Referenz verfügt über einen Ausgang mit 1.21 V und einen gepufferten Ausgang mit 1.65V. Der Quarzoszillator liefert eine Taktfrequenz fosc = 10 MHz bei einer maximalen Frequenzabweichung von 1300 ppm. Mit der eingebauten PLL lassen sich daraus die Frequenzen fout = 80, 40, 26.7, 20, 16, 13.7,11.3 und 10 MHz erzeugen. |

| Herstelldatum | II. Quartal 2014 |

| Kostenträger | MPC-Gruppe Baden-Württemberg |

| Veröffentlichung | Goran Bratek, Jürgen Giehl, Bernd Vettermann, Design eines Quarzoszillators in 0,35μm CMOS-Technologie, Vortrag am 43. MPC-Workshop, 5. Februar 2010, Göppingen, veröffentlicht im Tagungsband ISSN 1862-7102, S. 9-14, Ausgabe 43, Hrsg. Hochschule Ulm |

Chip-Daten zum Download:

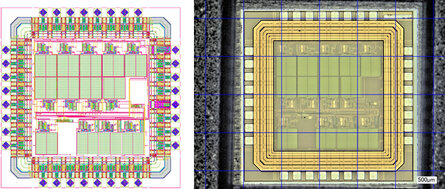

Operationsverstärker und On-Chip Tiefpass-Filter 3. und 8.Ordnung

Verantwortliche für den Entwurf:

Andreas Arnold, Frauke Bohinsky, Irina Ohm, Paul Kamou Fansi, Ninja

Koetsier, Bernd Vettermann, Jürgen Giehl

Hochschule Mannheim

Institut für Entwurf integrierter Schaltkreise

Paul-Wittsack-Straße 10, 68163 Mannheim

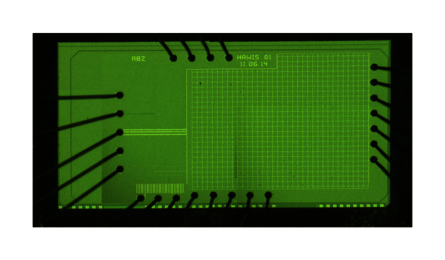

| Entwurfsverfahren | Full Custom Design |

| Technologie | AMSS35D4M5 0,35 mCMOS 4M/2P |

| Chipfläche | 2,04 mm x 2,04 mm |

| Gehäuse | QFN32 |

| Funktionsblöcke | Operationsverstärker,Strombank, PeakingCurrent Source, Filter 3.und 8. Ordnung |

| Funktion | Operationsverstärker (OTA,ft =1kHz,AV0 = 100 dB,CLastmax = 50 pF) Aktive On-Chip Tiefpassfilter 3.und 8.Ordnungmit einer Eckfrequenz von 50 Hz.Die Eckfrequenz wird hierbei durch die Miller-kompensierten Opera-tionsverstärker bestimmt.Das Filter 3.Ordnungenthält 3 OPs und hat eine Verstärkung von 30 dB.Das Filter 8.Ordnungenthält 8 OPs,hat keine Verstärkung (0 dB) und muss noch extern beschältet werden. |

| Herstelldatum | II. Quartal 2014 |

| Kostenträger | MPC-Gruppe Baden-Württemberg |

| Veröffentlichung | Ninja Koetsier, Frauke Bohinsky, Albrecht Zwick, Marcio Camoleze de Andrade, Jürgen Giehl, Bernd Vettermann,Design und Verifikation von On-Chip Tiefpass-Filtern 3.und 8. Ordnung mit Operationsverstärkern in einer 0.35pm CMOS Technologie, Vortrag am 53. MPC-Workshop,06. Februar 2015, Esslingen |

Chip-Daten zum Download:

HSMannheim_OPV2.pdf (291,2 KB)

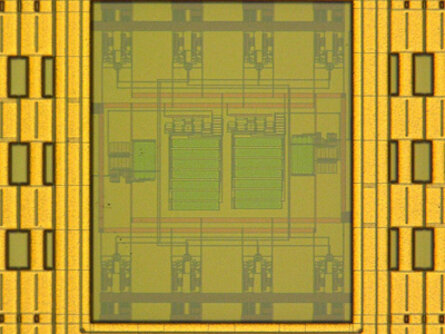

High-speed MultiplexerVDemultiplexer-IC

Verantwortliche für den Entwurf:

Christoph Rahnke, Josua Arndt, Bernd Vettermann, Jürgen Giehl

Hochschule Mannheim

Institut für Entwurf integrierter Schaltkreise

Paul-Wittsack-Straße 10, 68163 Mannheim

| Entwurfsverfahren | Full Custom Design |

| Technologie | AMS S35D4M5 0,35 mCMOS 4M/2P |

| Chipfläche | 1,4 mmx1,3 mm |

| Gehäuse | SOIC 16 |

| Funktionsblöcke | Komparatoren, PeakingCurrent Source,Logikblöcke, Buffer, Schalter |

| Funktion | Der Chip enthält einen Double Balanced Mischer (jeweils1:4) mit gemeinsamer Ansteuerlogik und kann sowohl als MUX (Sender) als auch als DEMUX (Empfänger) betrieben werden. Das Eingangssignal wird periodisch (jeweils1/4 Periode) auf die 4 Ausgänge gelegt (für DEMUX Betrieb, bei MUX umgekehrt). Die minimale MUX-Periode beträgt 8 ns für das UKW Band (DAB). Der Durchgangswiderstand der Schalter beträgt weniger als 10 Ohm. Die Ansteuerung erfolgt durch 2 differentielle 90° phasenverschobene Cosinusschwingungen (IQ) der MUX-Frequenz, die durch eine externe DDS erzeugt werden. Die internen Rechtecksignale werden über Komparatoren daraus erzeugt. Die Referenzströme werden durch eine Peaking Current Source erzeugt. |

| Herstelldatum | II. Quartal 2011 |

| Kostenträger | MPC-Gruppe Baden-Württemberg |

| Veröffentlichung | C. Rahnke, J. Giehl, B. Vettermann, „Entwurf eines High-Speed Multiplexers/De-multiplexers für einen Mischer in 0,35 m Technologie“, Workshop der Multiprojekt-Chip-Gruppe Baden-Württemberg, Karlsruhe, Tagungsband ISSN 1862-7102, S. 29 - 34, Ausgabe 42, Juli 2009. |

Chip-Daten zum Download:

HSMannheim_Mux.pdf (95,1KB)

Low Frequency Continuous Phase Differential Quadrature Phase Shift KeyingFront End ASIC

Verantwortliche für den Entwurf:

Waldemar Grünwald,Daniel Bau,Dirk Jansen

Hochschule Offenburg

Badstraße 24, 77652 Offenburg

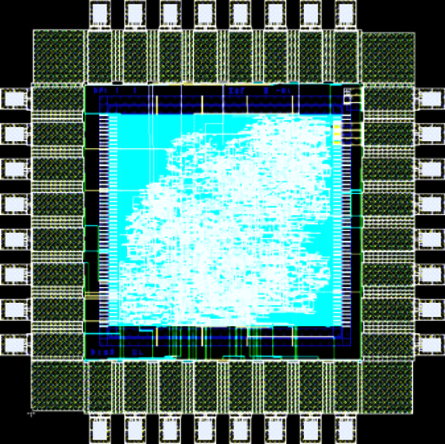

| Entwurfsverfahren | Standardzellen |

| Technologie | UMC CMOS 0,18 µm |

| Chipfläche | 1,36 mm x 1,36 mm |

| Gehäuse | QFN 32 |

| Funktionsblöcke | Universal transceiver based on inductive low frequency near field transmission |

| Funktion | Dieser Chip beinhaltet ein Frontend für die Übertragung von digitalen Daten auf einem Niederfrequenzträger von ca. 100 kHz - 200 kHz mit differenzieller Quadraturphasenmodulation. Die Datenrate beträgt nominel 9600 Baud. Das angewandte Verfahren enthält einen Gauss-Shift-Übergang, wodurch eine besonders niedrige Übertragungsbandbreite realisiert werden konnte. Nähere Einzelheiten sind der Dissertation von Nidal Fawaz 2009 zu entnehmen. Das Frontend wurde in der ePille Elektronik qualifiziert und erprobt. Der voliegende Chip macht das Verfahren allgemein für induktive Datenübertragung im medizinischen Bereich nutzbar. Das Interface zum Prozessor ist eine Byte-serielle Handshake Übertragung und kann von jedem Prozessor leicht bedient werden. |

| Herstelldatum | 2010 |

| Kostenträger | MPC-Gruppe Baden-Württemberg |

Chip-Daten zum Download:

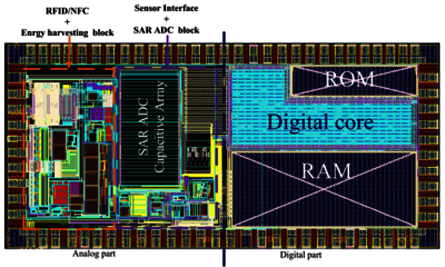

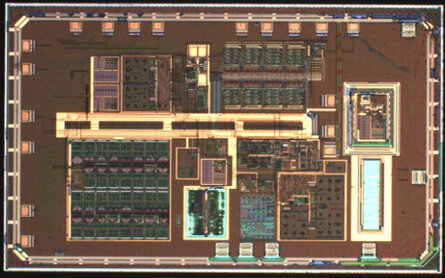

Mixed-Signal SoC for Biomedical Applications

Verantwortliche für den Entwurf:

Mayukh Bhattacharyya, Benjamin Dusch, Dirk Jansen

Hochschule Offenburg

Badstraße 24, 77652 Offenburg

| Entwurfsverfahren | Full Custom Design |

| Technologie | UMC CMOS 0,18 µm |

| Chipfläche | 1,52mm x 3,24 mm |

| Gehäuse | QFN64 |

| Funktionsblöcke | NFC-Interface, Energy Harvesting, SAR ADC, Sensor Interfaces, Sirius Microcontroller |

| Funktion | Bei dem Chip handelt es sich um einen RFID/NFC (ISO 15693standard) basierten, induktive versorgten SoC (system on chip) für biomedizinische Anwendungen. Der SoC enthält einen integrierten 32 bit Mikrocontroller inklusive Speicher, ein Sensor Interface für Spannungsgebend Sensoren mit einem SAR-AD-Umsetzer. Der Chip kann komplett passiv durch das Elektromagnetische Feld eines NFC-readers betrieben werden. |

| Herstelldatum | IV. Quartal 2015 |

| Kostenträger | MPC-Gruppe Baden-Württemberg |

| Veröffentlichung | Bhattacharyya, M.; Dusch, B.; Jansen, D.; Mackensen, E.: Design and Verification of a Mixed-Signal SoC for Biomedical Applications. In: Proceeding of the 54. MPC-Workshop. Ulm, Juli 2015. Pages 43-38. ISSN 1868-9221 |

|---|

Chip-Daten zum Download:

Testchip für ein Energy Harvesting IP in 0,18 µm CMOS-Technologie

Verantwortliche für den Entwurf:

Jens Rechtsteiner, Gerhard Forster

Hochschule Ulm

Institut für Kommunikationstechnik

Prittwitzstraße 10, 89075 Ulm

| Entwurfsverfahren | Full Custom Design |

| Technologie | UMC L180 Mixed-Mode/RF 180 nm CMOS 6M/1P 1.8V/3.3V |

| Chipfläche | 0,89 mm x 0,89 mm (Core 0,35 mm x 0,35 mm) |

| Gehäuse | QFN 24 |

| Funktionsblöcke | Sperrschwinger, Aktivgleichrichter, Bandgap-Referenz, Schaltregler, Linearregler, Logik. Extern wird ein Miniaturtransformator benötigt. |

| Funktion | Der Chip enthält den IP-Core einer Versorgungseinheit, die eine Versorgungsspannung von wahlweise 1,8 V oder 3,3 V zum Betrieb eines ASICs zur Verfügung stellt. Die Versorgungseinheit kommt ihrerseits mit einer Speisespannung von weniger als 100 mV aus. Wird dieser IP-Core in ein ASIC eingesetzt, so kann der Chip mit einer sehr geringen Versorgungsspannung betrieben werden, die sich z.B. mit Peltier-Elementen aus geringen Temperaturdifferenzen erzeugt lässt. Die Eigenstromaufnahme der Versorgungseinheit liegt bei 20 μA, der maximale Laststrom bei 1 mA. |

| Herstelldatum | III. Quartal 2012 |

| Kostenträger | MPC-Gruppe Baden-Württemberg |

| Veröffentlichung | Rechtsteiner, J; Forster, G.: Ein Energy Harvesting IP für den Einsatz in einem 0,18 μm CMOS ASIC. In: Workshop der Multiprojekt-Chip-Gruppe Baden-Württemberg, Offenburg, Tagungsband ISSN 1868-9221, S. 1 – 12, Ausgabe 47, Februar 2012. |

|---|

Chip-Daten zum Download:

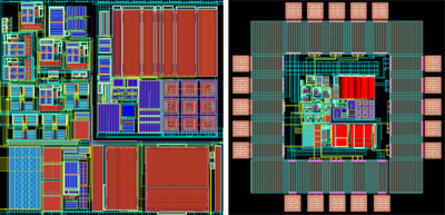

Testchip für ein Laser-Radar

Verantwortliche für den Entwurf:

Georg Vallant, Prof. Dipl.-Phys. Gerhard Forster

Hochschule Ulm

Institut für Kommunikationstechnik

Prittwitzstraße 10, 89075 Ulm

| Entwurfsverfahren | Mixed Signal-Entwurf Analogteil: Full Custom Design Digitalteil: Standardzellen-Entwurf |

| Technologie | C35B4C3 0,35 μm CMOS 4 Metal / 2 Poly / HR |

| Chipfläche | 2,15 mm x 1,70 mm |

| Gehäuse | QFN 48 |

| Funktionsblöcke | Analogteil:5 Transimpedanzverstärker, Komparatoren, 1 DPLL Digitalteil: 5 Zähler, Ausleselogik |

| Funktion | Mit dem Testchip sollten kritische Komponenten eines Laserradar-Empfängers untersucht werden. Der spätere Chip soll einmal 64 Empfangskanäle zur gleichzeitigen Laufzeitbestimmung eines reflektierten Laserpulses enthalten. Jeder Kanal besteht aus einem Transimpedanzverstärker (Transimpedanz 100 kΩ, Bandbreite 380 MHz), einem Komparator (Laufzeit 1,4 ns) und einem Zähler. Das System arbeitet mit einem internen Takt von 640 MHz, der mittels Frequenzsynthese gewonnen wird. Der Testchip enthält 4 Slices sowie einen Referenzkanal mit zusätzlichen Diagnoseanschlüssen. Er konnte bereits erfolgreich getestet werden. |

| Herstelldatum | III. Quartal 2008 |

| Kostenträger | MPC-Gruppe Baden-Württemberg |

Chip-Daten zum Download:

Ultra-Low-Power-Verstärker-ASIC mit Energy Harvesting

Verantwortliche für den Entwurf:

Benjamin Steiner, Gerhard Forster

Hochschule Ulm

Institut für Kommunikationstechnik

Prittwitzstraße 10, 89075 Ulm

| Entwurfsverfahren | Full Custom Design |

|---|---|

| Technologie | UMC L180 Mixed-Mode/RF 180 nm CMOS 6M/1P 1.8V/3.3V. |

| Chipfläche | 0,98 mm x 0,98 mm |

| Gehäuse | QFN 24 |

| Funktionsblöcke | Sperrschwinger, Aktivgleichrichter, Bandgap-Referenz, Schaltregler, Linearregler, Logik, Spannungsverdoppler, Ultra-Low-Power-Verstärker |

| Funktion | Der Chip enthält den IP-Core einer Versorgungseinheit, die eine Versorgungsspannung von wahlweise 1,8 V oder 3,3 V zum Betrieb eines ASICs zur Verfügung stellt. Die Versorgungseinheit kommt ihrerseits mit einer Speisespannung von weniger als 100 mV aus. Als Nutzlast befindet sich auf dem Chip ein Operationsverstärker mit zwei Differenzeingängen (Differential Difference Amplifier, DDA) zur Verstärkung von hochohmigen Differenzsignalen. Mit einer Stromaufnahme von 1 μA erreicht er eine Verstärkung von 70 dB und eine Transitfrequenz von 1 MHz. |

| Herstelldatum | II. Quartal 2014 |

| Kostenträger | MPC-Gruppe Baden-Württemberg |

| Veröffentlichung | J. Rechtsteiner, G. Forster, „Ein Energy Harvesting IP für den Einsatz in einem 0,18 μm CMOS ASIC“, Workshop der Multiprojekt-Chip-Gruppe Baden-Württemberg, Offenburg, Tagungsband ISSN 1868-9221, S. 1 – 12, Ausgabe 47, Februar 2012 |

Chip-Daten zum Download:

Ultra-Low-Power-Verstärker-ASIC mit Energy Harvesting

Verantwortliche für den Entwurf:

Lukas Schumm, Prof. Dipl.-Phys. Gerhard Forster

Hochschule Ulm

Institut für Kommunikationstechnik

Prittwitzstraße 10, 89075 Ulm

| Entwurfsverfahren | Full Custom Design |

|---|---|

| Technologie | AMS C35B4C3 0,35 μm CMOS 4M/2P/HR |

| Chipfläche | 1,19 mm x 1,00 mm |

| Gehäuse | DIL 16 |

| Funktionsblöcke | Rail-to-Rail-Operationsverstärker mit Versorgungseinheit |

| Funktion | Der Chip enthält den IP-Core eines CMOS-Operationsverstärkers, der sowohl am Ausgang als auch am Eingang bis an die Versorgungsspannung aussteuerbar ist. Bei der Versorgungsspannung 3,3 V erreicht die Endstufe eine Ausgangsspannung von 3,0 Vpp an 50 Ohm. Die Schleifenverstärkung beträgt 82 dB, die Transitfrequenz 10 MHz und die Offsetspannung liegt unter 2 mV. |

| Herstelldatum | IV. Quartal 2011 |

| Kostenträger | MPC-Gruppe Baden-Württemberg |

| Veröffentlichung | Schumm, L.; Forster, G.: Ein CMOS-Verstärker für niedrige Versorgungsspannungen. In: Workshop der Multiprojekt-Chip-Gruppe Baden-Württemberg, Furtwangen, Tagungsband ISSN 1868-9221, S. 7 – 15, Ausgabe 46, Juli 2011. |

Chip-Daten zum Download:

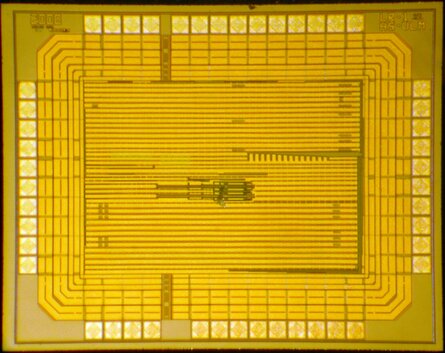

Hoch-Volt-Interface für 230 V-Netzbetrieb von ICs

Verantwortliche für den Entwurf:

Daniel Lutz, Bernhard Wicht

Robert Bosch Zentrum für Leistungselektronik

Alteburgstraße 150, 72762 Reutlingen

| Entwurfsverfahren | Full Custom Design |

|---|---|

| Technologie | 180 nm Hoch-Volt BiCMOS |

| Chipfläche | 3,88 mm x 2,19 mm |

| Gehäuse | CDIP 48 |

| Funktionsblöcke | Hoch-Volt-Interface für 230V Netzspannung, Gleichrichter, Zwischenkreisstabilisierung |

| Funktion | Bei diesem Chip handelt es sich um einen Testchip, welcher im vom BMBF geförderten Projekt „Hochintegrierte ACDC-Wandler als Kleinstnetzteil für direkten 230 V Netzbetreib von Integrierten Schaltungen“ (HAWIS) entwickelt wurde. Dieser Chip enthält Testschaltungen für ein Interface zur 230 V-Netzspannung. Die Netzspannung wird auf eine im Chip handhabbare Spannung gewandelt. Diese Spannung wird gleichgerichtet und mittels einer Zwischenkreisstabilisierung auf eine einstellbare Spannung (z.B. 40 V) stabilisiert. Diese stabilisierte Spannung steht auf dem Chip weiteren Funktionsblöcken zur Verfügung. |

| Herstelldatum | II. Quartal 2014 |

| Kostenträger | Industriepartner |

Chip-Daten zum Download:

Hocheffizienter resonanter Spannungswandler bis 30 V mit Maximumsdetektion < 1 ns Auflösung und 50 V High-Speed-Levelshifter

Verantwortliche für den Entwurf:

Tobias Funk, Jürgen Wittmann, Bernhard Wicht

Robert Bosch Zentrum für Leistungselektronik

Alteburgstraße 150, 72762 Reutlingen

| Entwurfsverfahren | Full Custom Design |

|---|---|

| Technologie | 180 nm Hoch-Volt BiCMOS |

| Chipfläche | 2.1 mm x 3.6 mm |

| Gehäuse | CSOIC 28 |

| Funktionsblöcke | Nullspannungsdetektion, Sample and Hold-Schaltung, Komparator, einstellbare Signalverzögerung, Spannungsregler, PWM-Generierung, Levelshifter, Gate-Treiber, Leistungsschalter. |

| Funktion | Um die Größe des passiven Ausgangsfilters zu reduzieren, soll ein Schaltwandler mit Taktfrequenzen > 10 MHz betrieben werden. Die entstehenden Schaltverluste werden durch Zero-Voltage-Switching (ZVS) minimiert. Dazu ist der Leistungsschalter um einen LC-Resonanzkreis erweitert. Der optimale Einschaltzeitpunkt für den Leistungsschalter ist das Maximum des oszillierenden Spannungsknotens. Hierzu werden zum einen der Hochpunkt des oszillierenden Spannungsknotens detektiert und zum anderen Signallaufzeiten von Levelshifter und Gate-Treiber kompensiert. Um mit dem Schaltwandler einen Eingangsspannungsbereich bis 30 V abdecken zu können, wird der Einschaltzeitpunkt mit einem LSB < 1 ns durch ein prädiktives Regelungsverfahren mithilfe einer Mixed-Signal-Auswertung nachgestellt. Dies ermöglicht den effizienten Betrieb von resonanten Spannungswandlern mit Schwingfrequenzen bis zu 50 MHz. |

| Herstelldatum | IV. Quartal 2013 |

| Kostenträger | Industriepartner |

| Veröffentlichung | J. Wittmann, Th. Rosahl, B. Wicht: A 50 V High-Speed Level Shifter with High dv/dt Immunity for Multi-MHz DCDC Converters. In ESSCIRC 2014, Proc. 40th European Solid-State Circuits Conference, Venice, Italy, p. 151 - 154, Sept. 22-26, 2014. T. Funk, J. Wittmann, T. Rosahl, B. Wicht, „A 20 V, 8 MHz Resonant DCDC Converter with Predictive Control for 1 ns Resolution Soft-Switching“, Circuits and Systems (ISCAS), 2015 IEEE International Symposium on, May 2015, in press. |

Chip-Daten zum Download: